The economics of monolithic die scaling drove USA semiconductor companies to pioneer chiplet disaggregation. AMD demonstrated commercial viability with its EPYC server processors starting in 2017, separating compute dies fabricated on leading edge process nodes from IO dies built on mature, cost effective nodes. This architectural choice delivered 64 core processors economically, while competitors remained constrained by reticle size limits and yield challenges on massive monolithic dies exceeding 800 square millimeters.

Intel recognized similar constraints and developed its tile approach, treating specialized chiplets as modular building blocks that optimize cost and performance across product lines. The company fabricates compute tiles on advanced nodes while leveraging mature processes for memory controllers and IO functions. This approach reduces total silicon cost by 30 to 40 percent compared with monolithic integration, while improving time to revenue through reuse of validated tiles across multiple processor families.

NVIDIA adopted chiplet architectures for its Blackwell GPU generation, splitting compute functions across dual dies connected through high density interconnects exceeding 10 terabytes per second bandwidth. This design enables scaling beyond single reticle limits while managing thermal density that would overwhelm monolithic implementations. Apple took a different approach with its M1 Ultra processor, connecting two complete system on chips through UltraFusion interconnect technology to create a unified 114 billion transistor processor with 2.5 terabytes per second die to die bandwidth.

Intel developed EMIB technology to connect chiplets without the cost and complexity of full silicon interposers. EMIB uses small embedded silicon bridges within the package substrate, delivering high density interconnects between adjacent dies with bump pitches reduced from 55 to 45 microns in second generation implementations. This localized bridge approach costs significantly less than interposer based solutions while providing sufficient bandwidth for logic to logic and logic to HBM connections.

Foveros builds on EMIB by enabling vertical die stacking through hybrid copper bonding with interconnect densities exceeding 10000 connections per square millimeter. Intel combines EMIB and Foveros in EMIB 3.5D architectures that create flexible heterogeneous systems mixing compute, memory, and IO tiles across both horizontal and vertical dimensions. The Data Center GPU Max Series integrates 47 active tiles across 5 process nodes using EMIB 3.5D, demonstrating the capability to build systems exceeding 100 billion transistors within a single package.

AMD pioneered 3D V Cache technology using TSMC hybrid bonding to stack additional cache memory directly atop compute dies. This approach delivers 96 megabytes of L3 cache per chiplet with through silicon via interconnects providing 2 terabytes per second bandwidth and interconnect density 200 times higher than 2D chiplet connections. The Milan X server processors achieve 768 megabytes total cache per socket, tripling cache capacity compared with conventional architectures and delivering 50 percent performance improvements in computational fluid dynamics and electronic design automation workloads.

Apple uses TSMC CoWoS S packaging to implement its UltraFusion interconnect, bonding two M1 Max dies on a silicon interposer exceeding 860 square millimeters. This configuration maintains cache coherency across 20 CPU cores and up to 64 GPU cores while providing 800 gigabytes per second memory bandwidth to unified memory pools reaching 128 gigabytes. The architecture demonstrates that 2.5D integration can deliver monolithic like performance when interconnect bandwidth and latency meet application requirements.

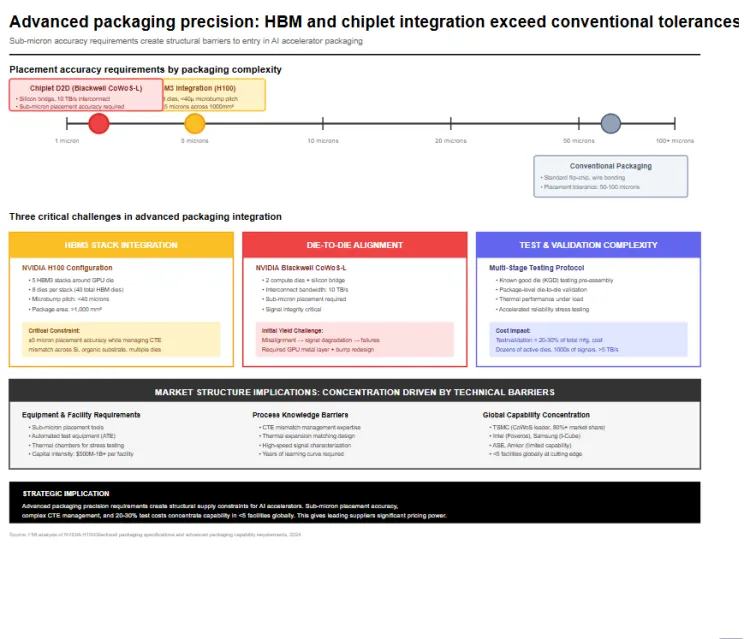

HBM integration demands process precision that exceeds conventional packaging tolerances by an order of magnitude. NVIDIA H100 integrates five HBM3 stacks surrounding a GPU die on a CoWoS S interposer, each stack containing eight dies bonded with microbump pitches under 40 microns. The assembly process must maintain placement accuracy within 5 microns across a package area exceeding 1000 square millimeters while managing coefficient of thermal expansion mismatches between silicon, organic substrate, and multiple die materials.

Die to die alignment for chiplet based GPU architectures presents even greater challenges. NVIDIA Blackwell uses CoWoS L packaging with local silicon interconnect bridges positioned between two compute dies that must maintain 10 terabytes per second interconnect bandwidth. Placement precision for these bridges requires sub micron accuracy, as any misalignment degrades signal integrity and causes system failures. The complexity led to initial yield challenges requiring redesign of GPU top metal layers and bump structures to improve thermal expansion matching.

Test and validation processes for advanced packages consume 20 to 30 percent of total manufacturing cost. Each chiplet requires known good die testing before assembly, followed by package level testing that validates die to die communication, thermal performance under operational loads, and long term reliability through accelerated stress testing. Only a handful of facilities globally possess the automated test equipment, thermal chambers, and process knowledge needed to characterize packages with dozens of active die and thousands of high speed signals operating at bandwidths exceeding 5 terabytes per second.

Silicon interposers for CoWoS packaging require fabrication processes similar to leading edge logic, with through silicon vias, redistribution layers, and microbump landing pads manufactured on 300 millimeter wafers. TSMC maintains the dominant position in interposer production, with monthly capacity approaching 50000 wafers dedicated to CoWoS S and expanding CoWoS L production. This concentration creates potential bottlenecks as NVIDIA, AMD, and other AI accelerator developers compete for limited packaging capacity.

Intel offers an alternative through its EMIB approach that eliminates full interposers in favor of substrate embedded bridges. This technology leverages advanced organic substrates with high density interconnect capabilities, reducing cost while maintaining adequate bandwidth for most applications. The company operates EMIB and Foveros packaging lines at its Rio Rancho New Mexico facility, providing USA based advanced packaging capacity that recently attracted interest from Apple, Qualcomm, and other design companies seeking alternatives to Asian concentrated packaging supply chains.

Organic substrates themselves represent a critical dependency. High performance packages require ABF substrates with fine line lithography capabilities approaching 2 microns line and space dimensions. Unimicron Technology emerged as Apple sole supplier for M1 Ultra substrates, reflecting the stringent quality and volume requirements that limit the supplier base. USA efforts to build domestic substrate capacity face challenges replicating the manufacturing expertise accumulated over decades in Taiwan, Japan, and South Korea.

Amkor Technology operates the largest USA based OSAT capability and announced a 2 billion dollar advanced packaging facility in Peoria Arizona scheduled for production by 2028. The facility will provide more than 500000 square feet of cleanroom space dedicated to advanced packaging and test services, partnering with TSMC to support chiplets fabricated at nearby Arizona fabs. Apple committed as the first and largest customer, ensuring sufficient demand to justify the investment in equipment and process development.

Intel maintains advanced packaging operations at multiple USA sites including Rio Rancho New Mexico and facilities in Arizona and Oregon. The company expanded EMIB capacity by 30 percent and Foveros capacity by 150 percent to address customer demand for alternatives to TSMC CoWoS packaging. Intel Foundry Services positions these capabilities as part of a comprehensive offering spanning process technology, advanced packaging, and test services, enabling end to end USA based manufacturing for customers prioritizing supply chain resilience.

The geographic concentration of front end fabs, packaging facilities, and equipment suppliers in Arizona creates an ecosystem effect that reduces logistics costs and enables tighter integration between design, fabrication, and packaging operations. Co location of TSMC, Intel, Amkor, Applied Materials, and ASML facilities supports rapid iteration cycles and accelerates qualification of new packaging technologies. This clustering replicates dynamics that made Taiwan dominant in semiconductor manufacturing while establishing similar capabilities on USA territory.

![]()

AMD chiplet architecture and 3D packaging

Intel advanced packaging technologies

NVIDIA HBM integration and CoWoS packaging

Apple UltraFusion and M series processors

USA advanced packaging facilities and capabilities

Industry analysis and supply chain trends

Advanced packaging enables performance scaling that monolithic die cannot achieve, justifying costs 3 to 5 times higher than conventional packaging. Chiplet architectures reduce total silicon costs through better yields and process optimization while delivering bandwidth and compute density impossible with traditional approaches. The economic return from improved processor performance exceeds incremental packaging costs.

Initial process qualification requires 12 to 18 months including design rule development, test vehicle fabrication, reliability testing across temperature and voltage ranges, and yield ramp to production targets. Established facilities with demonstrated process control can compress timelines to 9 to 12 months for evolutionary packaging technologies building on validated baseline processes.

Advanced packaging delivers die to die bandwidth exceeding 1 terabyte per second through microbump or hybrid bond interconnects with pitches under 50 microns. Conventional packaging typically provides less than 100 gigabytes per second bandwidth through coarser pitch bumps or wire bonds. Power delivery, thermal management, and interconnect density requirements separate advanced from conventional approaches.

Taiwan and South Korea dominate high volume advanced packaging through TSMC, Samsung, and OSAT providers like ASE Technology. However, USA facilities offer supply chain diversity, shorter qualification cycles for USA based customers, and CHIPS Act supported capacity expansion. Technology capabilities remain comparable, with differentiation based on customer relationships and geographic preferences rather than pure technical performance.

Universal Chiplet Interconnect Express provides standardized physical and protocol layers enabling multi vendor chiplet ecosystems. UCIe 2.0 adds 3D packaging support with hybrid bonding at bump pitches from 1 to 25 microns. Standards reduce custom engineering costs and enable broader supplier participation, but leading edge implementations still require close collaboration between chiplet designers and packaging providers to optimize performance and yield.

The GMO Testing Services Market is segmented by Technology (Polymerase Chain Reaction, ELISA Test, Lateral Flow Devices), Crop Type (Soy, Corn, Rapeseed/Canola, Potato, Tomato, Other Crops), and Region. Forecast for 2026 to 2036.

GMP Testing Services Market

Food Testing Services Market Size, Growth, and Forecast for 2025–2035

Examining Food Testing Services Market Share & Industry Outlook

Seed Testing Services Market Growth – Trends & Forecast 2018-2028