Wafer Batch Aligner Market

Wafer Batch Aligner Market Size and Share Forecast Outlook 2025 to 2035

Historical Data Covered: 2015 to 2023 | Base Year: 2024 | Estimated Year: 2025 | Forecast Period: 2026 to 2035

Wafer Batch Aligner Market Forecast and Outlook (2025-2035)

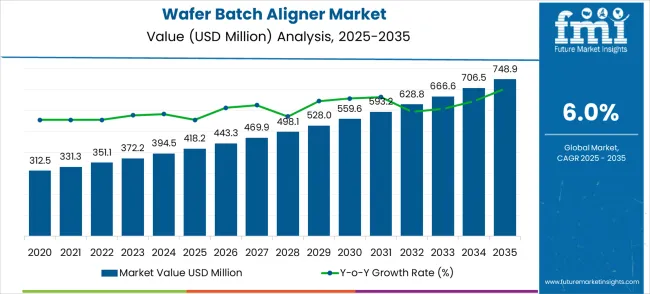

The wafer batch aligner industry stands at the threshold of a decade-long expansion trajectory that promises to reshape semiconductor manufacturing and precision alignment technology. The market's journey from USD 418.2 million in 2025 to USD 748.9 million by 2035 represents substantial growth, demonstrating the accelerating adoption of advanced semiconductor fabrication equipment and automated alignment systems across electronics manufacturing, automotive semiconductors, and advanced chip production sectors.

The first half of the decade (2025-2030) will see the market increase from USD 418.2 million to approximately USD 550.8 million, adding USD 132.6 million in value, which constitutes 40% of the total forecasted growth period. This phase will be characterized by the rapid adoption of automated wafer batch aligner systems, driven by increasing demand for semiconductors and modernization programs in the global manufacturing sector. Advanced precision capabilities and automated handling features will become standard expectations rather than premium options.

The latter half (2030-2035) will witness sustained growth from USD 550.8 million to USD 748.9 million, representing an addition of USD 198.1 million or 60% of the decade's expansion. This period will be defined by mass market penetration of next-generation alignment systems, integration with comprehensive semiconductor manufacturing platforms, and seamless compatibility with existing fab infrastructure. The market trajectory signals fundamental shifts in how semiconductor manufacturers approach wafer processing and batch handling, with participants positioned to benefit from sustained demand across multiple application segments.

Quick Stats for Wafer Batch Aligner Market

- Wafer Batch Aligner Market Value (2025): USD 418.2 million

- Wafer Batch Aligner Market Forecast Value (2035): USD 748.9 million

- Wafer Batch Aligner Market Forecast CAGR: 6.0%

- Leading Operation Mode in Wafer Batch Aligner Market: Automated Type

- Key Growth Regions in Wafer Batch Aligner Market: Asia Pacific, North America, and Europe

- Top Key Players in Wafer Batch Aligner Market: Emu Technologies, SPS-International, GL Automation, H-Square, G2 Automated Technologies

- Wafer Batch Aligner Market Year-over-Year Forecast (2025-2035)

The Wafer Batch Aligner market demonstrates distinct growth phases with varying market characteristics and competitive dynamics. Between 2025 and 2030, the market progresses through its technology adoption phase, expanding from USD 418.2 million to USD 550.8 million with steady annual increments averaging 5.7% growth. This period showcases the transition from basic manual alignment systems to advanced automated platforms with enhanced precision capabilities and integrated process control systems becoming mainstream features.

The 2025-2030 phase adds USD 132.6 million to market value, representing 40% of total decade expansion. Market maturation factors include standardization of automation protocols, declining component costs for precision alignment systems, and increasing semiconductor manufacturer awareness of automated batch processing benefits reaching 90-95% efficiency improvements in wafer handling applications. Competitive landscape evolution during this period features established semiconductor equipment manufacturers like Emu Technologies and SPS-International expanding their wafer batch aligner portfolios while new entrants focus on compact designs and enhanced throughput capabilities.

From 2030 to 2035, market dynamics shift toward advanced integration and multi-platform deployment, with growth accelerating from USD 550.8 million to USD 748.9 million, adding USD 198.1 million or 60% of total expansion. This phase transition logic centers on next-generation automated systems, integration with Industry 4.0 manufacturing networks, and deployment across diverse semiconductor fabrication scenarios, becoming standard rather than specialized applications. The competitive environment matures with focus shifting from basic alignment capability to comprehensive wafer handling systems and integration with fab-wide automation and process control platforms.

Wafer Batch Aligner Market Key Takeaways

| Metric | Value |

|---|---|

| $ Market Value (2025) → | USD 418.2 million |

| $ Market Forecast (2035) ↑ | USD 748.9 million |

| # Growth Rate ★ | 6.0% CAGR |

| Leading Technology → | Automated Type |

| Primary Application → | Wafer Segment |

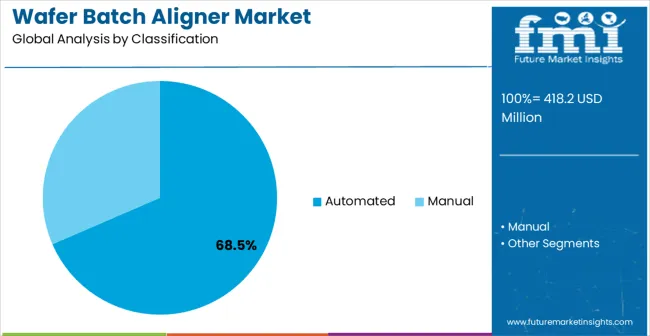

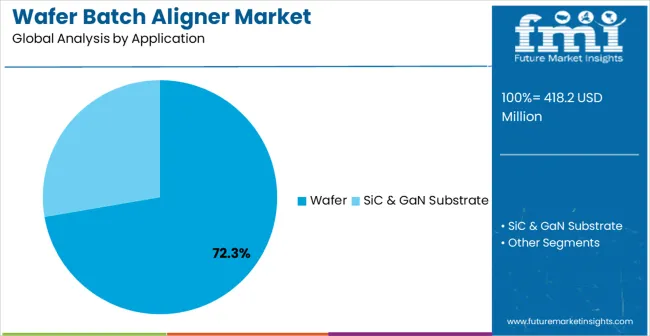

The market demonstrates strong fundamentals with automated operation mode systems capturing a dominant 68.5% share through advanced precision and high-throughput batch processing capabilities. Wafer applications drive primary demand with 72.3% market share, supported by increasing semiconductor production and advanced chip manufacturing requirements. Geographic expansion remains concentrated in developed markets with established semiconductor infrastructure, while emerging economies show accelerating adoption rates driven by electronics manufacturing growth and rising fab investments.

Why is the Wafer Batch Aligner Market Growing?

Market expansion rests on three fundamental shifts driving adoption across semiconductor and electronics manufacturing sectors.

- Automation demand creates compelling operational advantages through wafer batch aligner systems that provide precise wafer positioning with consistent repeatability, enabling manufacturers to achieve higher yields while maintaining quality standards and reducing manual handling risks.

- Semiconductor manufacturing modernization accelerates as fab facilities worldwide seek advanced automation equipment that complements existing process tools, enabling efficient batch processing and substrate handling applications that align with Industry 4.0 requirements and smart manufacturing protocols.

- Manufacturing infrastructure enhancement drives adoption from electronics companies and semiconductor foundries requiring effective wafer handling solutions that maximize throughput while maintaining contamination control during advanced chip production and packaging operations.

However, growth faces headwinds from technical complexity challenges that vary across different substrate types and processing requirements, which may limit operational flexibility in certain manufacturing environments. Cost considerations also persist regarding initial capital investment and integration expenses that may reduce system adoption rates in price-sensitive market segments that prioritize immediate cost savings over long-term automation benefits.

Opportunity Pathways - Wafer Batch Aligner Market

The wafer batch aligner market presents significant growth opportunities as global semiconductor manufacturing paradigms shift toward automated precision alignment solutions and Industry 4.0 integration accelerates worldwide. With the market projected to expand from USD 418.2 million in 2025 to USD 748.9 million by 2035 at a 6.0% CAGR, semiconductor equipment manufacturers and technology providers are positioned to capitalize on structural demand from chip fabrication facilities, electronics manufacturers, and research institutions requiring precise wafer handling and alignment capabilities.

The convergence of semiconductor manufacturing modernization programs, increasing chip complexity requirements, and automation emphasis on precision processing creates sustained market expansion opportunities. Geographic growth differentials are particularly pronounced in China (8.1% CAGR) and India (7.5% CAGR), where rapid semiconductor development and manufacturing infrastructure investments drive substantial demand. Technology advancement pathways around automation, precision enhancement, and process integration offer differentiation opportunities, while specialized applications across wafer processing, compound semiconductor manufacturing, and research facilities provide diverse revenue streams.

Automated system dominance and wafer application leadership indicate established foundations for strategic expansion, while SiC & GaN substrate applications represent emerging growth vectors. Semiconductor manufacturing investments globally support sustained procurement, while advanced packaging and specialty substrate requirements drive operational deployment.

- Pathway A - Semiconductor Manufacturing Automation & Fab Modernization. Global semiconductor fabs increasingly adopt automated wafer batch aligners as standard precision handling systems for advanced node processing, packaging operations, and specialty substrate manufacturing. Fab modernization programs mandate integration with existing process equipment, creating sustained procurement cycles. Companies developing fab-grade solutions with industry compatibility and cleanroom designs capture premium contracts. Expected revenue pool: USD 180-280 million.

- Pathway B - Geographic Expansion in High-Growth Markets. China's 8.1% CAGR and India's 7.5% growth present substantial opportunities through local manufacturing partnerships, technology transfer, and domestic semiconductor facility modernization. Regional expansion strategies capturing Asia-Pacific semiconductor buildup and electronics manufacturing requirements offer volume growth and market share gains. Revenue opportunity: USD 150-240 million.

- Pathway C - Technology Integration & Smart Manufacturing Systems. Integration with Industry 4.0 networks, process control systems, and automated material handling transforms basic wafer batch aligners into comprehensive fab automation solutions. Advanced features, including precision metrology, environmental monitoring, and multi-platform compatibility, enable premium positioning and recurring service revenue. Expected pool: USD 100-180 million.

- Pathway D - Advanced Substrate & Specialty Applications. Expanding beyond silicon wafers toward SiC & GaN substrate processing offers enhanced precision requirements, specialized handling capabilities, and integration with compound semiconductor manufacturing platforms. Development of specialized alignment systems, contamination control, and advanced substrate compatibility captures growing demand for power electronics and RF applications. Revenue potential: USD 90-150 million.

- Pathway E - Research & Development Facility Applications. Growing adoption by university research centers, government labs, and R&D facilities for prototype development, advanced material research, and next-generation semiconductor technology development. Specialized products meeting research deployment requirements, including flexible configurations and multi-substrate compatibility, expand the market beyond production applications. Pool: USD 70-120 million.

- Pathway F - Service Excellence & Support Programs. Comprehensive service offerings, including installation support, maintenance programs, and technical training, create recurring revenue streams while strengthening customer relationships. Digital service platforms enabling remote diagnostics and predictive maintenance support global deployment scaling. Expected opportunity: USD 60-100 million.

- Pathway G - Standards Compliance & Quality Certification. Developing solutions meeting diverse international standards around semiconductor equipment safety, cleanroom compatibility, and process control enables global market penetration. Certification programs and standards development leadership create competitive advantages in regulated semiconductor environments. Revenue pool: USD 50-90 million.

Segmental Analysis

Primary Market Structure: The market segments by operation mode into Automated and Manual categories, representing the evolution from traditional operator-dependent systems to advanced automated platforms for comprehensive precision handling and batch processing efficiency.

Secondary Breakdown: Application segmentation divides the market into Wafer and SiC & GaN Substrate sectors, reflecting distinct requirements for conventional silicon processing, compound semiconductor manufacturing, and specialty substrate handling applications.

Regional Distribution: Geographic classification covers Asia Pacific, North America, Europe, Latin America, and the Middle East & Africa, with established semiconductor manufacturing regions leading adoption while emerging economies show accelerating growth patterns driven by electronics manufacturing development programs.

The segmentation structure reveals technology progression from manual alignment systems toward fully automated platforms with enhanced precision and throughput capabilities, while application diversity spans from traditional silicon wafer processing to emerging compound semiconductor manufacturing requiring specialized handling solutions for advanced material properties.

By Operation Mode, the Automated Segment Accounts for Dominant Market Share

Market Position: Automated operation mode systems command the leading position in the wafer batch aligner market with 68.5% market share through advanced precision features, including robotic handling capabilities, computer-controlled positioning, and integrated process monitoring that enable semiconductor manufacturers to achieve consistent alignment accuracy across high-volume batch processing operations.

Value Drivers: The segment benefits from semiconductor industry preference for automated systems that provide superior repeatability and contamination control without requiring skilled operator intervention for each alignment cycle. Automated design features enable deployment in cleanroom environments, high-throughput manufacturing, and 24/7 production operations where consistency and reliability represent critical operational requirements for advanced chip manufacturing and substrate processing applications.

Competitive Advantages: Automated systems differentiate through intelligent control algorithms, adaptive positioning capabilities, and integration with fab-wide automation networks that enhance manufacturing efficiency while maintaining precision tolerances suitable for sub-micron semiconductor processing requirements and advanced packaging operations.

Key market characteristics:

- Advanced robotics integration with precision servo control and sub-micron positioning accuracy capabilities

- Process monitoring systems enabling real-time alignment verification and quality control documentation

- Cleanroom compatibility features, including contamination control and particle generation minimization for semiconductor environments

The Manual operation mode segment maintains 31.5% market share, primarily serving research applications, low-volume production, and specialized processing requirements where operational flexibility and cost considerations outweigh automation benefits in specific manufacturing scenarios.

By Application, the Wafer Segment Accounts for the Largest Market Share

Market Context: Wafer applications dominate the wafer batch aligner market with 72.3% market share due to widespread silicon semiconductor manufacturing and increasing focus on advanced chip production, packaging operations, and substrate processing applications that require precise alignment control for maintaining device performance and manufacturing yield optimization.

Appeal Factors: Wafer processing customers prioritize alignment accuracy, throughput optimization, and integration with existing semiconductor fabrication equipment that enables coordinated processing across multiple manufacturing stages. The segment benefits from substantial semiconductor industry investments and technology advancement programs that emphasize automated handling solutions for conventional silicon wafer processing in logic, memory, and mixed-signal device manufacturing applications.

Growth Drivers: Semiconductor industry expansion incorporates wafer batch aligners as essential equipment for advanced node processing and packaging operations, while increasing chip complexity and miniaturization drive demand for precision alignment capabilities that maintain device specifications and manufacturing quality standards. Advanced packaging trends, including 3D integration and system-in-package solutions, create additional alignment requirements for specialized wafer handling and substrate preparation processes.

Market Challenges: Substrate handling complexity and diverse wafer specifications may require customized alignment solutions that increase system costs and reduce standardization benefits across different semiconductor manufacturing applications and process requirements.

Application dynamics include:

- Strong growth in advanced packaging and 3D integration applications requiring specialized alignment capabilities for complex wafer configurations

- Increasing adoption in research and development facilities for prototype processing and next-generation semiconductor technology development

- Rising integration with automated material handling systems for comprehensive fab automation and process optimization

The SiC & GaN Substrate segment holds 27.7% market share, representing emerging opportunities in compound semiconductor manufacturing for power electronics, RF applications, and specialty device production where unique material properties require specialized alignment solutions and handling protocols.

What are the Drivers, Restraints, and Key Trends of the Wafer Batch Aligner Market?

Growth Accelerators: Semiconductor manufacturing modernization drives primary adoption as wafer batch aligner systems provide automated precision positioning that enables consistent wafer handling with sub-micron accuracy, supporting advanced node processing and compound semiconductor manufacturing that require precise alignment tolerances. Manufacturing automation demand accelerates market expansion as semiconductor fabs seek efficient batch processing tools that minimize human intervention while maintaining contamination control and yield optimization during critical wafer handling operations and substrate preparation processes. Electronics industry growth creates sustained demand for automated handling equipment that complements advanced manufacturing systems and provides operational flexibility in complex fab environments where precision and repeatability represent critical manufacturing requirements.

Industry 4.0 integration trends further amplify adoption as manufacturers implement smart factory concepts requiring automated equipment with process monitoring capabilities, real-time data collection, and integration with manufacturing execution systems that optimize production workflow and enable predictive maintenance scheduling. Advanced packaging requirements drive specialized alignment system demand as semiconductor manufacturers adopt new packaging technologies including 3D integration, system-in-package solutions, and heterogeneous integration approaches that necessitate precise wafer positioning and substrate handling capabilities beyond traditional applications.

Compound semiconductor market expansion, particularly in SiC and GaN substrate processing, creates specialized alignment requirements due to unique material properties and processing challenges that demand customized handling solutions with enhanced precision control and contamination prevention features. Research and development activity acceleration in semiconductor technology drives demand for flexible alignment systems capable of handling diverse substrate types and experimental processing requirements that support next-generation chip development and advanced material research applications.

Growth Inhibitors: Capital investment barriers persist as wafer batch aligner systems require substantial initial investment costs ranging from hundreds of thousands to millions of dollars per unit, which may limit adoption among smaller semiconductor manufacturers and research facilities operating under constrained budgets or uncertain return on investment scenarios. Technical complexity challenges create integration difficulties when incorporating new alignment systems into existing fab infrastructure, particularly in older facilities where legacy equipment compatibility and process modification requirements can result in extended implementation timelines and additional engineering costs.

Substrate compatibility limitations affect market penetration as specialized substrates including compound semiconductors, advanced packaging materials, and experimental wafers may require customized alignment solutions that increase system costs and reduce standardization benefits. Market fragmentation across diverse semiconductor applications creates compatibility concerns between different alignment system manufacturers and existing process equipment, potentially limiting supplier selection and increasing procurement complexity for fab operators managing multiple equipment vendor relationships.

Supply chain vulnerabilities in precision components and advanced automation systems can impact delivery schedules and system availability, particularly during periods of high semiconductor equipment demand when component shortages and extended lead times affect customer deployment plans and facility expansion timelines.

Market Evolution Patterns: Technology adoption accelerates in advanced semiconductor manufacturing facilities where precision alignment justifies system costs, with geographic concentration in major semiconductor regions transitioning toward mainstream adoption in emerging manufacturing hubs driven by electronics production growth and fab establishment programs. Automation sophistication increases as alignment systems incorporate artificial intelligence, machine learning algorithms, and advanced sensor technologies that enhance precision control and enable adaptive processing capabilities for diverse substrate handling requirements.

Market consolidation trends emerge as larger semiconductor equipment manufacturers acquire specialized alignment system companies to expand technology portfolios and provide comprehensive automation solutions that address complete wafer handling workflows. The market could face disruption if alternative alignment technologies or revolutionary substrate handling approaches significantly change semiconductor manufacturing processes or eliminate traditional batch processing requirements in advanced chip production environments.

Analysis of the Wafer Batch Aligner Market by Key Country

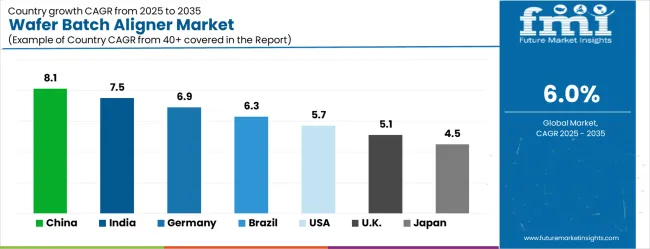

The wafer batch aligner market demonstrates varied regional dynamics with Growth Leaders including China (8.1% CAGR) and India (7.5% CAGR) driving expansion through semiconductor manufacturing development and electronics production infrastructure growth. Steady Performers encompass Germany (6.9% CAGR), Brazil (6.3% CAGR), and the U.S. (5.7% CAGR), benefiting from established semiconductor industries and advanced manufacturing technology adoption. Mature Markets feature the U.K. (5.1% CAGR) and Japan (4.5% CAGR), where specialized semiconductor applications and precision manufacturing integration support consistent growth patterns.

| Country | CAGR (2025-2035) |

|---|---|

| China | 8.1% |

| India | 7.5% |

| Germany | 6.9% |

| Brazil | 6.3% |

| U.S. | 5.7% |

| U.K. | 5.1% |

| Japan | 4.5% |

Regional synthesis reveals Asia-Pacific markets leading growth through semiconductor manufacturing expansion and electronics production infrastructure development, while European countries maintain steady expansion supported by advanced manufacturing technology and research facility investments. North American markets show moderate growth driven by semiconductor innovation and advanced packaging applications.

The report covers an in-depth analysis of 40+ countries; seven top-performing countries are highlighted below.

China Drives Global Market Leadership

China establishes market leadership through aggressive semiconductor manufacturing development programs and comprehensive electronics production infrastructure expansion, integrating advanced wafer batch aligner systems as standard components in fab automation and precision substrate handling applications. The country's 8.1% CAGR through 2035 reflects government initiatives promoting domestic semiconductor capability and electronics manufacturing competitiveness that mandate automated handling systems in manufacturing facilities and research installations. Growth concentrates in major semiconductor clusters, including Shanghai, Shenzhen, and Beijing, where technology development showcases integrated wafer batch aligner systems that appeal to domestic manufacturers seeking automated precision handling capabilities and advanced packaging applications.

Chinese manufacturers are developing cost-effective wafer batch aligner solutions that combine domestic production advantages with advanced automation features, including precision positioning systems and integrated process control capabilities. Distribution channels through state electronics programs and manufacturing equipment suppliers expand market access, while government funding for semiconductor technology development supports adoption across diverse manufacturing and research segments.

Strategic Market Indicators:

- Semiconductor fabs leading adoption with 70% automation rate in wafer handling operations

- Government electronics programs providing substantial funding for domestic equipment development and technology advancement

- Local manufacturers capturing 60% market share through competitive pricing and localized technical support services

- Research institutions segment growth driven by university requirements for precision substrate handling and experimental processing systems

- Export market development for cost-effective wafer batch aligner solutions targeting emerging semiconductor manufacturing regions

India Emerges as High-Growth Market

In Bangalore, Chennai, and Hyderabad, semiconductor facilities and electronics manufacturers are implementing advanced wafer batch aligner systems as standard equipment for precision handling operations and substrate processing applications, driven by increasing electronics production and government programs that emphasize manufacturing competitiveness and technology advancement capabilities. The market is projected to demonstrate a 7.5% CAGR through 2035, supported by government electronics manufacturing initiatives and semiconductor development programs that promote automated handling equipment for domestic facilities and international partnership projects. Indian electronics companies are adopting wafer batch aligner systems that provide efficient substrate processing capabilities and automated handling features, particularly appealing in technology centers where precision manufacturing represents critical operational requirements for export competitiveness.

Market expansion benefits from growing electronics manufacturing capabilities and international technology partnerships that enable domestic production of advanced handling systems for semiconductor and electronics applications. Technology adoption follows patterns established in manufacturing automation, where precision control and reliability drive procurement decisions and operational deployment strategies.

Market Intelligence Brief:

- Electronics and semiconductor segments driving initial adoption with 40% annual growth in automated equipment procurement

- Government manufacturing programs emphasizing precision handling equipment for electronics production competitiveness and export capabilities

- Local equipment manufacturers partnering with international technology providers for advanced system development and technology transfer programs

- Research facilities implementing wafer batch aligners for materials research and semiconductor technology development applications

Germany Maintains Technology Leadership

Germany's advanced manufacturing technology market demonstrates sophisticated wafer batch aligner deployment with documented operational effectiveness in semiconductor research facilities and precision manufacturing applications through integration with existing automation systems and quality control infrastructure. The country leverages engineering expertise in precision machinery and automation systems integration to maintain a 6.9% CAGR through 2035. Technology centers, including Dresden, Munich, and Stuttgart, showcase premium installations where wafer batch aligners integrate with comprehensive manufacturing platforms and research equipment to optimize substrate handling effectiveness and process precision capabilities.

German equipment manufacturers prioritize system precision and industry compatibility in wafer batch aligner development, creating demand for premium systems with advanced features, including environmental control and integration with research facility infrastructure. The market benefits from established manufacturing technology leadership and willingness to invest in advanced automation technologies that provide long-term operational benefits and support research excellence requirements.

Market Intelligence Brief:

- Engineering focuses on precision standards and system integration, driving premium segment growth and technology advancement programs

- Equipment manufacturer partnerships providing 35% faster technology development cycles and collaborative research programs

- Technology collaboration between German automation companies and international semiconductor equipment manufacturers

- Research facilities expanding wafer batch aligner integration in materials science and semiconductor development applications

Brazil Shows Strong Regional Leadership

Brazil's market expansion benefits from diverse electronics manufacturing demand, including semiconductor assembly in São Paulo and Campinas, technology development equipment upgrades, and government electronics programs that increasingly incorporate automated handling solutions for manufacturing competitiveness applications. The country maintains a 6.3% CAGR through 2035, driven by rising electronics production and increasing awareness of wafer batch aligner technology benefits, including automated processing and quality improvement capabilities for domestic manufacturing operations.

Market dynamics focus on cost-effective wafer batch aligner solutions that balance advanced handling features with affordability considerations important to Brazilian electronics manufacturers. Growing technology sector development creates sustained demand for precision handling systems in manufacturing infrastructure and research facility modernization projects.

Strategic Market Considerations:

- Electronics manufacturing and research segments leading growth with focus on automated handling and precision processing applications

- Regional manufacturing requirements driving diverse product portfolio from basic handling systems to advanced automated platforms

- Import dependency challenges offset by potential local assembly partnerships with international manufacturers and technology transfer programs

- Government electronics initiatives beginning to influence procurement standards and operational requirements for domestic manufacturing competitiveness

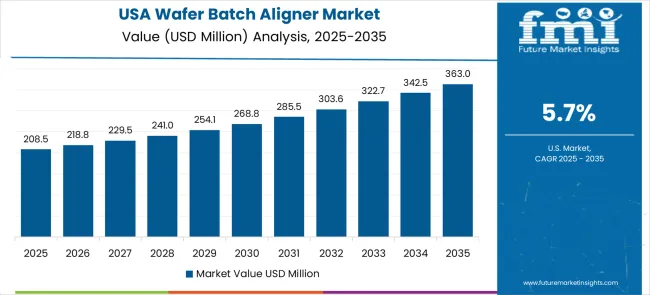

United States Demonstrates Technology Innovation

The U.S. market emphasizes advanced wafer batch aligner features, including precision automation systems and integration with comprehensive semiconductor manufacturing platforms that manage substrate handling, process control, and quality assurance applications through unified automation systems. The country is projected to show a 5.7% CAGR through 2035, driven by semiconductor industry modernization under manufacturing equipment upgrades and research facility demand for reliable automated handling systems with advanced positioning capabilities. American semiconductor manufacturers prioritize operational effectiveness with wafer batch aligners delivering consistent substrate positioning through advanced control algorithms and environmental adaptation capabilities for diverse processing requirements.

Technology deployment channels include major semiconductor equipment suppliers, specialized automation system providers, and research facility procurement programs that support professional installation for complex manufacturing applications. Semiconductor industry integration capabilities with established manufacturing systems expand market appeal across diverse operational requirements seeking precision and reliability benefits in advanced chip production environments.

Performance Metrics:

- Semiconductor facilities in California, Texas, and New York leading wafer batch aligner adoption for advanced manufacturing and research applications

- Equipment supplier networks maintaining 75% market share for complex semiconductor integration applications and specialized processing requirements

- Research institution procurement programs supporting 25% of wafer batch aligner acquisitions across university facilities and government research centers

- Manufacturing platform compatibility with major semiconductor processing systems driving procurement selection criteria and technology adoption patterns

United Kingdom Drives Advanced Research Integration

In Cambridge, Edinburgh, and other research centers, British semiconductor research facilities and electronics manufacturers are implementing advanced wafer batch aligner systems to enhance precision handling capabilities and support compound semiconductor development that aligns with advanced materials research requirements and specialized processing protocols. The U.K. market demonstrates sustained growth with a 5.1% CAGR through 2035, driven by research facility modernization programs and technology development initiatives that emphasize advanced handling equipment for semiconductor research and specialty electronics manufacturing applications. British research institutions prioritize wafer batch aligner systems that provide precise substrate positioning capabilities while maintaining compatibility with existing research equipment and enabling diverse material handling requirements, particularly important in compound semiconductor research and advanced materials development projects.

Market expansion benefits from government research funding programs that mandate advanced handling capabilities in research equipment specifications, creating sustained demand across the U.K.'s research and development sectors where operational precision and material compatibility represent critical requirements. The regulatory framework supports wafer batch aligner adoption through research facility standards and international collaboration requirements that promote advanced handling systems aligned with global research capabilities.

Strategic Market Indicators:

- Research institutions and specialty manufacturers leading adoption with technology development programs requiring precision substrate handling systems

- Government research funding providing regulatory support for advanced equipment acquisition and research facility modernization programs

- International collaboration requirements driving demand for standardized systems with global research facility compatibility

- Compound semiconductor research segments adopting comprehensive wafer batch aligner solutions for specialized materials handling and processing applications

Japan Emphasizes Precision and Integration Excellence

Japan demonstrates steady market development with a 4.5% CAGR through 2035, distinguished by semiconductor manufacturers' preference for high-precision wafer batch aligners that integrate seamlessly with existing manufacturing systems and provide reliable long-term operation in specialized processing applications. The market prioritizes advanced features, including precision positioning, environmental control, and integration with comprehensive manufacturing platforms that reflect Japanese manufacturing expectations for technological sophistication and operational excellence in semiconductor production environments.

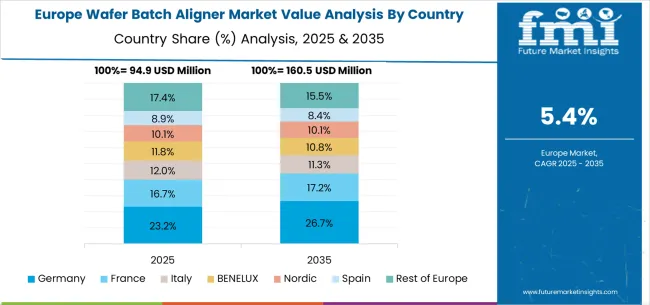

Europe Market Split by Country

The European Wafer Batch Aligner market is projected to grow from USD 89.2 million in 2025 to USD 142.6 million by 2035, registering a CAGR of 4.8% over the forecast period. Germany is expected to maintain its leadership position with a 31.2% market share in 2025, declining slightly to 30.8% by 2035, supported by its advanced semiconductor manufacturing infrastructure and major research centers, including Dresden and Munich technology clusters.

France follows with a 22.4% share in 2025, projected to reach 22.8% by 2035, driven by comprehensive electronics manufacturing programs and semiconductor technology development initiatives. The United Kingdom holds a 18.6% share in 2025, expected to maintain 18.3% by 2035 through specialized semiconductor research applications and compound semiconductor development programs. Italy commands a 12.8% share, while Spain accounts for 8.7% in 2025. The Rest of Europe region is anticipated to gain momentum, expanding its collective share from 6.3% to 6.8% by 2035, attributed to increasing wafer batch aligner adoption in Nordic countries and emerging Eastern European semiconductor facilities implementing manufacturing modernization programs.

Competitive Landscape of the Wafer Batch Aligner Market

The wafer batch aligner market operates with moderate concentration, featuring approximately 15-18 meaningful participants, where leading companies control roughly 50-55% of the global market share through established semiconductor equipment industry relationships and comprehensive technology portfolios. Competition emphasizes precision capabilities, automation sophistication, and manufacturing platform integration rather than price-based rivalry in the premium segment.

Market Leaders encompass Emu Technologies, SPS-International, and GL Automation, which maintain competitive advantages through extensive semiconductor manufacturing expertise, global equipment supplier networks, and comprehensive system integration capabilities that create customer switching costs and support premium positioning. These companies leverage decades of precision automation experience and ongoing research investments to develop advanced wafer batch aligner systems with sub-micron accuracy and cleanroom compatibility features.

Technology Innovators include H-Square, G2 Automated Technologies, and Chung King Enterprise, which compete through specialized automation technology focus and innovative precision interfaces that appeal to semiconductor customers seeking advanced accuracy capabilities and manufacturing flexibility. These companies differentiate through rapid technology development cycles and specialized semiconductor application expertise focused on next-generation processing requirements.

Regional Specialists feature companies like Dou Yee Enterprises, Honwe Precision, and Shen-Yueh Technology, which focus on specific geographic markets and specialized applications, including compound substrate handling and research facility solutions. Market dynamics favor participants that combine reliable hardware with advanced automation software, including process monitoring and predictive maintenance capabilities. Competitive pressure intensifies as traditional semiconductor equipment manufacturers expand into wafer handling systems, while specialized automation companies challenge established players through innovative precision solutions and cost-effective platforms targeting emerging semiconductor manufacturing segments.

Key Players in the Wafer Batch Aligner Market

- Emu Technologies

- SPS-International

- GL Automation

- H-Square

- G2 Automated Technologies

- Chung King Enterprise

- Dou Yee Enterprises

- Honwe Precision

- Shen-Yueh Technology

- Standard Technology

- Chain-Logic International (MPI Corporation)

- Suzhou SOSCH Microelectronics

Scope of the Report

| Item | Value |

|---|---|

| Quantitative Units | USD 418.2 ,illion |

| Operation Mode | Automated, Manual |

| Application | Wafer, SiC & GaN Substrate |

| Regions Covered | Asia Pacific, North America, Europe, Latin America, Middle East & Africa |

| Countries Covered | China, India, Germany, Brazil, the U.S., the U.K., Japan, and 25+ additional countries |

| Key Companies Profiled | Emu Technologies, SPS-International, GL Automation, H-Square, G2 Automated Technologies, Chung King Enterprise |

| Additional Attributes | Dollar sales by operation mode and application categories, regional adoption trends across Asia Pacific, North America, and Europe, competitive landscape with semiconductor equipment manufacturers and automation providers, customer preferences for precision handling and system reliability, integration with manufacturing platforms and process control systems, innovations in automation algorithms and precision positioning, and development of specialized solutions with enhanced accuracy and contamination control capabilities. |

Wafer Batch Aligner Market by Segments

Operation Mode:

- Automated

- Manual

Application:

- Wafer

- SiC & GaN Substrate

Region:

- Asia Pacific

- China

- Japan

- India

- South Korea

- ASEAN

- Australia & New Zealand

- Rest of Asia Pacific

- North America

- United States

- Canada

- Mexico

- Europe

- Germany

- United Kingdom

- France

- Italy

- Spain

- Nordic

- BENELUX

- Rest of Europe

- Latin America

- Brazil

- Chile

- Rest of Latin America

- Middle East & Africa

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkey

- South Africa

- Other African Union

- Rest of Middle East & Africa

Frequently Asked Questions

How big is the wafer batch aligner market in 2025?

The global wafer batch aligner market is estimated to be valued at USD 418.2 million in 2025.

What will be the size of wafer batch aligner market in 2035?

The market size for the wafer batch aligner market is projected to reach USD 748.9 million by 2035.

How much will be the wafer batch aligner market growth between 2025 and 2035?

The wafer batch aligner market is expected to grow at a 6.0% CAGR between 2025 and 2035.

What are the key product types in the wafer batch aligner market?

The key product types in wafer batch aligner market are automated and manual.

Which application segment to contribute significant share in the wafer batch aligner market in 2025?

In terms of application, wafer segment to command 72.3% share in the wafer batch aligner market in 2025.

Table of Content

- Executive Summary

- Global Market Outlook

- Demand to side Trends

- Supply to side Trends

- Technology Roadmap Analysis

- Analysis and Recommendations

- Market Overview

- Market Coverage / Taxonomy

- Market Definition / Scope / Limitations

- Market Background

- Market Dynamics

- Drivers

- Restraints

- Opportunity

- Trends

- Scenario Forecast

- Demand in Optimistic Scenario

- Demand in Likely Scenario

- Demand in Conservative Scenario

- Opportunity Map Analysis

- Product Life Cycle Analysis

- Supply Chain Analysis

- Investment Feasibility Matrix

- Value Chain Analysis

- PESTLE and Porter’s Analysis

- Regulatory Landscape

- Regional Parent Market Outlook

- Production and Consumption Statistics

- Import and Export Statistics

- Market Dynamics

- Global Market Analysis 2020 to 2024 and Forecast, 2025 to 2035

- Historical Market Size Value (USD Million) Analysis, 2020 to 2024

- Current and Future Market Size Value (USD Million) Projections, 2025 to 2035

- Y to o to Y Growth Trend Analysis

- Absolute $ Opportunity Analysis

- Global Market Pricing Analysis 2020 to 2024 and Forecast 2025 to 2035

- Global Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Classification

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Classification , 2020 to 2024

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Classification , 2025 to 2035

- Automated

- Manual

- Y to o to Y Growth Trend Analysis By Classification , 2020 to 2024

- Absolute $ Opportunity Analysis By Classification , 2025 to 2035

- Global Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Application

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Application, 2020 to 2024

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Application, 2025 to 2035

- Wafer

- SiC & GaN Substrate

- Y to o to Y Growth Trend Analysis By Application, 2020 to 2024

- Absolute $ Opportunity Analysis By Application, 2025 to 2035

- Global Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Region

- Introduction

- Historical Market Size Value (USD Million) Analysis By Region, 2020 to 2024

- Current Market Size Value (USD Million) Analysis and Forecast By Region, 2025 to 2035

- North America

- Latin America

- Western Europe

- Eastern Europe

- East Asia

- South Asia and Pacific

- Middle East & Africa

- Market Attractiveness Analysis By Region

- North America Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2020 to 2024

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2025 to 2035

- By Country

- USA

- Canada

- Mexico

- By Classification

- By Application

- By Country

- Market Attractiveness Analysis

- By Country

- By Classification

- By Application

- Key Takeaways

- Latin America Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2020 to 2024

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2025 to 2035

- By Country

- Brazil

- Chile

- Rest of Latin America

- By Classification

- By Application

- By Country

- Market Attractiveness Analysis

- By Country

- By Classification

- By Application

- Key Takeaways

- Western Europe Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2020 to 2024

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2025 to 2035

- By Country

- Germany

- UK

- Italy

- Spain

- France

- Nordic

- BENELUX

- Rest of Western Europe

- By Classification

- By Application

- By Country

- Market Attractiveness Analysis

- By Country

- By Classification

- By Application

- Key Takeaways

- Eastern Europe Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2020 to 2024

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2025 to 2035

- By Country

- Russia

- Poland

- Hungary

- Balkan & Baltic

- Rest of Eastern Europe

- By Classification

- By Application

- By Country

- Market Attractiveness Analysis

- By Country

- By Classification

- By Application

- Key Takeaways

- East Asia Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2020 to 2024

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2025 to 2035

- By Country

- China

- Japan

- South Korea

- By Classification

- By Application

- By Country

- Market Attractiveness Analysis

- By Country

- By Classification

- By Application

- Key Takeaways

- South Asia and Pacific Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2020 to 2024

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2025 to 2035

- By Country

- India

- ASEAN

- Australia & New Zealand

- Rest of South Asia and Pacific

- By Classification

- By Application

- By Country

- Market Attractiveness Analysis

- By Country

- By Classification

- By Application

- Key Takeaways

- Middle East & Africa Market Analysis 2020 to 2024 and Forecast 2025 to 2035, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2020 to 2024

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2025 to 2035

- By Country

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkiye

- South Africa

- Other African Union

- Rest of Middle East & Africa

- By Classification

- By Application

- By Country

- Market Attractiveness Analysis

- By Country

- By Classification

- By Application

- Key Takeaways

- Key Countries Market Analysis

- USA

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Canada

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Mexico

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Brazil

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Chile

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Germany

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- UK

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Italy

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Spain

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- France

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- India

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- ASEAN

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Australia & New Zealand

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- China

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Japan

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- South Korea

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Russia

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Poland

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Hungary

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Kingdom of Saudi Arabia

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- Turkiye

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- South Africa

- Pricing Analysis

- Market Share Analysis, 2024

- By Classification

- By Application

- USA

- Market Structure Analysis

- Competition Dashboard

- Competition Benchmarking

- Market Share Analysis of Top Players

- By Regional

- By Classification

- By Application

- Competition Analysis

- Competition Deep Dive

- Emu Technologies

- Overview

- Product Portfolio

- Profitability by Market Segments (Product/Age /Sales Channel/Region)

- Sales Footprint

- Strategy Overview

- Marketing Strategy

- Product Strategy

- Channel Strategy

- SPS-International

- GL Automation

- H-Square

- G2 Automated Technologies

- Chung King Enterprise

- Dou Yee Enterprises

- Honwe Precision

- Shen-Yueh Technology

- Standard Technology

- Chain-Logic International (MPI Corporation)

- Suzhou SOSCH Microelectronics

- Emu Technologies

- Competition Deep Dive

- Assumptions & Acronyms Used

- Research Methodology

List of Tables

- Table 1: Global Market Value (USD Million) Forecast by Region, 2020 to 2035

- Table 2: Global Market Value (USD Million) Forecast by Classification , 2020 to 2035

- Table 3: Global Market Value (USD Million) Forecast by Application, 2020 to 2035

- Table 4: North America Market Value (USD Million) Forecast by Country, 2020 to 2035

- Table 5: North America Market Value (USD Million) Forecast by Classification , 2020 to 2035

- Table 6: North America Market Value (USD Million) Forecast by Application, 2020 to 2035

- Table 7: Latin America Market Value (USD Million) Forecast by Country, 2020 to 2035

- Table 8: Latin America Market Value (USD Million) Forecast by Classification , 2020 to 2035

- Table 9: Latin America Market Value (USD Million) Forecast by Application, 2020 to 2035

- Table 10: Western Europe Market Value (USD Million) Forecast by Country, 2020 to 2035

- Table 11: Western Europe Market Value (USD Million) Forecast by Classification , 2020 to 2035

- Table 12: Western Europe Market Value (USD Million) Forecast by Application, 2020 to 2035

- Table 13: Eastern Europe Market Value (USD Million) Forecast by Country, 2020 to 2035

- Table 14: Eastern Europe Market Value (USD Million) Forecast by Classification , 2020 to 2035

- Table 15: Eastern Europe Market Value (USD Million) Forecast by Application, 2020 to 2035

- Table 16: East Asia Market Value (USD Million) Forecast by Country, 2020 to 2035

- Table 17: East Asia Market Value (USD Million) Forecast by Classification , 2020 to 2035

- Table 18: East Asia Market Value (USD Million) Forecast by Application, 2020 to 2035

- Table 19: South Asia and Pacific Market Value (USD Million) Forecast by Country, 2020 to 2035

- Table 20: South Asia and Pacific Market Value (USD Million) Forecast by Classification , 2020 to 2035

- Table 21: South Asia and Pacific Market Value (USD Million) Forecast by Application, 2020 to 2035

- Table 22: Middle East & Africa Market Value (USD Million) Forecast by Country, 2020 to 2035

- Table 23: Middle East & Africa Market Value (USD Million) Forecast by Classification , 2020 to 2035

- Table 24: Middle East & Africa Market Value (USD Million) Forecast by Application, 2020 to 2035

List of Figures

- Figure 1: Global Market Pricing Analysis

- Figure 2: Global Market Value (USD Million) Forecast 2020-2035

- Figure 3: Global Market Value Share and BPS Analysis by Classification , 2025 and 2035

- Figure 4: Global Market Y to o to Y Growth Comparison by Classification , 2025-2035

- Figure 5: Global Market Attractiveness Analysis by Classification

- Figure 6: Global Market Value Share and BPS Analysis by Application, 2025 and 2035

- Figure 7: Global Market Y to o to Y Growth Comparison by Application, 2025-2035

- Figure 8: Global Market Attractiveness Analysis by Application

- Figure 9: Global Market Value (USD Million) Share and BPS Analysis by Region, 2025 and 2035

- Figure 10: Global Market Y to o to Y Growth Comparison by Region, 2025-2035

- Figure 11: Global Market Attractiveness Analysis by Region

- Figure 12: North America Market Incremental Dollar Opportunity, 2025-2035

- Figure 13: Latin America Market Incremental Dollar Opportunity, 2025-2035

- Figure 14: Western Europe Market Incremental Dollar Opportunity, 2025-2035

- Figure 15: Eastern Europe Market Incremental Dollar Opportunity, 2025-2035

- Figure 16: East Asia Market Incremental Dollar Opportunity, 2025-2035

- Figure 17: South Asia and Pacific Market Incremental Dollar Opportunity, 2025-2035

- Figure 18: Middle East & Africa Market Incremental Dollar Opportunity, 2025-2035

- Figure 19: North America Market Value Share and BPS Analysis by Country, 2025 and 2035

- Figure 20: North America Market Value Share and BPS Analysis by Classification , 2025 and 2035

- Figure 21: North America Market Y to o to Y Growth Comparison by Classification , 2025-2035

- Figure 22: North America Market Attractiveness Analysis by Classification

- Figure 23: North America Market Value Share and BPS Analysis by Application, 2025 and 2035

- Figure 24: North America Market Y to o to Y Growth Comparison by Application, 2025-2035

- Figure 25: North America Market Attractiveness Analysis by Application

- Figure 26: Latin America Market Value Share and BPS Analysis by Country, 2025 and 2035

- Figure 27: Latin America Market Value Share and BPS Analysis by Classification , 2025 and 2035

- Figure 28: Latin America Market Y to o to Y Growth Comparison by Classification , 2025-2035

- Figure 29: Latin America Market Attractiveness Analysis by Classification

- Figure 30: Latin America Market Value Share and BPS Analysis by Application, 2025 and 2035

- Figure 31: Latin America Market Y to o to Y Growth Comparison by Application, 2025-2035

- Figure 32: Latin America Market Attractiveness Analysis by Application

- Figure 33: Western Europe Market Value Share and BPS Analysis by Country, 2025 and 2035

- Figure 34: Western Europe Market Value Share and BPS Analysis by Classification , 2025 and 2035

- Figure 35: Western Europe Market Y to o to Y Growth Comparison by Classification , 2025-2035

- Figure 36: Western Europe Market Attractiveness Analysis by Classification

- Figure 37: Western Europe Market Value Share and BPS Analysis by Application, 2025 and 2035

- Figure 38: Western Europe Market Y to o to Y Growth Comparison by Application, 2025-2035

- Figure 39: Western Europe Market Attractiveness Analysis by Application

- Figure 40: Eastern Europe Market Value Share and BPS Analysis by Country, 2025 and 2035

- Figure 41: Eastern Europe Market Value Share and BPS Analysis by Classification , 2025 and 2035

- Figure 42: Eastern Europe Market Y to o to Y Growth Comparison by Classification , 2025-2035

- Figure 43: Eastern Europe Market Attractiveness Analysis by Classification

- Figure 44: Eastern Europe Market Value Share and BPS Analysis by Application, 2025 and 2035

- Figure 45: Eastern Europe Market Y to o to Y Growth Comparison by Application, 2025-2035

- Figure 46: Eastern Europe Market Attractiveness Analysis by Application

- Figure 47: East Asia Market Value Share and BPS Analysis by Country, 2025 and 2035

- Figure 48: East Asia Market Value Share and BPS Analysis by Classification , 2025 and 2035

- Figure 49: East Asia Market Y to o to Y Growth Comparison by Classification , 2025-2035

- Figure 50: East Asia Market Attractiveness Analysis by Classification

- Figure 51: East Asia Market Value Share and BPS Analysis by Application, 2025 and 2035

- Figure 52: East Asia Market Y to o to Y Growth Comparison by Application, 2025-2035

- Figure 53: East Asia Market Attractiveness Analysis by Application

- Figure 54: South Asia and Pacific Market Value Share and BPS Analysis by Country, 2025 and 2035

- Figure 55: South Asia and Pacific Market Value Share and BPS Analysis by Classification , 2025 and 2035

- Figure 56: South Asia and Pacific Market Y to o to Y Growth Comparison by Classification , 2025-2035

- Figure 57: South Asia and Pacific Market Attractiveness Analysis by Classification

- Figure 58: South Asia and Pacific Market Value Share and BPS Analysis by Application, 2025 and 2035

- Figure 59: South Asia and Pacific Market Y to o to Y Growth Comparison by Application, 2025-2035

- Figure 60: South Asia and Pacific Market Attractiveness Analysis by Application

- Figure 61: Middle East & Africa Market Value Share and BPS Analysis by Country, 2025 and 2035

- Figure 62: Middle East & Africa Market Value Share and BPS Analysis by Classification , 2025 and 2035

- Figure 63: Middle East & Africa Market Y to o to Y Growth Comparison by Classification , 2025-2035

- Figure 64: Middle East & Africa Market Attractiveness Analysis by Classification

- Figure 65: Middle East & Africa Market Value Share and BPS Analysis by Application, 2025 and 2035

- Figure 66: Middle East & Africa Market Y to o to Y Growth Comparison by Application, 2025-2035

- Figure 67: Middle East & Africa Market Attractiveness Analysis by Application

- Figure 68: Global Market - Tier Structure Analysis

- Figure 69: Global Market - Company Share Analysis

Full Research Suite comprises of:

Market outlook & trends analysis

Interviews & case studies

Strategic recommendations

Vendor profiles & capabilities analysis

5-year forecasts

8 regions and 60+ country-level data splits

Market segment data splits

12 months of continuous data updates

DELIVERED AS:

PDF EXCEL ONLINE