3D IC and 2.5D IC Packaging Market

This report captures the current state and future direction of the 3D IC and 2.5D IC packaging market, analyzing market size, revenue forecast, competitive landscape, demand outlook, growth drivers, restraints, industry-specific trends, supply chain developments, and strategic growth avenues.

Historical Data Covered: 2016 to 2024 | Base Year: 2025 | Estimated Year: 2026 | Forecast Period: 2027 to 2036

3D IC and 2.5D IC Packaging Market Size, Market Forecast and Outlook By FMI

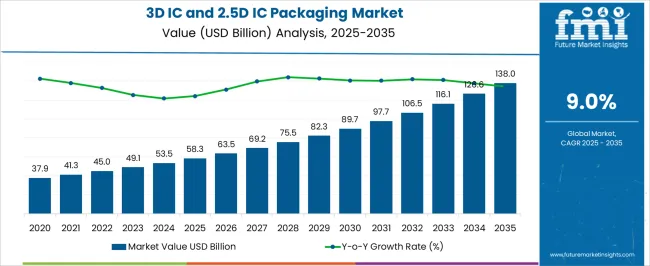

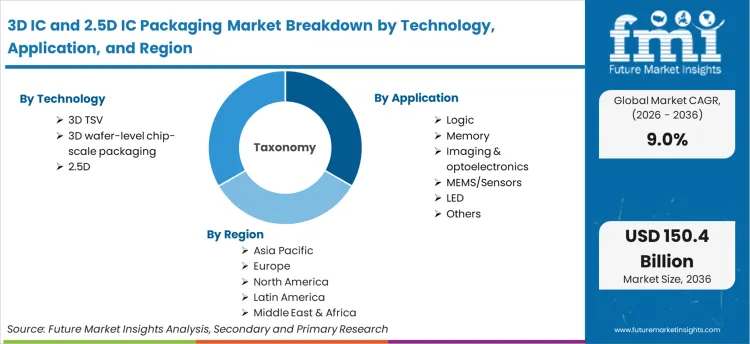

In 2025, the 3d ic and 2.5d ic packaging market was valued at USD 58.30 billion. Based on Future Market Insights' analysis, demand is estimated to grow to USD 63.55 billion in 2026 and USD 150.44 billion by 2036. FMI projects a CAGR of 9.00% during the forecast period.

The market is set to add approximately USD 86.89 billion in absolute terms between 2026 and 2036. AI accelerator and high-bandwidth memory (HBM) demand from data center GPU and TPU deployments is the singular growth catalyst for 3D IC packaging. TSMC CoWoS (Chip-on-Wafer-on-Substrate) and Intel EMIB capacity expansion programs are directly responding to NVIDIA, AMD, and Google chip packaging requirements that conventional 2D packaging cannot physically satisfy due to interconnect density and memory bandwidth limitations.

Summary of 3D IC and 2.5D IC Packaging Market

-

3D IC and 2.5D IC Packaging Market Definition

- 3D IC and 2.5D IC packaging encompasses advanced semiconductor packaging technologies using through-silicon vias (TSVs), silicon interposers, and wafer-level chip-scale packaging to vertically and laterally integrate multiple die into a single package for logic, memory, imaging, sensor, and LED applications.

- Demand Drivers in the Market

- AI accelerator chip packaging demand from NVIDIA (H100/B100 GPU), AMD (MI300X), and Google (TPU v5) requires 2.5D CoWoS and EMIB interposer technologies to integrate HBM memory stacks adjacent to logic die, generating the largest single-year advanced packaging capacity requirements in semiconductor industry history.

- HBM (High Bandwidth Memory) production by SK Hynix, Samsung, and Micron requires 3D TSV stacking of 8 to 12 DRAM die per package, with each AI GPU consuming 4 to 6 HBM stacks, creating a multiplicative demand relationship between AI chip production and 3D TSV packaging volume.

- Automotive sensor fusion modules integrating LiDAR ASIC, radar processor, and vision processor die into heterogeneous 2.5D packages are creating a new application category for advanced packaging beyond the traditional consumer electronics and data center segments.

- Key Segments Analyzed in the FMI Report

- 3D TSV technology: 50.6% share in 2026, reflecting its structural position as the primary category across established procurement channels.

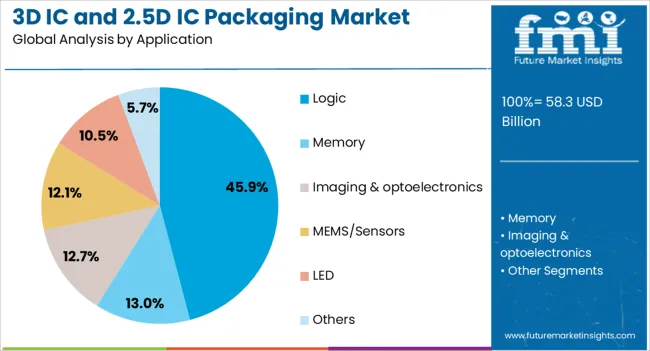

- Logic application: 45.9% share in 2026, reflecting its structural position as the primary category across established procurement channels.

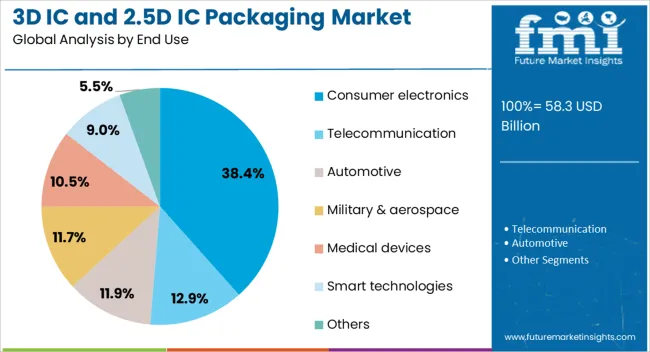

- Consumer Electronics end use: 38.4% share in 2026, reflecting its structural position as the primary category across established procurement channels.

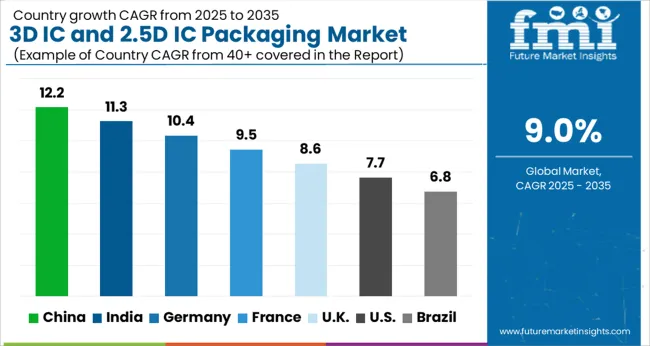

- China: 12.20% compound growth through 2036, indicating concentrated demand acceleration.

- Analyst Opinion at FMI

- The 3D IC and 2.5D IC packaging market is experiencing the most concentrated demand surge in semiconductor packaging history, driven by AI accelerator production schedules. FMI analysts observe that 3D TSV technology commands 50.6% share because HBM memory stacking is physically impossible without TSV interconnects, making this technology a non-substitutable requirement for every AI GPU shipped. Logic application at 45.9% share leads because AI accelerator logic die are the design-in anchor that pulls HBM, interposer, and substrate demand through the supply chain. Consumer electronics at 38.4% end-use share captures the smartphone AP (application processor) and gaming GPU segments that pioneered advanced packaging before the AI data center wave. China leads at 12.2% CAGR as domestic OSAT capacity expansion programs respond to geopolitical supply chain diversification requirements.

- Strategic Implications / Executive Takeaways

- OSAT companies must secure CoWoS and EMIB-equivalent advanced packaging capacity to capture allocation from AI chip designers facing 12-to-18 month lead times at TSMC and Intel packaging facilities.

- Memory manufacturers should accelerate 12-high HBM4 TSV stacking development to maintain qualification positions with NVIDIA, AMD, and custom AI chip programs requiring next-generation memory bandwidth.

- Automotive Tier-1 suppliers should initiate 2.5D packaging qualification programs for sensor fusion modules to capture the emerging advanced packaging opportunity in ADAS and autonomous driving compute platforms.

3D IC and 2.5D IC Packaging Market Key Takeaways

| Metric | Details |

|---|---|

| Industry Size (2026) | USD 63.55 Billion |

| Industry Value (2036) | USD 150.44 Billion |

| CAGR (2026 to 2036) | 9.00% |

Source: Future Market Insights, 2026

As per FMI, country-level growth rates through 2036 are projected as follows: China at 12.20%, India at 11.30%, Germany at 10.40%, France at 9.50%, UK at 8.60%, USA at 7.70%, Brazil at 6.80%. China records the fastest expansion driven by concentrated institutional investment and infrastructure development.

3D IC and 2.5D IC Packaging Market Definition

The 3D IC and 2.5D IC packaging market represents the advanced semiconductor packaging technology layer enabling heterogeneous die integration beyond the physical limits of conventional 2D packaging. 3D TSV technology stacks multiple die vertically using through-silicon via interconnects, while 2.5D packaging places die side-by-side on a silicon interposer for lateral high-bandwidth communication. FMI is of the opinion that the market is in an AI-driven capacity expansion phase where HBM memory stacking and logic interposer packaging for AI accelerators are consuming advanced packaging capacity faster than the industry can build it.

3D IC and 2.5D IC Packaging Market Inclusions

Market scope covers 3D TSV packaging, 3D wafer-level chip-scale packaging, and 2.5D silicon interposer packaging technologies for logic processors, HBM memory stacks, image sensors, MEMS devices, and LED arrays across consumer electronics, telecom, automotive, aerospace, and medical end-use segments.

3D IC and 2.5D IC Packaging Market Exclusions

Conventional 2D wire-bond and flip-chip packaging without TSV or interposer integration, standalone PCB substrates, and general semiconductor wafer fabrication services not classified as advanced packaging are excluded.

3D IC and 2.5D IC Packaging Market Research Methodology

- Primary Research: Analysts conducted structured interviews with procurement managers, product engineers, and distribution channel operators to map purchase decision triggers and specification requirements across key verticals.

- Desk Research: Data collection aggregated regulatory filings, industry standards documentation, patent registries, trade body publications, and company annual reports across all target geographies.

- Market-Sizing and Forecasting: Baseline values derive from a bottom-up aggregation of product shipment volumes and average selling prices, validated against publicly disclosed revenue figures from leading suppliers.

- Data Validation and Update Cycle: Projections are cross-referenced against quarterly earnings data, import-export trade statistics, and industry association production reports to maintain forecast integrity.

Why is the 3D IC and 2.5D IC Packaging Market Growing?

The 3D IC and 2.5D IC packaging market is experiencing significant expansion due to the increasing demand for miniaturization and enhanced performance in semiconductor devices. The market growth is being propelled by the rising need for higher bandwidth, improved power efficiency, and reduced latency in electronics.

These advanced packaging technologies enable the stacking and integration of multiple chips within a single package, which supports the development of compact, high-functioning devices used in consumer electronics, data centers, and telecommunications. Innovations in interconnect technology and thermal management are further facilitating the adoption of these packaging solutions.

The market outlook remains strong as emerging applications in artificial intelligence, 5G communications, and automotive electronics continue to drive the demand for sophisticated packaging methods that can accommodate complex chip architectures and deliver superior performance.

Segmental Analysis

The 3d ic and 2.5d ic packaging market is segmented by technology, application, end use, and geographic regions. By technology, 3d ic and 2.5d ic packaging market is divided into 3D TSV, 3D wafer-level chip-scale packaging, and 2.5D. In terms of application, 3d ic and 2.5d ic packaging market is classified into Logic, Memory, Imaging & optoelectronics, MEMS/Sensors, LED, and Others. Based on end use, 3d ic and 2.5d ic packaging market is segmented into Consumer electronics, Telecommunication, Automotive, Military & aerospace, Medical devices, Smart technologies, and Others. Regionally, the 3d ic and 2.5d ic packaging industry is classified into North America, Latin America, Western Europe, Eastern Europe, Balkan & Baltic Countries, Russia & Belarus, Central Asia, East Asia, South Asia & Pacific, and the Middle East & Africa.

Insights into the 3D TSV Technology Segment

The 3D TSV technology segment is projected to hold 50.6% of the market revenue share in 2026, making it the leading technology type in the 3D IC and 2.5D IC packaging market. This position is being attributed to the superior vertical integration capabilities of 3D TSV, which enables high-density interconnects and reduces the length of inter-chip connections, thereby improving signal integrity and power efficiency.

The technology has found widespread acceptance in applications demanding compact and high-performance chip packages. Its ability to support heterogeneous integration of different chip types has further accelerated its adoption.

Additionally, advancements in TSV fabrication processes have enhanced yield and reduced costs, making this technology more accessible for mass production.

Insights into the Logic Application Segment

The logic application segment is expected to capture 45.9% of the market revenue share in 2026, leading all application categories. The growth of this segment is being driven by the increasing complexity and performance requirements of logic chips used in processors and microcontrollers.

Logic applications benefit significantly from 3D and 2.5D packaging due to the enhanced data transfer rates and lower power consumption that these packaging methods provide. The demand for high-performance computing and mobile devices has further fueled the adoption of advanced packaging solutions in logic applications.

The ability to integrate memory and logic components within a single package supports performance optimization and space savings, which are critical factors in the continued expansion of this segment.

Insights into the Consumer Electronics End Use Segment

The consumer electronics end-use industry segment is projected to hold 38.4% of the market revenue share in 2026, making it the largest end-use sector in the 3D IC and 2.5D IC packaging market. This leadership is being attributed to the rapid proliferation of smartphones, tablets, wearable devices, and other portable electronics that demand miniaturized and high-performance semiconductor components.

The consumer electronics industry favors packaging technologies that enable compact designs while delivering improved speed and energy efficiency. As consumer expectations for device functionality and form factor continue to rise, the adoption of 3D and 2.5D packaging solutions has been accelerated.

Furthermore, the need for cost-effective manufacturing and faster time-to-market has encouraged manufacturers to embrace these packaging technologies in consumer electronics production lines.

What are the Drivers, Restraints, and Key Trends of the 3D IC and 2.5D IC Packaging Market?

The 3D IC and 2.5D IC packaging market is shaped by high-performance computing, consumer electronics adoption, automotive applications, and cost-supply dynamics. Growth will accelerate as integration density and efficiency remain decisive levers.

Expanding Role of High-Performance Computing Demand

The 3D IC and 2.5D IC packaging sector is heavily shaped by increasing reliance on high-performance computing. Data centers, AI accelerators, and enterprise cloud workloads demand compact, thermally efficient packages that deliver high bandwidth and low latency. The transition from conventional packaging to stacked dies and interposers has been reinforced by exponential growth in AI and machine learning models that require faster memory access. The compound annual growth shows that integration density and reduced power consumption are not just technological shifts but commercial necessities. This dynamic anchors the market firmly in the enterprise computing ecosystem, where workload optimization dictates rapid adoption of advanced packaging solutions.

Rising Adoption Across Consumer Electronics Ecosystems

Consumer electronics continues to strengthen its role as a major driver of 3D IC and 2.5D IC packaging. Smartphones, tablets, AR/VR devices, and wearables are increasingly built with stacked memory and interposer-based designs to reduce footprint while improving efficiency. This evolution ensures better graphics performance, faster processing, and superior thermal handling for compact devices. Companies focus on advanced packaging to differentiate in a saturated electronics market, making integration density a competitive necessity. Shift from traditional single-die packages to 3D structures is no longer an optional strategy but an inevitable outcome of consumer preferences for high-speed, low-power, and feature-rich devices.

Automotive Electronics and Advanced Driver Assistance Systems

The automotive industry plays a crucial role in the adoption of 3D IC and 2.5D IC packaging. Advanced driver assistance systems, autonomous driving platforms, and infotainment modules demand higher computational capacity, which 3D stacking and interposers provide efficiently. These systems require lower power footprints while ensuring reliability in harsh operating conditions. Automotive OEMs are integrating advanced packaging to handle sensor fusion, real-time data analytics, and in-vehicle connectivity. This dynamic positions automotive applications as a transformative growth avenue where safety, efficiency, and processing speed converge. Long-term adoption will be driven by regulations supporting vehicle automation and electrification strategies globally.

Cost Structures, Yield Challenges, and Supply Chain

Despite growth momentum, the 3D IC and 2.5D IC packaging sector faces constraints from cost structures, yield management, and supply chain complexities. Yield losses in through-silicon-via processes and thermal management costs elevate production challenges. Suppliers focus on modular interposers and improved assembly methods to lower costs. Regional dependence on advanced fabs creates vulnerabilities, as geopolitical and material shortages can delay adoption. Yet, these challenges also drive differentiation where companies mastering process yield and cost reduction secure a premium advantage. The ability to address these barriers through partnerships, scale economies, and advanced testing will define market leaders and their long-term profitability.

Analysis of 3D IC and 2.5D IC Packaging Market By Key Countries

.webp)

| Country | CAGR |

|---|---|

| China | 12.2% |

| India | 11.3% |

| Germany | 10.4% |

| France | 9.5% |

| UK | 8.6% |

| USA | 7.7% |

| Brazil | 6.8% |

The global 3D IC and 2.5D IC packaging market is projected to grow at a CAGR of 9.0% from 2026 to 2036. China leads at 12.2%, followed by India at 11.3%, Germany at 10.4%, France at 9.5%, the UK at 8.6%, and the USA at 7.7%. Growth is driven by strong adoption of heterogeneous integration, AI accelerators, memory stacking, and advanced chiplet designs that deliver higher bandwidth and lower power consumption. Asia-Pacific, particularly China and India, demonstrates rapid expansion through semiconductor manufacturing capacity, government-led incentives, and domestic electronics consumption. Germany and France emphasize automotive electronics, industrial automation, and high-efficiency computing, while the UK expands through design leadership and collaborative R&D hubs. The USA focuses on AI computing, defense applications, and large-scale data center integration, maintaining steady but competitive growth. Foundry partnerships, packaging innovation, and end-use diversification further enhance dollar sales and market share. The analysis includes over 40+ countries, with the leading markets highlighted above.

Market Insights of 3D IC and 2.5D IC Packaging in China

The 3D IC and 2.5D IC packaging market in China is projected to grow at a CAGR of 12.2% from 2026 to 2036, supported by strong government-led semiconductor policies, expanding foundry capabilities, and large-scale consumer electronics production. Chinese firms are investing heavily in through-silicon-via (TSV) technology and advanced interposers, allowing them to compete with global leaders in chiplet integration. Rapid adoption is being observed across AI, high-performance computing, and 5G infrastructure, where performance density and power efficiency are critical. Domestic partnerships with cloud service providers and international technology firms strengthen China’s global supply chain footprint. China’s scale, combined with its policy-driven push for semiconductor independence, positions it as the leading market globally.

- Government-backed semiconductor expansion programs

- Rising demand from AI and 5G ecosystems

- Domestic foundries scaling TSV and interposer technologies

Demand Outlook of 3D IC and 2.5D IC Packaging in India

The 3D IC and 2.5D IC packaging market in India is expected to grow at a CAGR of 11.3% between 2026 and 2036, driven by surging demand in consumer electronics, telecom infrastructure, and renewable-linked digital grids. Domestic semiconductor programs such as “Make in India” are encouraging foundry development and localized assembly. India’s IT and data center industry provides an expanding base for advanced packaging adoption, while global players are partnering with Indian firms to set up pilot lines. AI startups, cloud providers, and gaming ecosystems are fostering demand for high-performance chiplet integration. India’s ability to combine cost efficiency with growing domestic consumption will ensure its place as one of the fastest-growing hubs.

- Make in India fueling semiconductor packaging growth

- Data centers and telecom accelerating adoption

- International collaborations enhancing local capabilities

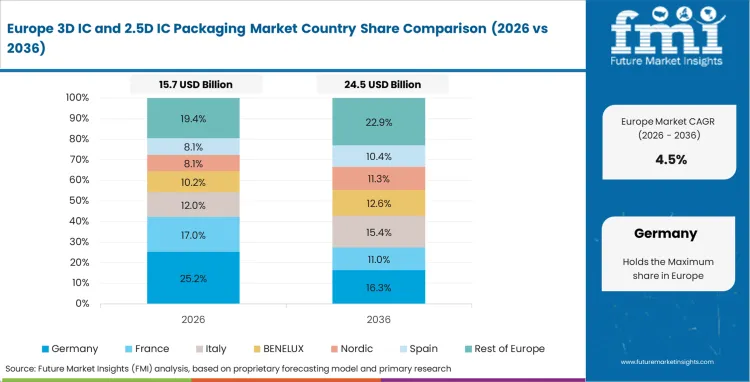

Expansion Trends of 3D IC and 2.5D IC Packaging in European

The 3D IC and 2.5D IC packaging market in France is projected to expand at a CAGR of 9.5% from 2026 to 2036, supported by research-driven initiatives and government incentives for semiconductor R&D. France plays a crucial role in European semiconductor strategy, focusing on automotive electronics, aerospace, and industrial automation where reliability and miniaturization are vital. Adoption is reinforced by partnerships with major European chipmakers and institutes focusing on heterogeneous integration. Pilot projects in renewable energy and edge computing reinforce demand for advanced packaging solutions. France is developing a quality-driven market, where innovation pipelines and government-funded programs create sustainable momentum despite its smaller production base.

- Automotive and aerospace driving advanced adoption

- Government incentives strengthening semiconductor research

- Partnerships with European chipmakers expanding footprint

Growth Outlook of 3D IC and 2.5D IC Packaging in the UK

The 3D IC and 2.5D IC packaging market in the UK is anticipated to grow at a CAGR of 8.6% between 2026 and 2036, with strong emphasis on design leadership, R&D partnerships, and pilot-scale semiconductor projects. The UK focuses on advanced packaging for AI, defense, and quantum computing applications, with universities and research institutions contributing to cutting-edge design. Though large-scale fabrication is limited, international partnerships allow access to advanced manufacturing capacity. Startups in chip design are adopting chiplet-based architectures, ensuring steady demand for 2.5D interposers and 3D stacking. The UK’s role will be defined more by design innovation and niche application strength than by mass production.

- Design innovation driving niche semiconductor growth

- Research institutions contributing to advanced packaging

- International partnerships enabling large-scale access

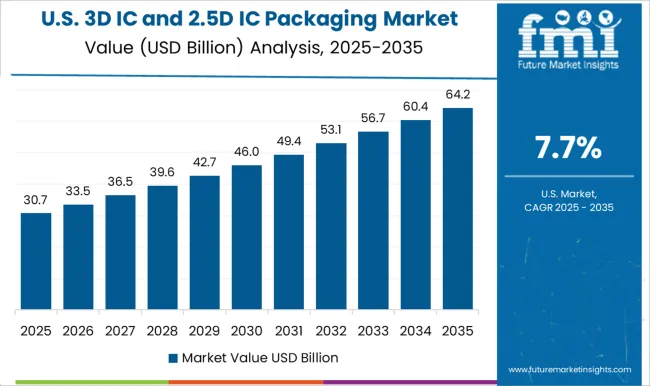

Market Growth Analysis of 3D IC and 2.5D IC Packaging in the USA

The 3D IC and 2.5D IC packaging market in the USA is projected to grow at a CAGR of 7.7% from 2026 to 2036, with growth anchored in defense electronics, high-performance computing, and hyperscale data centers. USA semiconductor firms are at the forefront of developing chiplet architectures, with strong integration into AI and cloud ecosystems. Government-backed programs such as the CHIPS Act are funding advanced packaging R&D and manufacturing initiatives. Automotive and aerospace sectors also drive adoption, requiring reliable, thermally efficient chip packages for mission-critical applications. While growth is steadier compared to Asia, the USA maintains leadership in innovation, IP ownership, and early commercialization of advanced 3D packaging technologies.

- Defense and AI workloads driving adoption

- CHIPS Act funding advanced packaging initiatives

- Cloud and data centers strengthening demand base

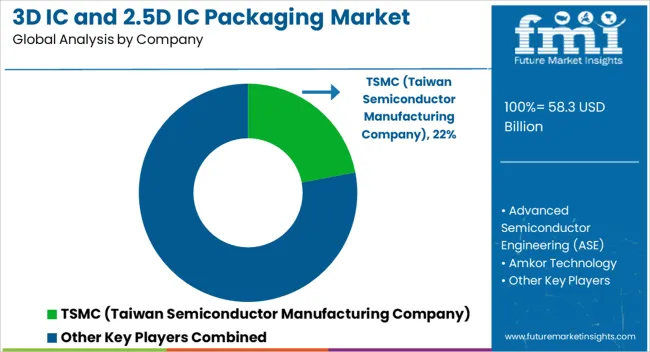

Competitive Landscape of 3D IC and 2.5D IC Packaging Market

Competition in the 3D IC and 2.5D IC packaging market is defined by integration density, advanced interconnect solutions, and efficiency in high-performance computing applications. TSMC (Taiwan Semiconductor Manufacturing Company) leads with cutting-edge wafer-level packaging and through-silicon-via (TSV) technologies, dominating global demand through strong foundry capabilities and partnerships with leading fabless firms. Samsung Electronics and Intel Corporation compete closely by leveraging their advanced node capabilities and in-house design-to-packaging integration, focusing on data centers, AI processors, and consumer electronics. Amkor Technology and Advanced Semiconductor Engineering (ASE) differentiate as outsourced semiconductor assembly and test (OSAT) leaders, offering scalable 2.5D and 3D integration platforms that support global fabless chipmakers.

Broadcom, Xilinx, and Texas Instruments emphasize customized solutions for networking, FPGAs, and analog-intensive applications, reinforcing the role of packaging in enhancing device performance. Companies like JCET, SPIL, Powertech Technology Inc. (PTI), and ChipMOS Technologies serve as essential global OSAT players, providing cost-competitive packaging with regional strengths in Asia. Japanese firms Mitsubishi Electric Corporation and Toshiba Corporation focus on automotive, industrial, and energy applications where reliability and thermal management are critical, while United Microelectronics Corporation (UMC) contributes by combining foundry and packaging capabilities for select markets. Strategic initiatives across these companies highlight collaborations with equipment manufacturers, ecosystem partnerships, and heavy investment in R&D to improve yield rates and manage costs in TSV and interposer-based technologies. Product documentation across the industry highlights features such as interposer thickness, TSV density, thermal dissipation efficiency, and compatibility with logic-memory integration. Brochures emphasize performance metrics, power consumption reduction, and system-level optimization.

Competitive strategies emphasize differentiation through heterogeneous integration, ecosystem alignment with AI and 5G markets, and co-development with fabless and systems companies. The market is marked by a blend of foundry dominance, OSAT scale, and specialized providers carving niches in automotive, networking, and FPGA-driven demand.

Key Players in the 3D IC and 2.5D IC Packaging Market

- TSMC (Taiwan Semiconductor Manufacturing Company)

- Advanced Semiconductor Engineering (ASE)

- Amkor Technology

- Broadcom

- ChipMOS Technologies Inc

- Intel Corporation

- Jiangsu Changjiang Electronics Technology (JCET)

- Mitsubishi Electric Corporation

- Powertech Technology Inc. (PTI)

- Samsung Electronics

- Siliconware Precision Industries (SPIL)

- Texas Instrument

- Toshiba Corporation

- United Microelectronics Corporation (UMC)

- Xilinx Inc.

Scope of the Report

| Metric | Value |

|---|---|

| Quantitative Units | USD 63.55 Bn to USD 150.44 Bn, at a CAGR of 9.00% |

| Market Definition | 3D IC and 2.5D IC packaging encompasses advanced semiconductor packaging technologies using through-silicon vias (TSVs), silicon interposers, and wafer-level chip-scale packaging to vertically and laterally integrate multiple die into a single package for logic, memory, imaging, sensor, and LED applications. |

| Technology Segmentation | 3D TSV, 3D Wafer-Level Chip-Scale Packaging, 2.5D |

| Application Segmentation | Logic, Memory, Imaging & Optoelectronics, MEMS/Sensors, LED, Others |

| End Use Segmentation | Consumer Electronics, Telecommunication, Automotive, Military & Aerospace, Medical Devices, Smart Technologies, Others |

| Regions Covered | North America, Latin America, Europe, East Asia, South Asia, Oceania, Middle East & Africa |

| Countries Covered | China, India, Germany, France, UK, USA, Brazil, and 40 plus countries |

| Key Companies Profiled | TSMC, Advanced Semiconductor Engineering (ASE), Amkor Technology, Broadcom, ChipMOS Technologies Inc, Intel Corporation, Jiangsu Changjiang Electronics Technology (JCET), Mitsubishi Electric Corporation, Powertech Technology Inc. (PTI), Samsung Electronics, Siliconware Precision Industries (SPIL), Texas Instruments, Toshiba Corporation, United Microelectronics Corporation (UMC), Xilinx Inc. |

| Forecast Period | 2026 to 2036 |

| Approach | Hybrid bottom-up and top-down modeling validated against primary research inputs and publicly available industry data. |

3D IC and 2.5D IC Packaging Market by Segments

Technology:

- 3D TSV

- 3D wafer-level chip-scale packaging

- 2.5D

Application:

- Logic

- Memory

- Imaging & optoelectronics

- MEMS/Sensors

- LED

- Others

End Use:

- Consumer electronics

- Telecommunication

- Automotive

- Military & aerospace

- Medical devices

- Smart technologies

- Others

Region:

- North America

- USA

- Canada

- Mexico

- Latin America

- Brazil

- Chile

- Rest of Latin America

- Western Europe

- Germany

- UK

- Italy

- Spain

- France

- Nordic

- BENELUX

- Rest of Western Europe

- Eastern Europe

- Russia

- Poland

- Hungary

- Balkan & Baltic

- Rest of Eastern Europe

- East Asia

- China

- Japan

- South Korea

- South Asia and Pacific

- India

- ASEAN

- Australia & New Zealand

- Rest of South Asia and Pacific

- Middle East & Africa

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkiye

- South Africa

- Other African Union

- Rest of Middle East & Africa

Bibliography

- [1] TSMC. (2024). Annual Report 2024: Advanced Packaging Technology Division. TSMC.

- [2] SEMI. (2024). Global Semiconductor Packaging Market Statistics Report. SEMI.

- [3] International Technology Roadmap for Semiconductors. (2024). Heterogeneous Integration Roadmap. IEEE/SEMI.

- [4] SK Hynix. (2024). HBM Product Roadmap: 3D TSV Stacking Technology. SK Hynix.

- [5] Intel Corporation. (2024). EMIB and Foveros Advanced Packaging Technology Update. Intel.

This bibliography is provided for reader reference. The full FMI report contains the complete reference list with primary research documentation.

Frequently Asked Questions

How large is the demand for 3D IC and 2.5D IC Packaging in the global market in 2026?

Demand for 3D IC and 2.5D IC Packaging in the global market is estimated to be valued at USD 63.55 billion in 2026.

What will be the market size of 3D IC and 2.5D IC Packaging by 2036?

Market size for 3D IC and 2.5D IC Packaging is projected to reach USD 150.44 billion by 2036.

What is the expected demand growth between 2026 and 2036?

Demand is expected to grow at a CAGR of 9.00% between 2026 and 2036.

Which Technology is poised to lead by 2026?

3D TSV accounts for 50.6% in 2026, reflecting its established position across primary channels.

How significant is Logic in driving adoption?

Logic represents 45.9% of segment share in 2026.

What country records the fastest growth?

China is projected to grow at a CAGR of 12.20% during 2026 to 2036.

What is the projected growth for India?

India is projected to expand at a CAGR of 11.30% during 2026 to 2036.

What is included in the scope of this report?

Market scope covers 3D TSV packaging, 3D wafer-level chip-scale packaging, and 2.5D silicon interposer packaging technologies for logic processors, HBM memory stacks, image sensors, MEMS devices, and LED arrays across consumer electronics, telecom, automotive, aerospace, and medical end-use segments.

Table of Content

- Executive Summary

- Global Market Outlook

- Demand to side Trends

- Supply to side Trends

- Technology Roadmap Analysis

- Analysis and Recommendations

- Market Overview

- Market Coverage / Taxonomy

- Market Definition / Scope / Limitations

- Research Methodology

- Chapter Orientation

- Analytical Lens and Working Hypotheses

- Market Structure, Signals, and Trend Drivers

- Benchmarking and Cross-market Comparability

- Market Sizing, Forecasting, and Opportunity Mapping

- Research Design and Evidence Framework

- Desk Research Programme (Secondary Evidence)

- Company Annual and Sustainability Reports

- Peer-reviewed Journals and Academic Literature

- Corporate Websites, Product Literature, and Technical Notes

- Earnings Decks and Investor Briefings

- Statutory Filings and Regulatory Disclosures

- Technical White Papers and Standards Notes

- Trade Journals, Industry Magazines, and Analyst Briefs

- Conference Proceedings, Webinars, and Seminar Materials

- Government Statistics Portals and Public Data Releases

- Press Releases and Reputable Media Coverage

- Specialist Newsletters and Curated Briefings

- Sector Databases and Reference Repositories

- FMI Internal Proprietary Databases and Historical Market Datasets

- Subscription Datasets and Paid Sources

- Social Channels, Communities, and Digital Listening Inputs

- Additional Desk Sources

- Expert Input and Fieldwork (Primary Evidence)

- Primary Modes

- Qualitative Interviews and Expert Elicitation

- Quantitative Surveys and Structured Data Capture

- Blended Approach

- Why Primary Evidence is Used

- Field Techniques

- Interviews

- Surveys

- Focus Groups

- Observational and In-context Research

- Social and Community Interactions

- Stakeholder Universe Engaged

- C-suite Leaders

- Board Members

- Presidents and Vice Presidents

- R&D and Innovation Heads

- Technical Specialists

- Domain Subject-matter Experts

- Scientists

- Physicians and Other Healthcare Professionals

- Governance, Ethics, and Data Stewardship

- Research Ethics

- Data Integrity and Handling

- Primary Modes

- Tooling, Models, and Reference Databases

- Desk Research Programme (Secondary Evidence)

- Data Engineering and Model Build

- Data Acquisition and Ingestion

- Cleaning, Normalisation, and Verification

- Synthesis, Triangulation, and Analysis

- Quality Assurance and Audit Trail

- Market Background

- Market Dynamics

- Drivers

- Restraints

- Opportunity

- Trends

- Scenario Forecast

- Demand in Optimistic Scenario

- Demand in Likely Scenario

- Demand in Conservative Scenario

- Opportunity Map Analysis

- Product Life Cycle Analysis

- Supply Chain Analysis

- Investment Feasibility Matrix

- Value Chain Analysis

- PESTLE and Porter’s Analysis

- Regulatory Landscape

- Regional Parent Market Outlook

- Production and Consumption Statistics

- Import and Export Statistics

- Market Dynamics

- Global Market Analysis 2021 to 2025 and Forecast, 2026 to 2036

- Historical Market Size Value (USD Million) Analysis, 2021 to 2025

- Current and Future Market Size Value (USD Million) Projections, 2026 to 2036

- Y to o to Y Growth Trend Analysis

- Absolute $ Opportunity Analysis

- Global Market Pricing Analysis 2021 to 2025 and Forecast 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Technology

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Technology , 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Technology , 2026 to 2036

- 3D TSV

- 3D wafer-level chip-scale packaging

- 2.5D

- 3D TSV

- Y to o to Y Growth Trend Analysis By Technology , 2021 to 2025

- Absolute $ Opportunity Analysis By Technology , 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Application

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Application, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Application, 2026 to 2036

- Logic

- Memory

- Imaging & optoelectronics

- MEMS/Sensors

- LED

- Others

- Logic

- Y to o to Y Growth Trend Analysis By Application, 2021 to 2025

- Absolute $ Opportunity Analysis By Application, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By End Use

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By End Use, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By End Use, 2026 to 2036

- Consumer electronics

- Telecommunication

- Automotive

- Military & aerospace

- Medical devices

- Smart technologies

- Others

- Consumer electronics

- Y to o to Y Growth Trend Analysis By End Use, 2021 to 2025

- Absolute $ Opportunity Analysis By End Use, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Region

- Introduction

- Historical Market Size Value (USD Million) Analysis By Region, 2021 to 2025

- Current Market Size Value (USD Million) Analysis and Forecast By Region, 2026 to 2036

- North America

- Latin America

- Western Europe

- Eastern Europe

- East Asia

- South Asia and Pacific

- Middle East & Africa

- Market Attractiveness Analysis By Region

- North America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- USA

- Canada

- Mexico

- By Technology

- By Application

- By End Use

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology

- By Application

- By End Use

- Key Takeaways

- Latin America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Brazil

- Chile

- Rest of Latin America

- By Technology

- By Application

- By End Use

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology

- By Application

- By End Use

- Key Takeaways

- Western Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Germany

- UK

- Italy

- Spain

- France

- Nordic

- BENELUX

- Rest of Western Europe

- By Technology

- By Application

- By End Use

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology

- By Application

- By End Use

- Key Takeaways

- Eastern Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Russia

- Poland

- Hungary

- Balkan & Baltic

- Rest of Eastern Europe

- By Technology

- By Application

- By End Use

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology

- By Application

- By End Use

- Key Takeaways

- East Asia Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- China

- Japan

- South Korea

- By Technology

- By Application

- By End Use

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology

- By Application

- By End Use

- Key Takeaways

- South Asia and Pacific Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- India

- ASEAN

- Australia & New Zealand

- Rest of South Asia and Pacific

- By Technology

- By Application

- By End Use

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology

- By Application

- By End Use

- Key Takeaways

- Middle East & Africa Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkiye

- South Africa

- Other African Union

- Rest of Middle East & Africa

- By Technology

- By Application

- By End Use

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology

- By Application

- By End Use

- Key Takeaways

- Key Countries Market Analysis

- USA

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Canada

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Mexico

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Brazil

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Chile

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Germany

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- UK

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Italy

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Spain

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- France

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- India

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- ASEAN

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Australia & New Zealand

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- China

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Japan

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- South Korea

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Russia

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Poland

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Hungary

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Kingdom of Saudi Arabia

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- Turkiye

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- South Africa

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology

- By Application

- By End Use

- USA

- Market Structure Analysis

- Competition Dashboard

- Competition Benchmarking

- Market Share Analysis of Top Players

- By Regional

- By Technology

- By Application

- By End Use

- Competition Analysis

- Competition Deep Dive

- TSMC (Taiwan Semiconductor Manufacturing Company)

- Overview

- Product Portfolio

- Profitability by Market Segments (Product/Age /Sales Channel/Region)

- Sales Footprint

- Strategy Overview

- Marketing Strategy

- Product Strategy

- Channel Strategy

- Advanced Semiconductor Engineering (ASE)

- Amkor Technology

- Broadcom

- ChipMOS Technologies Inc

- Intel Corporation

- Jiangsu Changjiang Electronics Technology (JCET)

- Mitsubishi Electric Corporation

- Powertech Technology Inc. (PTI)

- Samsung Electronics

- Siliconware Precision Industries (SPIL)

- Texas Instrument

- Toshiba Corporation

- Value (USD Million)ed Microelectronics Corporation (UMC)

- Xilinx Inc.

- TSMC (Taiwan Semiconductor Manufacturing Company)

- Competition Deep Dive

- Assumptions & Acronyms Used

List of Tables

- Table 1: Global Market Value (USD Million) Forecast by Region, 2021 to 2036

- Table 2: Global Market Value (USD Million) Forecast by Technology , 2021 to 2036

- Table 3: Global Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 4: Global Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 5: North America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 6: North America Market Value (USD Million) Forecast by Technology , 2021 to 2036

- Table 7: North America Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 8: North America Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 9: Latin America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 10: Latin America Market Value (USD Million) Forecast by Technology , 2021 to 2036

- Table 11: Latin America Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 12: Latin America Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 13: Western Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 14: Western Europe Market Value (USD Million) Forecast by Technology , 2021 to 2036

- Table 15: Western Europe Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 16: Western Europe Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 17: Eastern Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 18: Eastern Europe Market Value (USD Million) Forecast by Technology , 2021 to 2036

- Table 19: Eastern Europe Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 20: Eastern Europe Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 21: East Asia Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 22: East Asia Market Value (USD Million) Forecast by Technology , 2021 to 2036

- Table 23: East Asia Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 24: East Asia Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 25: South Asia and Pacific Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 26: South Asia and Pacific Market Value (USD Million) Forecast by Technology , 2021 to 2036

- Table 27: South Asia and Pacific Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 28: South Asia and Pacific Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 29: Middle East & Africa Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 30: Middle East & Africa Market Value (USD Million) Forecast by Technology , 2021 to 2036

- Table 31: Middle East & Africa Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 32: Middle East & Africa Market Value (USD Million) Forecast by End Use, 2021 to 2036

List of Figures

- Figure 1: Global Market Pricing Analysis

- Figure 2: Global Market Value (USD Million) Forecast 2021-2036

- Figure 3: Global Market Value Share and BPS Analysis by Technology , 2026 and 2036

- Figure 4: Global Market Y-o-Y Growth Comparison by Technology , 2026-2036

- Figure 5: Global Market Attractiveness Analysis by Technology

- Figure 6: Global Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 7: Global Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 8: Global Market Attractiveness Analysis by Application

- Figure 9: Global Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 10: Global Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 11: Global Market Attractiveness Analysis by End Use

- Figure 12: Global Market Value (USD Million) Share and BPS Analysis by Region, 2026 and 2036

- Figure 13: Global Market Y-o-Y Growth Comparison by Region, 2026-2036

- Figure 14: Global Market Attractiveness Analysis by Region

- Figure 15: North America Market Incremental Dollar Opportunity, 2026-2036

- Figure 16: Latin America Market Incremental Dollar Opportunity, 2026-2036

- Figure 17: Western Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 18: Eastern Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 19: East Asia Market Incremental Dollar Opportunity, 2026-2036

- Figure 20: South Asia and Pacific Market Incremental Dollar Opportunity, 2026-2036

- Figure 21: Middle East & Africa Market Incremental Dollar Opportunity, 2026-2036

- Figure 22: North America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 23: North America Market Value Share and BPS Analysis by Technology , 2026 and 2036

- Figure 24: North America Market Y-o-Y Growth Comparison by Technology , 2026-2036

- Figure 25: North America Market Attractiveness Analysis by Technology

- Figure 26: North America Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 27: North America Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 28: North America Market Attractiveness Analysis by Application

- Figure 29: North America Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 30: North America Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 31: North America Market Attractiveness Analysis by End Use

- Figure 32: Latin America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 33: Latin America Market Value Share and BPS Analysis by Technology , 2026 and 2036

- Figure 34: Latin America Market Y-o-Y Growth Comparison by Technology , 2026-2036

- Figure 35: Latin America Market Attractiveness Analysis by Technology

- Figure 36: Latin America Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 37: Latin America Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 38: Latin America Market Attractiveness Analysis by Application

- Figure 39: Latin America Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 40: Latin America Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 41: Latin America Market Attractiveness Analysis by End Use

- Figure 42: Western Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 43: Western Europe Market Value Share and BPS Analysis by Technology , 2026 and 2036

- Figure 44: Western Europe Market Y-o-Y Growth Comparison by Technology , 2026-2036

- Figure 45: Western Europe Market Attractiveness Analysis by Technology

- Figure 46: Western Europe Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 47: Western Europe Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 48: Western Europe Market Attractiveness Analysis by Application

- Figure 49: Western Europe Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 50: Western Europe Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 51: Western Europe Market Attractiveness Analysis by End Use

- Figure 52: Eastern Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 53: Eastern Europe Market Value Share and BPS Analysis by Technology , 2026 and 2036

- Figure 54: Eastern Europe Market Y-o-Y Growth Comparison by Technology , 2026-2036

- Figure 55: Eastern Europe Market Attractiveness Analysis by Technology

- Figure 56: Eastern Europe Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 57: Eastern Europe Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 58: Eastern Europe Market Attractiveness Analysis by Application

- Figure 59: Eastern Europe Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 60: Eastern Europe Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 61: Eastern Europe Market Attractiveness Analysis by End Use

- Figure 62: East Asia Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 63: East Asia Market Value Share and BPS Analysis by Technology , 2026 and 2036

- Figure 64: East Asia Market Y-o-Y Growth Comparison by Technology , 2026-2036

- Figure 65: East Asia Market Attractiveness Analysis by Technology

- Figure 66: East Asia Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 67: East Asia Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 68: East Asia Market Attractiveness Analysis by Application

- Figure 69: East Asia Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 70: East Asia Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 71: East Asia Market Attractiveness Analysis by End Use

- Figure 72: South Asia and Pacific Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 73: South Asia and Pacific Market Value Share and BPS Analysis by Technology , 2026 and 2036

- Figure 74: South Asia and Pacific Market Y-o-Y Growth Comparison by Technology , 2026-2036

- Figure 75: South Asia and Pacific Market Attractiveness Analysis by Technology

- Figure 76: South Asia and Pacific Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 77: South Asia and Pacific Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 78: South Asia and Pacific Market Attractiveness Analysis by Application

- Figure 79: South Asia and Pacific Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 80: South Asia and Pacific Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 81: South Asia and Pacific Market Attractiveness Analysis by End Use

- Figure 82: Middle East & Africa Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 83: Middle East & Africa Market Value Share and BPS Analysis by Technology , 2026 and 2036

- Figure 84: Middle East & Africa Market Y-o-Y Growth Comparison by Technology , 2026-2036

- Figure 85: Middle East & Africa Market Attractiveness Analysis by Technology

- Figure 86: Middle East & Africa Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 87: Middle East & Africa Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 88: Middle East & Africa Market Attractiveness Analysis by Application

- Figure 89: Middle East & Africa Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 90: Middle East & Africa Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 91: Middle East & Africa Market Attractiveness Analysis by End Use

- Figure 92: Global Market - Tier Structure Analysis

- Figure 93: Global Market - Company Share Analysis

Full Research Suite comprises of:

Market outlook & trends analysis

Interviews & case studies

Strategic recommendations

Vendor profiles & capabilities analysis

5-year forecasts

8 regions and 60+ country-level data splits

Market segment data splits

12 months of continuous data updates

DELIVERED AS:

PDF EXCEL ONLINE