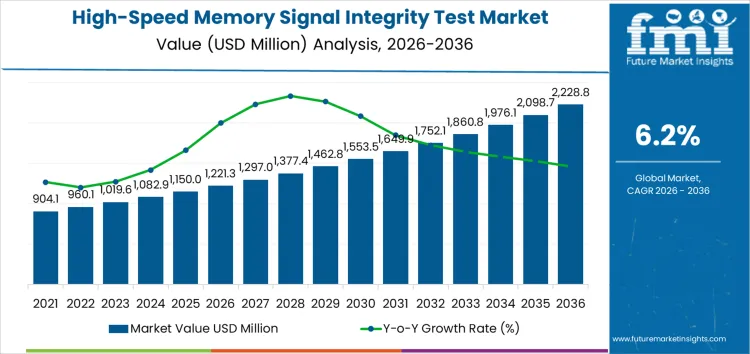

Demand for high-speed memory signal integrity test market is valued at USD 1,221.3 million in 2026 and is forecast to reach USD 2,228.8 million by 2036, expanding at a CAGR of 6.2%. Growth is driven by rapid scaling of DDR5, HBM, GDDR, and emerging memory interfaces supporting AI accelerators, data centers, and advanced networking hardware. Rising data rates, tighter timing margins, and higher channel losses increase dependency on precise signal integrity validation during design, validation, and production stages.

Real-time and sampling oscilloscopes represent the leading instrument class globally. These platforms enable accurate eye-diagram analysis, jitter decomposition, crosstalk evaluation, and channel compliance testing at multi-gigabit speeds. Adoption remains strongest in memory controller validation, interposer-based architectures, and advanced packaging environments where signal degradation directly impacts system yield and performance. Complementary demand exists for vector network analyzers, bit error rate testers, and protocol-aware analysis software supporting comprehensive electrical characterization.

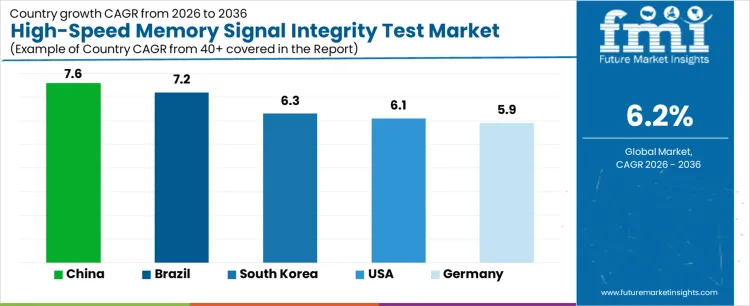

China, Brazil, South Korea, USA, and Germany rank among fastest-growing countries, supported by semiconductor manufacturing expansion and memory-intensive compute deployments. Competitive landscape is led by Keysight Technologies, Rohde & Schwarz, Tektronix, Anritsu, and Teledyne LeCroy. Market structure reflects sustained reliance on high-bandwidth, low-noise instrumentation aligned with evolving memory interface standards.

| Metric | Value |

|---|---|

| Market Value (2026) | USD 1,221.3 million |

| Market Forecast Value (2036) | USD 2,228.8 million |

| Forecast CAGR (2026-2036) | 6.2% |

Demand for high-speed memory signal integrity test solutions is growing globally due to increasing complexity and performance requirements of modern computing systems. Memory technologies such as DDR, LPDDR, HBM, and GDDR operate at higher frequencies and tighter timing margins, which elevates sensitivity to signal degradation, crosstalk, and reflection effects. Semiconductor developers and system integrators require advanced test equipment to validate memory channel performance, timing accuracy, and error rates prior to production. Growth in data center compute, artificial intelligence, machine learning, and edge computing workloads intensifies pressure on memory subsystems to deliver sustained throughput with minimal latency.

Test platforms that provide high fidelity analysis of jitter, eye diagrams, and impedance profiles support design optimization and yield improvement across diverse architectures. Global adoption of next generation protocols and interface standards encourages standardized signal integrity validation practices across supply chains. Equipment suppliers deliver scalable solutions that integrate with automated test environments and support multi-channel evaluation. Research institutions and advanced packaging facilities invest in test systems to enhance understanding of high speed interconnect behavior and material impact. Demand is sustained by focus on reliability, performance consistency, and compliance with emerging signal integrity benchmarks across computing industries worldwide.

Demand for high-speed memory signal integrity test solutions globally is shaped by rising data rates, tighter timing margins, and complex interconnect architectures. Stakeholders assess bandwidth capability, jitter tolerance, measurement accuracy, and correlation across lab and production environments. Adoption patterns reflect validation needs for advanced memory interfaces across silicon development, system integration, and large-scale compute deployments requiring consistent signal performance.

Real-time or sampling oscilloscopes hold 34.0%, accounting for the largest share of global demand. These instruments enable time-domain visibility of eye diagrams, jitter components, and transient behavior at high speeds. BERTs or pattern generators hold 28.0%, supporting bit error analysis and stress testing under controlled impairment conditions. TDR and S-parameter tools account for 22.0%, enabling impedance characterization and channel loss assessment. Probing, fixtures, and software hold 16.0%, supporting accurate signal access and analysis workflows. Instrument distribution reflects priority for direct waveform observation in signal integrity validation.

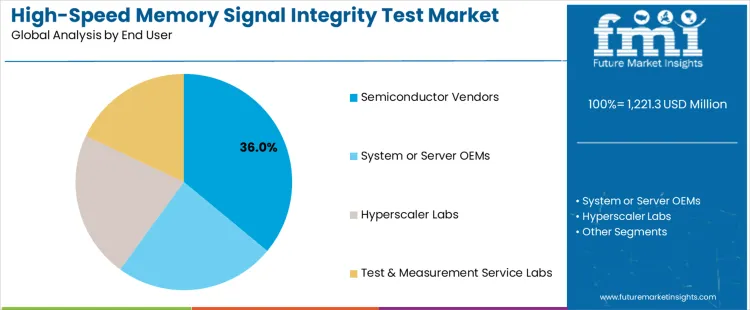

Semiconductor vendors hold 36.0%, driving the highest global demand. These organizations validate memory PHY performance, compliance, and margin during silicon development and characterization. System or server OEMs hold 24.0%, supporting platform-level signal integrity across boards and interconnects. Hyperscaler labs account for 22.0%, validating high-speed memory performance within large-scale compute architectures. Test and measurement service laboratories hold 18.0%, providing third-party validation and overflow testing capacity. End-user distribution reflects concentration of signal integrity responsibility within silicon development and system integration environments.

Global demand rises as semiconductor manufacturers, system integrators, and test service providers adopt advanced signal integrity (SI) test solutions to ensure reliability and performance of high-speed memory interfaces in servers, AI accelerators, mobile devices, and networking equipment. Memory standards such as DDR5, HBM, LPDDR, and emerging next-generation protocols impose stringent timing, crosstalk, and reflection constraints. Adoption aligns with increasing adoption of high-performance computing, data center acceleration, and edge computing platforms worldwide.

How do memory performance requirements and interface scale drive global demand?

High-speed memory systems require precise characterization of signal timing, bit error rates, channel losses, and electromagnetic interference under operational conditions. Manufacturers use SI test platforms to validate trace-length effects, material dielectric loss, and connector integrity across high-frequency bands. Test solutions integrate vector network analysis, eye-diagram evaluation, and time-domain reflectometry to isolate distortion sources. System designers evaluate memory subsystem performance within multi-die packages and heterogeneous computing architectures where margin requirements are tight. OEMs and foundries invest in automated test benches capable of high-throughput measurements that support qualification and yield improvement efforts across global supply chains.

How do capital intensity, standard fragmentation, and engineering complexity influence market scalability?

High-speed memory SI test equipment entails substantial investment in precision instruments, calibration standards, and controlled fixture environments. Fragmentation among memory standards requires adaptable test platforms that support multiple protocols and evolving specifications, increasing development workload. Engineering expertise in electromagnetic modelling, statistical analysis, and fixture design is essential to interpret results, extending test cycle durations. Regional disparities in access to high-end labs concentrate advanced capability within major semiconductor hubs, while smaller developers rely on shared facilities or outsourcing. Coordination with standards bodies and ecosystem partners adds complexity to test planning. Long-term growth depends on development of modular, scalable SI test solutions and alignment of global testing frameworks that reduce fragmentation and lower barriers for next-generation memory validation worldwide.

Demand for high-speed memory signal integrity test systems is increasing globally due to higher data rates, tighter timing margins, and advanced packaging adoption. China leads with a 7.6% CAGR, supported by domestic semiconductor expansion and memory interface development. Brazil follows at 7.2%, driven by academic research and emerging electronics validation needs. South Korea records a 6.3% CAGR, shaped by DRAM and NAND leadership and precision characterization requirements. USA posts 6.1%, reflecting platform refresh cycles and next-generation compute systems. Germany records 5.9%, supported by automotive electronics and industrial computing standards. Growth reflects escalating signal speeds, complexity of interconnects, and necessity for repeatable integrity validation worldwide.

| Country | CAGR (%) |

|---|---|

| China | 7.6% |

| Brazil | 7.2% |

| South Korea | 6.3% |

| USA | 6.1% |

| Germany | 5.9% |

China drives demand through rapid expansion of semiconductor manufacturing, advanced packaging, and high-speed interface development. Country’s CAGR of 7.6% reflects extensive testing of DDR, HBM, and GDDR interfaces across design and validation stages. Engineers validate eye diagrams, jitter, crosstalk, and channel loss under real operating conditions. In-house labs scale capacity to shorten design cycles and protect intellectual property. Test platforms emphasize bandwidth, automation, and correlation with simulation. Government-backed programs expand access to advanced instrumentation. Growth remains scale-driven and investment-led, aligned with domestic semiconductor capability buildout.

Brazil demand is shaped by growth in electronics research, embedded systems development, and university-led validation programs. Country’s CAGR of 7.2% reflects increasing use of signal integrity test systems for memory interfaces in networking, defense, and computing research. Shared laboratories enable cost-efficient access to high-bandwidth oscilloscopes and probes. Collaboration with international vendors supports adoption of standard test methodologies. Demand favors modular platforms suitable for mixed research workloads. Growth remains capability-building focused, aligned with gradual strengthening of domestic electronics design and validation competence.

South Korea demand reflects global leadership in DRAM and NAND manufacturing and advanced packaging. Country’s CAGR of 6.3% is supported by intensive signal integrity validation across process nodes and product generations. Manufacturers emphasize precision timing analysis, channel modeling, and correlation with silicon yield. Automated test flows support high-volume validation. Government-backed initiatives promote standardized characterization. Growth remains process-driven, aligned with aggressive performance scaling and reliability targets across memory portfolios.

USA demand is driven by platform refresh cycles, AI and HPC systems, and server memory upgrades. Country’s CAGR of 6.1% reflects validation of next-generation memory standards and complex board designs. Test systems support compliance, debug, and optimization across development stages. Integration with simulation and design tools improves correlation. Procurement emphasizes bandwidth, accuracy, and workflow efficiency. Growth remains lifecycle-driven, aligned with system upgrades and evolving compute architectures.

Germany demand reflects automotive electronics, industrial computing, and stringent reliability standards. Country’s CAGR of 5.9% is supported by testing memory interfaces used in vehicles, factories, and edge systems. Test platforms validate signal integrity under temperature variation, vibration, and long lifetimes. Shared research institutes expand access to advanced instrumentation. Procurement favors documentation, repeatability, and standards alignment. Growth remains engineering-led, aligned with safety, durability, and compliance requirements across industrial applications.

Demand for high-speed memory signal integrity test platforms is driven by scaling of DDR5, HBM, GDDR, and emerging memory architectures used in AI accelerators and high-performance computing systems. Validation workflows focus on eye diagram integrity, jitter tolerance, crosstalk behavior, insertion loss, and timing margin analysis at multi-gigabit data rates. Buyers prioritize bandwidth headroom, low intrinsic noise, calibration traceability, and protocol-aware measurement capability across development and qualification stages. Procurement teams assess automation readiness for compliance testing, correlation between lab and production measurements, and reliability under sustained high-speed operation. Trend in the global market reflects shrinking timing budgets, higher channel losses, and tighter integration between electrical characterization and system-level validation.

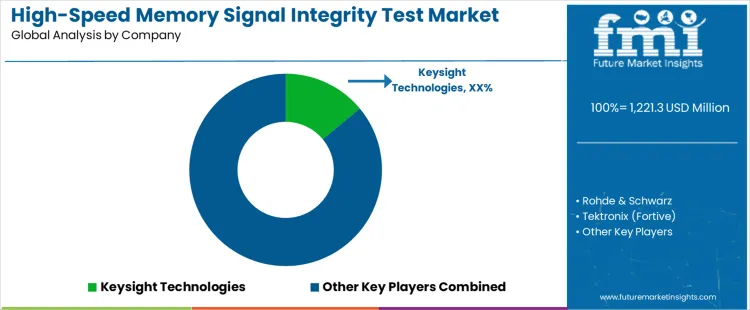

Keysight Technologies holds strong positioning through high-bandwidth oscilloscopes, BERT systems, and memory-aware analysis software supporting advanced memory standards. Rohde & Schwarz and Anritsu supply low-jitter signal generation and analysis platforms used for transmitter and receiver stress testing. Tektronix, part of Fortive, and Teledyne LeCroy support signal integrity debugging with real-time scopes emphasizing deep memory and timing analysis. National Instruments, operating under Emerson, provides modular PXI-based platforms enabling automated signal integrity workflows. Advantest integrates memory characterization within semiconductor test ecosystems, while VIAVI Solutions, Spirent Communications, and EXFO contribute interconnect, link, and channel validation tools. Competitive differentiation depends on measurement fidelity, automation depth, protocol coverage, and cross-platform correlation consistency.

| Items | Values |

|---|---|

| Quantitative Units | USD million |

| Instrument Class | Real-Time or Sampling Oscilloscopes; BERTs or Pattern Generators; TDR and S-Parameter Measurement Tools; Probing Solutions, Fixtures, and Signal Integrity Software |

| End User | Semiconductor Vendors; System or Server OEMs; Hyperscaler and Cloud Data Center Labs; Independent Test and Measurement Service Laboratories |

| Regions Covered | Asia Pacific; Europe; North America; Latin America; Middle East & Africa |

| Countries Covered | China; Brazil; South Korea; USA; Germany; and 40+ countries |

| Key Companies Profiled | Keysight Technologies; Rohde & Schwarz; Tektronix; Anritsu; Teledyne LeCroy; National Instruments (Emerson); Advantest; VIAVI Solutions; Spirent Communications; EXFO |

| Additional Attributes | Dollar sales by instrument class and end-user category; regional adoption trends across advanced semiconductor fabs and hyperscaler labs; validation demand for DDR5, HBM, and PCIe interfaces; increased automation in signal integrity compliance testing; growing use of software-driven analysis tools. |

How big is the high-speed memory signal integrity test market in 2026?

The global high-speed memory signal integrity test market is estimated to be valued at USD 1,221.3 million in 2026.

What will be the size of high-speed memory signal integrity test market in 2036?

The market size for the high-speed memory signal integrity test market is projected to reach USD 2,228.8 million by 2036.

How much will be the high-speed memory signal integrity test market growth between 2026 and 2036?

The high-speed memory signal integrity test market is expected to grow at a 6.2% CAGR between 2026 and 2036.

What are the key instrument class types in the high-speed memory signal integrity test market?

The key instrument class types in high-speed memory signal integrity test market are real-time or sampling oscilloscopes, berts or pattern generators, tdr & s-parameter tools and probing, fixtures & software.

Which end user segment to contribute significant share in the high-speed memory signal integrity test market in 2026?

In terms of end user, semiconductor vendors segment to command 36.0% share in the high-speed memory signal integrity test market in 2026.

Full Research Suite comprises of:

Market outlook & trends analysis

Interviews & case studies

Strategic recommendations

Vendor profiles & capabilities analysis

5-year forecasts

8 regions and 60+ country-level data splits

Market segment data splits

12 months of continuous data updates

DELIVERED AS:

PDF EXCEL ONLINE

Thank you!

You will receive an email from our Business Development Manager. Please be sure to check your SPAM/JUNK folder too.