Chiplet Integration and Die-to-Die Interconnect Test Solutions Market

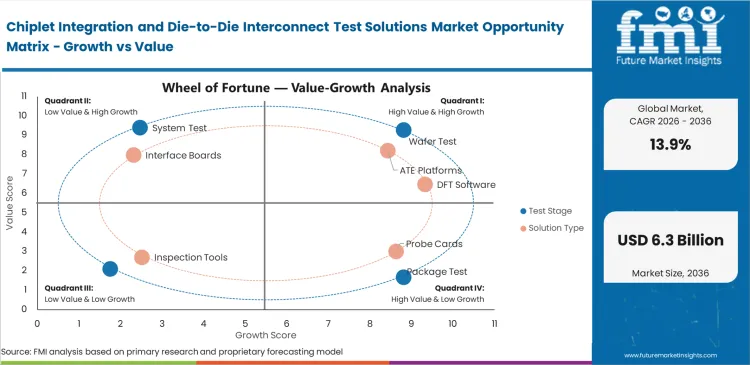

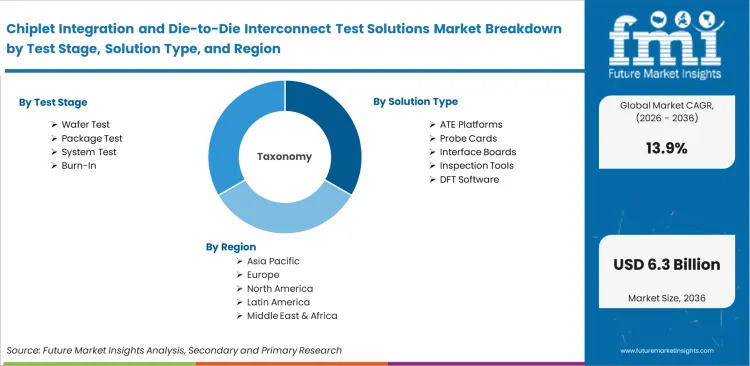

The chiplet integration and die-to-die interconnect test solutions market is segmented by Test Stage (Wafer Test, Package Test, System Test, Burn-In), Solution Type (ATE Platforms, Probe Cards, Interface Boards, Inspection Tools, DFT Software), Interconnect Type (UCIe, Proprietary Links, TSV Links, Bridge Links), Package Architecture (2.5D Packages, 3D Stacks, Fan-Out, SiP Modules), End User (IDMs, Foundries, OSATs, Fabless Firms), and Region. Forecast for 2026 to 2036.

Historical Data Covered: 2016 to 2024 | Base Year: 2025 | Estimated Year: 2026 | Forecast Period: 2027 to 2036

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Size, Market Forecast and Outlook By FMI

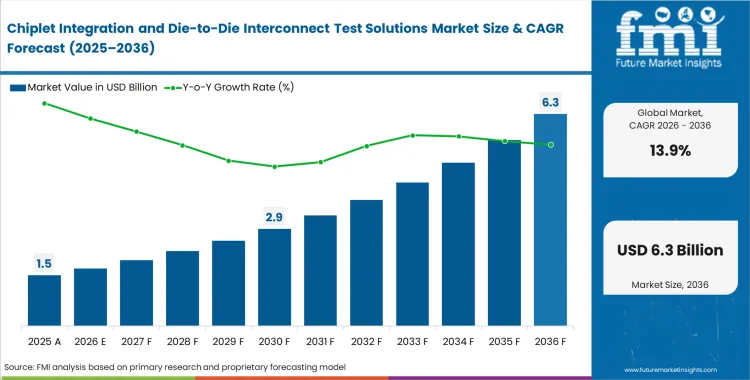

The chiplet integration and die-to-die interconnect test solutions market was valued at USD 1.3 billion in 2025. Demand is estimated to hit USD 1.5 billion in 2026 at a CAGR of 13.9% during the forecast period. The total valuation is expected to reach USD 5.5 billion through 2036, as yield economics dictate mandatory known good die testing for chiplets prior to final heterogeneous assembly.

Yield architects at tier-one foundries face significant challenges in mitigating defect escapes during testing of AI accelerator chiplet designs. A single defective logic block integrated into a high-density package can result in the loss of high-value silicon and advanced substrate materials. Rather than expanding capacity, procurement teams must invest in advanced X-ray CT inspection systems capable of evaluating sub‑40‑micron micro-bumps without compromising delicate interconnects. Delays in upgrading test capabilities expose operations teams to cascading yield losses that can materially erode margins on premium products. Conventional diagnostic methods are increasingly ineffective at these densities, requiring yield management strategies to be restructured around rigorous die-to-die compliance protocols.

Summary of Chiplet Integration and Die-to-Die Interconnect Test Solutions Market

- Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Definition:

- Specialized hardware and software validating communication bridges between independent silicon dies. This infrastructure proves critical for identifying defects before final assembly, protecting high-value logic and substrate investments from cascading failures.

- Demand Drivers in the Market:

- Yield protection economics compel packaging operations managers to implement pre-assembly screening utilizing chiplet test equipment.

- Substrate complexity forces interconnect designers to embed specialized test logic within bridging circuits.

- Interoperability standards push fabless verification teams to acquire compliant protocol validation platforms.

- Key Segments Analyzed in the FMI Report:

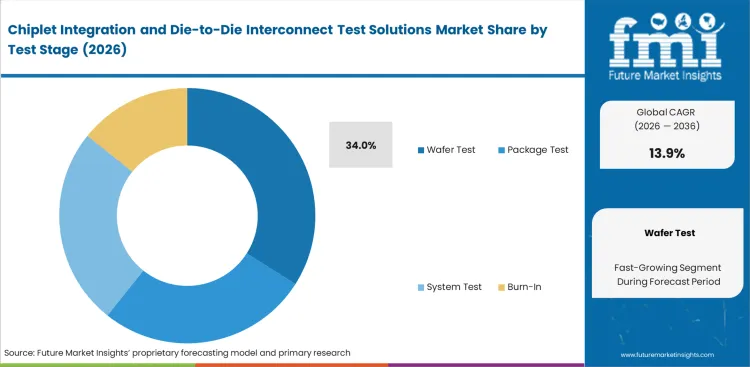

- Wafer Test is estimated to hold 34.0% share in 2026, driven by defect identification economics preceding expensive packaging steps.

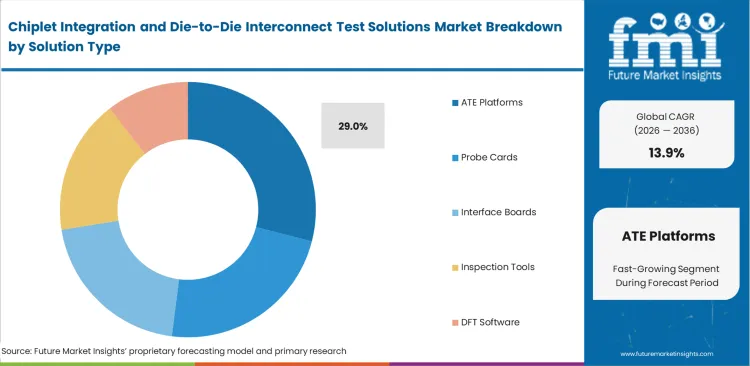

- ATE Platforms is expected to lead by Solution Type, absorbing massive signal volumes generated by high-density heterogeneous configurations.

- UCIe is projected to capture 41.0% share in 2026, supported by dominant intellectual property consortium standardization efforts.

- 2.5D Packages is set to command 38.0% share in 2026, reflecting massive deployment in server accelerator module designs.

- IDMs is anticipated to retain 37.0% share in 2026, leveraging closed-loop internal supply chains for rapid test qualification.

- Taiwan: Taiwan registers 15.4% compound growth, anchored by dominant global foundry testing ecosystems and advanced substrate concentration.

- Analyst Opinion at FMI:

- Rahul Pandita, Principal Analyst, Technology, at FMI, points out, "Test operations directors assume standard fault coverage metrics perfectly translate to heterogeneous architectures. In reality, thermal density during concurrent die testing creates false failures that traditional metrics completely miss. Generalists focus on contact pitch shrinking, but actual practitioners understand thermal dissipation inside the test socket dictates throughput speed. Facilities upgrading probe cards without simultaneously overhauling their active thermal control infrastructure immediately bottleneck their entire high-performance compute production lines."

- Strategic Implications / Executive Takeaways:

- Procurement directors face immediate vendor lock-in risks selecting non-standard proprietary bridge validation frameworks.

- Yield architects must overhaul diagnostic software workflows before integrating next-generation memory stacks.

- Fab managers gain significant margin protection by deploying active thermal control mechanisms during wafer-level screening.

- Methodology:

- Baseline sizing models capture deployed advanced packaging capacity matched to explicit chiplet adoption roadmaps. Primary input streams trace capital expenditure flows from leading test equipment vendors straight into foundry qualification laboratories.

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Key Takeaways

| Metric | Details |

|---|---|

| Industry Size (2026) | USD 1.5 billion |

| Industry Value (2036) | USD 5.5 billion |

| CAGR (2026 to 2036) | 13.9% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Standardization through the Universal Chiplet Interconnect Express (UCIe) is transforming test workflows. As UCIe matures across major IP portfolios, design teams are moving away from proprietary verification scripts. This shift enables test equipment vendors to deliver unified software platforms that natively recognize standardized link architectures, improving efficiency and interoperability across the ecosystem.

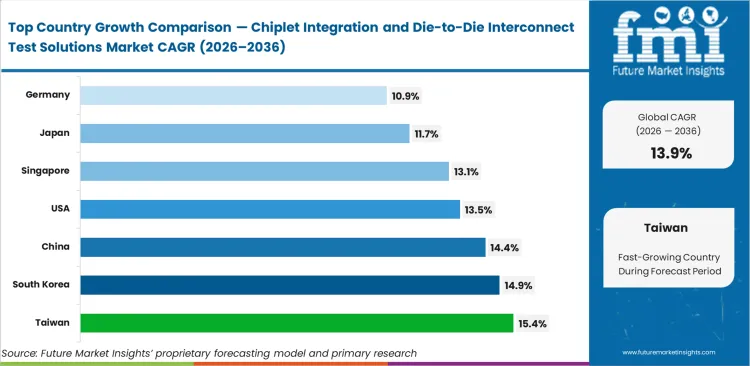

Taiwan leads the chiplet test forecast 2036 growth at 15.4%, as concentrated packaging ecosystems prioritize high-density interconnect validation. South Korea tracks at 14.9% CAGR, driven by extreme memory stacking requirements, while China maintains 14.4% CAGR, backing domestic capacity buildouts. United States engineering centers expand at 13.5% CAGR, demanding tight architectural compliance tools. Singapore advances at 13.1% CAGR on outsourced assembly volume. Japan scales at 11.7% CAGR, and Germany grows at 10.9% CAGR, supporting specialized industrial electronics. Structural divergence occurs primarily between regions controlling leading-edge substrate fabrication versus locations handling standard semiconductor metrology and inspection volume.

Segmental Analysis

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis by Test Stage

The critical role of early defect detection determines the manner in which the operations managers control the capital expenditures before the substrate attachment. The wafer test holds a 34.0% market share in 2026 due to the critical nature of discovering a defective interconnect micro-bump, which prevents costly functioning chiplets from being integrated into a complicated module, thus destroying margin potential. The yield architects at the outsourced assembly facilities heavily rely on this specific screening phase of the entire chiplet test flow, from wafer to package, in order to ascertain the known good die. The FMI evaluation reveals that the figure actually underestimates the firm’s intrinsic valuation due to the massive capital expenditures on proprietary pre-assembly probing, which often go unnoticed in capital equipment reporting. Test engineering directors implementing 3D IC and 25D IC packaging formats require absolute certainty regarding bump coplanarity and electrical continuity. Skipping rigorous wafer-level semiconductor bonding validation forces companies to scrap fully assembled premium accelerators later in the manufacturing cycle.

- Defect containment priority: Capturing signal failures prior to permanent bonding prevents multi-die yield collapse. Yield architects at outsourced assembly facilities protect baseline profitability by expanding active probe arrays.

- Micro-bump physical limits: Shrinking contact pad dimensions challenge mechanical alignment tolerances during initial touch. Test engineers face constant socket maintenance cycles protecting delicate interface tips from rapid degradation.

- Scrap cost avoidance: Discarding a bare die costs fractions compared to scrapping fully integrated modules. Procurement directors underinvesting in wafer screening inevitably destroy unit economics downstream.

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis by Solution Type

The necessity of signal density requirements forces test facility managers to use a centralized processing strategy. ATE platforms segment accounts for share of 29.0% in 2026 due to their unique ability to process thousands of interconnect channels at high speeds. Engineers configuring system configurations use massive platforms to synchronize timing patterns between vastly different silicon nodes that share a single substrate. Test directors at premium fabrication companies understand that these are long-term foundation platforms. FMI analysts note that relying exclusively on platform share obscures a critical reality regarding consumable tooling: advanced packaging destroys probe cards at unprecedented rates, shifting actual lifecycle spend away from mainframes toward replaceable interface components. Test operators who use the wrong platforms experience massive data bottlenecks during complex concurrent test execution. This forces procurement to repeatedly consult the best chiplet test companies to upgrade platforms.

- Concurrent execution requirement: Managing parallel test sequences across heterogeneous nodes demands extreme processing bandwidth. System configuration engineers minimize test duration by optimizing centralized vector distribution.

- Pattern memory exhaustion: Complex heterogeneous designs quickly overwhelm legacy platform storage capacities. Facilities managers must upgrade internal memory subsystems to avoid splitting verification into multiple physical passes.

- Platform transition timing: Replacing legacy mainframes demands extensive software migration planning. Operations directors delaying upgrades face severe capacity constraints handling modern high-pin-count interconnect modules.

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis by Interconnect Type

The alignment with intellectual property guides the way in which fabless design teams specify testing infrastructure. UCIe holds a 41.0% market share in 2026, as broad industry consortium backing establishes it as a baseline standard for heterogeneous integration. The standardized protocol is utilized by silicon validation engineers to deploy automated diagnostic routines without requiring software wrappers to be written. Massive engineering overhead is eliminated with standardization in testing for UCIe compliance. Protocol standardization presents an unacknowledged blind spot according to FMI's analysis: universal specification compliance masks subtle timing variations introduced by different 3D TSV packages suppliers, leading to mysterious field failures despite passing standard factory tests. Fabless procurement teams not adhering to standardized UCIe test solutions market protocols face a brutal form of vendor lock-in.

- Automated Routine Generation: Awareness of standardized protocols enables instantaneous generation of test patterns across different foundries. Silicon validation engineers speed up tape-out cycles by eliminating manual script writing.

- Compliance Corner Cases: Complex state machines are a part of standardized protocols, which often result in deadlocks during edge cases. Verification leads face difficulties in catching transient physical layer issues occurring deep within standard compliance testing.

- Cross-Vendor Interoperability: Ensuring communication between chiplets of different origins mandates absolute physical layer compliance. Teams not adhering to strict compliance certification face immediate rejection from tier-one integrator supply chains.

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis by Package Architecture

Thermal density physics plays a major role in dictating testing restrictions on specific module types. 2.5D packages segment hold a 38.0% share in 2026, primarily used to deploy massive artificial intelligence accelerators that require extreme levels of memory bandwidth. Integration experts rely on testing to ensure communication between logic and memory layers on sensitive silicon interposers. Hardware architects in high-performance computing environments rely on complete interposer integrity to ensure design bandwidth targets. Operations missing critical signal degradation metrics on wafer level packaging ship defective compute modules to critical data center clients, accelerating demand for highly specialized 2.5D package test solutions and precise HBM package testing cells.

- Interposer signal integrity: Validating massive parallel routing across silicon interposers demands extreme high-speed instrumentation. Integration specialists capture subtle cross-talk interference patterns destroying theoretical memory bandwidth limits.

- Thermal socket limitations: High-power modules generate massive heat during full concurrent testing cycles. Socket designers fight continuous battles balancing precise electrical contact against aggressive liquid cooling requirements.

- End-of-line yield impact: Silicon interposer failures discovered after final encapsulation destroy thousands of dollars in known-good logic. Production directors deploying insufficient 2.5D test coverage immediately ruin quarterly margin projections.

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis by End User

The benefits of closed-loop feedback loops are enormous in operation during complex technology shifts. DMs segment lead with 37.0% share in 2026 because controlling both design architecture and final test execution allows rapid iteration of die-to-die compliance protocols. The yield optimization directors of these vertical organizations are capable of using their own exclusive diagnostic feedback loops that are completely impossible for fragmented supply chains. According to FMI research, the market share leadership of IDMs conceals a critical weakness: semiconductor and IC packaging materials testing groups within these organizations often experience extreme insular blind spots that cannot accommodate rapid adaptation as the rest of the industry consensus shifts to alternative open-source bridging solutions. Fabless organizations that solely depend on third-party testing services will experience extended debugging times due to initial phase failure of their isolated chiplet package testing strategy. Additionally, the complexity of fan-out wafer level packaging solutions demands unique handling techniques that are challenging for captive testing services to deploy.

- Vertical loop optimization: Tight coupling between internal design and test teams accelerates diagnostic learning curves. Yield optimization directors push precise failure analysis directly back to physical layout engineers.

- Capital expenditure burden: Supporting bleeding-edge packaging evaluation requires massive, continuous equipment investments. Financial officers at mid-tier integrated manufacturers struggle justifying dedicated advanced packaging testers for low-volume product lines.

- External ecosystem isolation: Captive testing facilities risk missing efficiency breakthroughs developed in the open foundry market. Strategy vice presidents isolating their test operations gradually lose cost competitiveness against agile fabless networks.

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Drivers, Restraints, and Opportunities

Economics of Yield Protection forces operations directors of assembly facilities to be very rigorous in their known good die validation processes before committing their components to advanced packaging structures. High-performance computing architectures require several costly logic and memory devices to be placed on a single substrate, and the financial penalty of a single interconnect failure can be exponentially costly. The operations director cannot afford to discard a fully assembled premium accelerator due to a microscopic bridge defect. The financial pressure is immediate procurement of high-density probing systems. Delaying these semiconductor packaging test equipment upgrades guarantees unacceptable end-of-line yield collapse.

Contact pad pitch shrinking is growing at a much higher rate than the capability of micro-electromechanical manufacturing for probe cards. The test operation managers face a hard limit in their efforts to place thousands of microscopic physical probes onto extremely fragile silicon interfaces without causing damage. This mechanical contact friction creates massive bottlenecking as semiconductor bonding equipment resolutions advance past physical testing limits. Interface tooling suppliers currently attempt using sacrificial conductive layers, but high-volume production requirements quickly degrade these temporary solutions.

Opportunities in the Chiplet Integration and Die-to-Die Interconnect Test Solutions Market

- Contactless probe architectures: Radio frequency inductive coupling replaces mechanical touch downs. Test operations managers eliminate pad damage completely, accelerating testing throughput across delicate interface structures.

- Standardized IP compliance toolkits: Pre-packaged software verification suites target specific universal chiplet protocols. Fabless verification engineers utilize these tools to guarantee flip chip interfaces communicate flawlessly before physical tape-out.

- Stacked architecture simulation: Engineers adopting sophisticated 3D IC interconnect test equipment isolate thermal hotspots earlier. Production floor supervisors maintain high testing throughput without triggering artificial thermal shutdown events.

Regional Analysis

Based on regional analysis, the chiplet integration and die-to-die interconnect test solutions market is segmented into North America, Europe, Asia Pacific, Latin America, and Middle East & Africa across 40 plus countries.

.webp)

| Country | CAGR (2026 to 2036) |

|---|---|

| Taiwan | 15.4% |

| South Korea | 14.9% |

| China | 14.4% |

| United States | 13.5% |

| Singapore | 13.1% |

| Japan | 11.7% |

| Germany | 10.9% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Asia Pacific Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis

Extreme concentration of advanced substrate fabrication dictates testing capital deployment strategy in Asia Pacific. Foundries and outsourced assembly houses collocate massive evaluation labs adjacent to cleanrooms, eliminating wafer transport delays. Operations directors exploit extreme regional clustering to quickly develop new micro bump probing technology. FMI recognizes that raw regional volume metrics do not capture a critical qualitative shift in the market: the top Asian fabrication facilities refuse to qualify secondary outsourced assembly houses for ultra-dense module validation, thus confining the highest margin thin wafers integration test work to a handful of elite captive facilities.

- Taiwan: Taiwan is expected to grow at a CAGR of 15.4%, with the country benefiting from a dense and highly integrated semiconductor foundry ecosystem. The ecosystem requires the rapid deployment of high-density interconnect validation platforms, with key vendors in the Taiwan chiplet test solutions market driving innovation in this space. The key strength in Taiwan is the country’s ability to leverage advanced manufacturing capabilities with dedicated testing infrastructure, ensuring chiplet packaging and interconnect systems meet the high standards set by global customers. The growth trend in Taiwan highlights the country’s importance in the next-generation semiconductor validation and reliability assurance ecosystem.

- South Korea: Suppliers in South Korea are using their close relationship with memory OEMs to stay at the forefront in advanced testing, further cementing the country’s position at the heart of the evolution of semiconductors. The market in South Korea is growing at a CAGR of 14.9%, driven by the preeminence of the country’s memory manufacturers. They are helping to define the limits of performance by demanding extreme high-bandwidth module screening. This is accomplished by developing customized test cells that meet the unique demands of specific product architectures. The focus is on precision, scalability, and speed to ensure that high-capacity memory modules meet exacting standards for quality and reliability.

- China: China is rising at a CAGR of 14.4%, with massive investments in terms of capital by the state to attain packaging independence in China. The focus is on strategic initiatives to attain this, which in turn results in a high equipment purchase cycle to grow the packaging and testing infrastructure in China. The growth curve shows China's commitment to ensuring sustainability in terms of semiconductor packaging, with strategic initiatives by the state to guarantee accelerated growth in this sector.

- Singapore: The key focus area in these centers is to optimize the processes to ensure maximum efficiency, speed, and cost-effectiveness in the standardized chiplet packages. Currently, the semiconductor test solution industry in Singapore is growing at a CAGR of 13.1%, mainly due to the high volume outsourced assembly centers in the country. The strength of the country is in streamlining the processes to deliver high volume output, which is in high demand in the international industry. The country is able to reinforce this by ensuring standardized processes in the industry.

- Japan: The suppliers in Japan use their established manufacturing environments and capabilities in research to provide incremental improvements in substrate design and testing. The approach taken by Japan focuses on precision, refinement, and reliability, which makes Japan a vital player in the global semiconductor supply chain, providing specialized and high-quality solutions. Japan is growing at a CAGR of 11.7%, driven by its expertise in the study of specialized substrate materials. This involves a very precise analytical probing environment, which is needed to satisfy the high requirements of new-generation semiconductor packages.

FMI's report includes emerging Southeast Asian assembly hubs scaling baseline heterogeneous packaging capabilities. Capacity constraints at primary foundries push secondary testing volumes into these adjacent geographies.

North America Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis

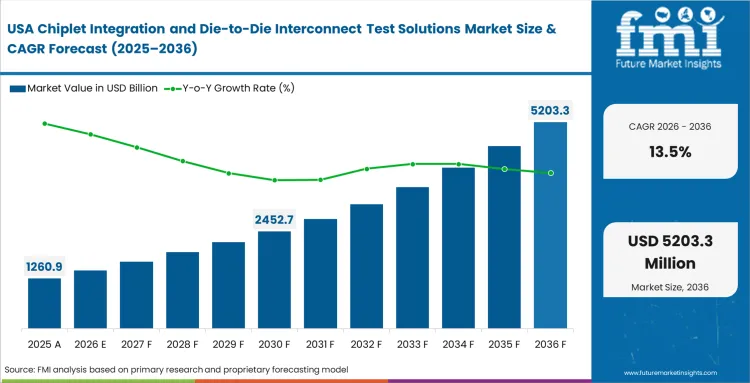

Silicon design centers developing high-end artificial intelligence accelerators require extreme high-fidelity simulation and screening tools. Verification engineers in these design centers define the compliance metrics to be executed eventually by the offshore factories. Estimated by FMI, design phase verification approaches introduce "blind spots" in physical socket constraints on the factory floor, often resulting in severe friction between domestic architects and offshore semiconductor foundry providers in initial production ramps.

- United States: The country’s position as a leader in high-performance computing, where scalability and interoperability are critical to sustaining the market position. This makes U.S. suppliers well-poised to deliver robust compliance platforms that are reliable, efficient, and globally standardized, thereby cementing their position as a cornerstone for next-generation semiconductor design. The market in the United States is expected to grow at a CAGR of 13.5%, because of the need to achieve tighter architectural compliance. This is because high-performance compute architectures require platforms that enforce strict universal protocol compliance, especially within massively parallel design environments.

FMI's report includes Canadian design centers expanding specialized protocol validation capabilities. Local engineering teams secure niche contracts supporting proprietary accelerator bridge development.

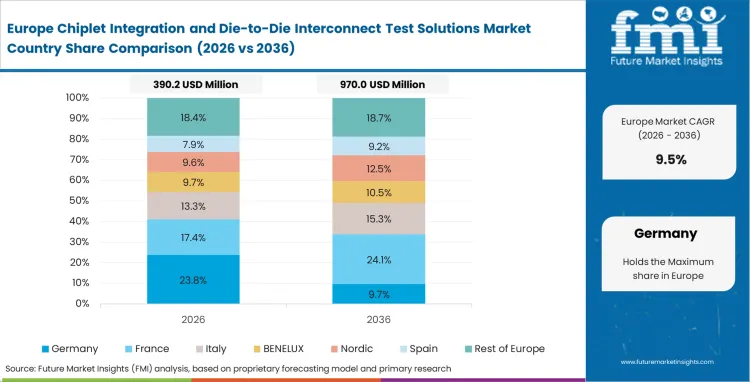

Europe Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis

Industrial electronic components and specialized automotive sensing module test items are driving investment decisions within European regions. Semiconductors are heavily integrating disparate sensor and logic chiplets that require specialized mixed-signal probing capabilities. Operations directors who manage automotive qualification flows are adapting chiplet test hardware to support brutal reliability requirements. From FMI's point of view, European facility managers are prioritizing defect screen test equipment that simulates extreme environmental stresses across quantum computing architectures, largely ignoring raw bandwidth race issues within consumer electronics segments.

- Germany: Germany is able to reinforce its position in the world marketplace with respect to precision in automotive electronics and semiconductor reliability assurance. Germany’s industry is expected to grow at a CAGR of 10.9%, primarily due to the country’s focus on precision in integrating automotive sensors. The growth pattern is influenced by the fact that the automotive industry requires extreme high reliability interconnect testing, especially when subjected to thermal stress. German suppliers are utilizing their expertise in engineering to provide testing environments where the sensors have the precision, reliability, and safety to operate in extreme conditions.

FMI's report includes specialized European research hubs driving early standardization for photonic-to-electronic die bridges. These centers establish critical optical probing protocols ahead of broad commercial deployment.

Latin America Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis

Expansion in Brazil and Mexico of outsourced semiconductor assembly and testing services fuels upgrades in regional capability. Facilities managers in these regions focus on standard package testing platforms to serve the supply chain for consumer electronics rather than incurring the upfront cost to acquire bleeding-edge heterogeneous integration cells. Engineers modify existing testing infrastructure to accommodate initial system-in-package validation protocols.

Middle East & Africa Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis

Technology diversification schemes in GCC states by their governments launch investments in the early stages of the semiconductor ecosystem. Procurement directors in these states establish foundational integrated circuit validation capabilities to serve as a foundation for future micro-bump screening integration. Testing strategies in these states are primarily based on establishing foundational high-speed diagnostic reliability.

Competitive Aligners for Market Players

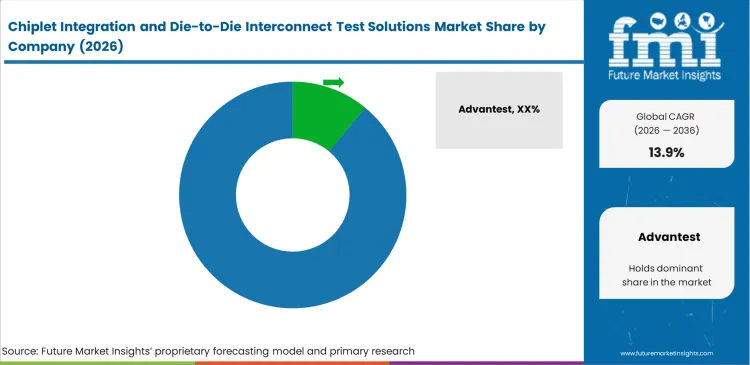

Dominant automated test equipment suppliers maintain intense concentration by leveraging massive installed bases of core mainframes. Competitors struggle attempting to displace legacy systems because fab managers refuse to scrap perfectly functional platforms just to evaluate new computer microchips validation hardware. Major players like Advantest and Teradyne dictate transition cycles by slowly releasing specialized chiplet instrumentation cards perfectly backward-compatible with existing factory infrastructure. Procurement directors overwhelmingly choose this evolutionary upgrade path, effectively blocking new entrants attempting to sell revolutionary but incompatible standalone screening systems. Current chiplet test market trends indicate consolidation will only accelerate as interface complexity deepens.

Incumbent interface suppliers control access to vital micro-electromechanical fabrication capabilities. Producing functional probe arrays at sub-40-micron pitches requires specialized wafer batch aligner systems and deeply guarded material science intellectual property. Challengers must build cleanroom manufacturing expertise from scratch, attempting to match incumbent pricing on highly consumable interface boards. Test operations directors aggressively audit supplier cleanroom capabilities, actively screening out vendors lacking redundant manufacturing sites capable of supporting massive surge volumes during product ramps.

Large foundries resist testing ecosystem lock-in by forcing competing equipment vendors into strict interoperability consortiums. Facilities architects refuse to implement proprietary semiconductor wafers throughput communication links between testers and handlers, demanding open API access for custom data extraction. Market competition revolves entirely around providing software transparency; hardware capability simply represents the entry baseline. Leading design automation firms secure dominant positions by ensuring their diagnostic software hooks flawlessly into every major hardware platform available.

Key Players in Chiplet Integration and Die-to-Die Interconnect Test Solutions Market

- Advantest

- Teradyne

- FormFactor

- Cohu

- Chroma ATE

- Synopsys

- Siemens EDA

Scope of the Report

| Metric | Value |

|---|---|

| Quantitative Units | USD 1.5 billion to USD 5.5 billion, at a CAGR of 13.9% |

| Market Definition | Specialized hardware and software validating communication bridges between independent silicon dies. This infrastructure proves critical for identifying defects before final assembly, protecting high-value logic and substrate investments. |

| Segmentation | Test Stage, Solution Type, Interconnect Type, Package Architecture, End User, and Region |

| Regions Covered | North America, Europe, Asia Pacific, Latin America, Middle East and Africa |

| Countries Covered | Taiwan, South Korea, China, United States, Singapore, Japan, Germany |

| Key Companies Profiled | Advantest, Teradyne, FormFactor, Cohu, Chroma ATE, Synopsys, Siemens EDA |

| Forecast Period | 2026 to 2036 |

| Approach | Baseline sizing models capture deployed advanced packaging capacity matched to explicit chiplet adoption roadmaps. |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Chiplet Integration and Die-to-Die Interconnect Test Solutions Market Analysis by Segments

Test Stage:

- Wafer Test

- Package Test

- System Test

- Burn-In

Solution Type:

- ATE Platforms

- Probe Cards

- Interface Boards

- Inspection Tools

- DFT Software

Interconnect Type:

- UCIe

- Proprietary Links

- TSV Links

- Bridge Links

Package Architecture:

- 2.5D Packages

- 3D Stacks

- Fan-Out

- SiP Modules

End User:

- IDMs

- Foundries

- OSATs

- Fabless Firms

Region:

- North America

- United States

- Canada

- Europe

- Germany

- United Kingdom

- France

- Spain

- Italy

- BENELUX

- Rest of Europe

- Asia Pacific

- China

- Japan

- India

- South Korea

- Taiwan

- Singapore

- ASEAN

- ANZ

- Rest of Asia Pacific

- Latin America

- Brazil

- Mexico

- Rest of Latin America

- Middle East and Africa

- GCC Countries

- Türkiye

- South Africa

- North Africa

- Rest of Middle East and Africa

Bibliography

- Das Sharma, D., Pasdast, G., Tiagaraj, S., & Aygün, K. (2024, February). High-performance, power-efficient three-dimensional system-in-package designs with universal chiplet interconnect express. Nature Electronics, 7, 244-254.

- Onufryk, P., & Choudhary, S. (2025, January/February). UCIe: Standard for an open chiplet ecosystem. IEEE Micro, 45(1), 16–25.

- Muthrasanallur, S., & Zorian, Y. (2025, January/February). A test, debug, and silicon lifecycle management architecture for a UCIe-based open chiplet ecosystem. IEEE Micro, 45(1), 67-74.

- Keysight Technologies, Inc. (2025, January). Keysight expands chiplet interconnect standards support in Chiplet PHY Designer 2025.

- Cadence Design Systems, Inc. (2025, June). Cadence accelerates SoC, 3D-IC and chiplet design for AI data centers, automotive and connectivity in collaboration with Samsung Foundry.

This bibliography is provided for reader reference. The full FMI report contains the complete reference list with primary source documentation.

This Report Addresses

- Test engineering adaptation responding to ultra-fine contact pad shrink limits.

- Thermal footprint management constraints limiting massive concurrent probing.

- Substrate layout dependency dictating heavy 2.5D format deployment.

- Foundational protocol interoperability driven strictly by UCIe consortium mandates.

- Specialized inspection routing required catching hidden interposer micro-cracks.

- Concentrated platform control utilized effectively by Advantest and Teradyne.

- Regional assembly clustering fueling high-margin capabilities across Taiwan.

- Fabless architectural teams forcing customized design-for-test compliance tracking.

Frequently Asked Questions

how big is the chiplet test solutions market?

The valuation hits USD 1.5 billion in 2026, scaling rapidly to USD 5.5 billion by 2036. This sheer volume jump signals massive capital diversion away from legacy single-die testers directly into specialized heterogeneous validation cells.

What is the growth rate for this sector?

Growth maintains a 13.9% CAGR between 2026 and 2036. Sustained demand reflects pure yield economics; skipping specialized test steps guarantees catastrophic margin destruction downstream during final accelerator module assembly.

wafer test vs package test for chiplets: why does early screening dominate?

Wafer Test commands 34.0% share in 2026 because capturing interconnect defects before permanent bonding saves expensive surrounding logic components. Yield architects refuse assembling premium interposers using questionable bare die inputs.

What makes ATE Platforms the leading Solution Type?

ATE Platforms securely lead because validating high-density mixed-node configurations requires massive concurrent signal processing bandwidth. Test facilities demand these platforms to prevent massive data bottlenecks during complex verification sequences.

Why does UCIe capture the majority share in Interconnect Types?

UCIe holds 41.0% share driven by universal industry consortium backing. Fabless validation engineers leverage this specific standard protocol to instantly synthesize test patterns, completely eliminating tedious manual proprietary script generation.

how are chiplets tested across complex geographic supply chains?

Taiwan leads growth at 15.4% CAGR due to overwhelming concentration of foundry packaging ecosystems. Local procurement directors establish unassailable capability moats by securing priority equipment allocation directly adjacent to major substrate fabrication centers.

What distinguishes South Korea's growth profile?

South Korea advances at 14.9% CAGR, heavily skewed toward vertical memory stacking requirements. Test engineering managers locally deploy uniquely customized probe cards necessary for capturing subtle high-bandwidth memory interface variations.

Why are interface boards highly vulnerable to commoditization?

Tooling suppliers producing standard interface hardware face extreme pricing pressure once fab managers standardize physical footprints. Operations directors actively pit secondary suppliers against each other precisely to crush consumable tooling premiums.

what is UCIe compliance testing designed to prevent?

Compliance testing prevents mismatched communication protocols between mixed-origin dies. Test operations managers execute these standardized routines to guarantee that chiplets from different foundries can securely interface on the same substrate without deadlocking.

How do IDMs leverage their position?

IDMs capture 37.0% share by tightly coupling internal layout architects with final test floor supervisors. This extreme vertical integration allows rapid proprietary protocol iteration entirely impossible across fragmented outsourced assembly chains.

Why do 2.5D Packages command such high testing focus?

Holding 38.0% share, 2.5D layouts support massive artificial intelligence accelerator rollouts. Integration specialists deploy extreme high-speed instrumentation targeting subtle interposer cross-talk interference patterns destroying theoretical memory bandwidth limits.

What forces fabless firms into specific test strategies?

Fabless validation teams lacking internal factory access must guarantee protocol compliance strictly through simulation and external test houses. These teams prioritize design-for-test software suites precisely to prevent vendor lock-in at specific assembly facilities.

explain the chiplet test workflow from wafer to package and how it handles memory exhaustion?

Complex heterogeneous layouts quickly overwhelm legacy platform storage banks as wafers transition to final package testing. Facilities managers avoid splitting verification into multiple physical test passes by upgrading massive centralized vector memory subsystems inside premium ATE platforms.

Why is thermal density such a severe constraint?

High-power modules generate intense heat during full concurrent probing cycles. Socket designers battle continuously to balance precise electrical continuity against aggressive active liquid cooling requirements without distorting delicate substrate materials.

What defines the United States testing dynamic?

Scaling at 13.5% CAGR, United States engineering centers focus primarily on architectural compliance. High-performance compute designers demand sophisticated design-for-test tools exactly to dictate compliance metrics executed eventually by offshore factories.

How do automotive sensing modules impact European testing?

Germany grows at 10.9% CAGR focusing on precision mixed-signal integration. Qualification directors establish formidable barriers demanding absolute zero-defect traceability across specialized sensor-to-logic chiplet interconnects operating under extreme environmental stress.

Why do proprietary links still maintain hardware presence?

Certain extreme-performance accelerators require communication speeds bypassing even standard consortium protocols. Architectural leads deploy proprietary links temporarily to achieve immediate hardware superiority despite accepting brutal downstream testing ecosystem isolation.

What causes interposer signal integrity failures post-screening?

Identifying microscopic interposer substrate cracks during rapid factory signaling tests proves exceptionally difficult. Operations missing these specific degradation metrics ship technically defective modules that inevitably fail during intensive data center installations.

How does China approach testing capability?

China maintains 14.4% CAGR backed by state capital targeting packaging independence. Facilities managers secure broad screening capabilities, focusing heavily on volume throughput efficiency even while chasing cutting-edge sub-micron pitch nodes.

What is the commercial consequence of delaying platform upgrades?

Operations directors attempting advanced module screening using legacy equipment face immediate throughput collapse. Slow processing bandwidth creates massive factory bottlenecks exactly when major clients demand rapid premium accelerator delivery.

which companies lead chiplet test solutions in 2026 and how do they defend share?

Advantest and Teradyne lead by releasing specialized upgrade cards perfectly compatible with existing factory mainframes. Procurement directors overwhelmingly accept these evolutionary hardware paths to avoid the severe operational disruption of switching primary testing platform architectures.

What role does contactless probing play moving forward?

Test operations managers view radio frequency inductive coupling as the ultimate escape from mechanical contact limits. Eliminating physical touch-downs removes pad damage entirely, radically altering future consumable japan 3d TSV packages interface board lifecycle economics.

Table of Content

- Executive Summary

- Global Market Outlook

- Demand to side Trends

- Supply to side Trends

- Technology Roadmap Analysis

- Analysis and Recommendations

- Market Overview

- Market Coverage / Taxonomy

- Market Definition / Scope / Limitations

- Research Methodology

- Chapter Orientation

- Analytical Lens and Working Hypotheses

- Market Structure, Signals, and Trend Drivers

- Benchmarking and Cross-market Comparability

- Market Sizing, Forecasting, and Opportunity Mapping

- Research Design and Evidence Framework

- Desk Research Programme (Secondary Evidence)

- Company Annual and Sustainability Reports

- Peer-reviewed Journals and Academic Literature

- Corporate Websites, Product Literature, and Technical Notes

- Earnings Decks and Investor Briefings

- Statutory Filings and Regulatory Disclosures

- Technical White Papers and Standards Notes

- Trade Journals, Industry Magazines, and Analyst Briefs

- Conference Proceedings, Webinars, and Seminar Materials

- Government Statistics Portals and Public Data Releases

- Press Releases and Reputable Media Coverage

- Specialist Newsletters and Curated Briefings

- Sector Databases and Reference Repositories

- FMI Internal Proprietary Databases and Historical Market Datasets

- Subscription Datasets and Paid Sources

- Social Channels, Communities, and Digital Listening Inputs

- Additional Desk Sources

- Expert Input and Fieldwork (Primary Evidence)

- Primary Modes

- Qualitative Interviews and Expert Elicitation

- Quantitative Surveys and Structured Data Capture

- Blended Approach

- Why Primary Evidence is Used

- Field Techniques

- Interviews

- Surveys

- Focus Groups

- Observational and In-context Research

- Social and Community Interactions

- Stakeholder Universe Engaged

- C-suite Leaders

- Board Members

- Presidents and Vice Presidents

- R&D and Innovation Heads

- Technical Specialists

- Domain Subject-matter Experts

- Scientists

- Physicians and Other Healthcare Professionals

- Governance, Ethics, and Data Stewardship

- Research Ethics

- Data Integrity and Handling

- Primary Modes

- Tooling, Models, and Reference Databases

- Desk Research Programme (Secondary Evidence)

- Data Engineering and Model Build

- Data Acquisition and Ingestion

- Cleaning, Normalisation, and Verification

- Synthesis, Triangulation, and Analysis

- Quality Assurance and Audit Trail

- Market Background

- Market Dynamics

- Drivers

- Restraints

- Opportunity

- Trends

- Scenario Forecast

- Demand in Optimistic Scenario

- Demand in Likely Scenario

- Demand in Conservative Scenario

- Opportunity Map Analysis

- Product Life Cycle Analysis

- Supply Chain Analysis

- Investment Feasibility Matrix

- Value Chain Analysis

- PESTLE and Porter’s Analysis

- Regulatory Landscape

- Regional Parent Market Outlook

- Production and Consumption Statistics

- Import and Export Statistics

- Market Dynamics

- Global Market Analysis 2021 to 2025 and Forecast, 2026 to 2036

- Historical Market Size Value (USD Million) Analysis, 2021 to 2025

- Current and Future Market Size Value (USD Million) Projections, 2026 to 2036

- Y to o to Y Growth Trend Analysis

- Absolute $ Opportunity Analysis

- Global Market Pricing Analysis 2021 to 2025 and Forecast 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Test Stage

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Test Stage , 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Test Stage , 2026 to 2036

- Wafer Test

- Package Test

- System Test

- Burn-In

- Wafer Test

- Y to o to Y Growth Trend Analysis By Test Stage , 2021 to 2025

- Absolute $ Opportunity Analysis By Test Stage , 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Solution Type

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Solution Type, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Solution Type, 2026 to 2036

- ATE Platforms

- Probe Cards

- Interface Boards

- Inspection Tools

- DFT Software

- ATE Platforms

- Y to o to Y Growth Trend Analysis By Solution Type, 2021 to 2025

- Absolute $ Opportunity Analysis By Solution Type, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Region

- Introduction

- Historical Market Size Value (USD Million) Analysis By Region, 2021 to 2025

- Current Market Size Value (USD Million) Analysis and Forecast By Region, 2026 to 2036

- North America

- Latin America

- Western Europe

- Eastern Europe

- East Asia

- South Asia and Pacific

- Middle East & Africa

- Market Attractiveness Analysis By Region

- North America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- USA

- Canada

- Mexico

- By Test Stage

- By Solution Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Test Stage

- By Solution Type

- Key Takeaways

- Latin America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Brazil

- Chile

- Rest of Latin America

- By Test Stage

- By Solution Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Test Stage

- By Solution Type

- Key Takeaways

- Western Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Germany

- UK

- Italy

- Spain

- France

- Nordic

- BENELUX

- Rest of Western Europe

- By Test Stage

- By Solution Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Test Stage

- By Solution Type

- Key Takeaways

- Eastern Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Russia

- Poland

- Hungary

- Balkan & Baltic

- Rest of Eastern Europe

- By Test Stage

- By Solution Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Test Stage

- By Solution Type

- Key Takeaways

- East Asia Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- China

- Japan

- South Korea

- By Test Stage

- By Solution Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Test Stage

- By Solution Type

- Key Takeaways

- South Asia and Pacific Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- India

- ASEAN

- Australia & New Zealand

- Rest of South Asia and Pacific

- By Test Stage

- By Solution Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Test Stage

- By Solution Type

- Key Takeaways

- Middle East & Africa Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkiye

- South Africa

- Other African Union

- Rest of Middle East & Africa

- By Test Stage

- By Solution Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Test Stage

- By Solution Type

- Key Takeaways

- Key Countries Market Analysis

- USA

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Canada

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Mexico

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Brazil

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Chile

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Germany

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- UK

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Italy

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Spain

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- France

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- India

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- ASEAN

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Australia & New Zealand

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- China

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Japan

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- South Korea

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Russia

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Poland

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Hungary

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Kingdom of Saudi Arabia

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- Turkiye

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- South Africa

- Pricing Analysis

- Market Share Analysis, 2025

- By Test Stage

- By Solution Type

- USA

- Market Structure Analysis

- Competition Dashboard

- Competition Benchmarking

- Market Share Analysis of Top Players

- By Regional

- By Test Stage

- By Solution Type

- Competition Analysis

- Competition Deep Dive

- Advantest

- Overview

- Product Portfolio

- Profitability by Market Segments (Product/Age /Sales Channel/Region)

- Sales Footprint

- Strategy Overview

- Marketing Strategy

- Product Strategy

- Channel Strategy

- Teradyne

- FormFactor

- Cohu

- Chroma ATE

- Synopsys

- Siemens EDA

- Advantest

- Competition Deep Dive

- Assumptions & Acronyms Used

List of Tables

- Table 1: Global Market Value (USD Million) Forecast by Region, 2021 to 2036

- Table 2: Global Market Value (USD Million) Forecast by Test Stage , 2021 to 2036

- Table 3: Global Market Value (USD Million) Forecast by Solution Type, 2021 to 2036

- Table 4: North America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 5: North America Market Value (USD Million) Forecast by Test Stage , 2021 to 2036

- Table 6: North America Market Value (USD Million) Forecast by Solution Type, 2021 to 2036

- Table 7: Latin America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 8: Latin America Market Value (USD Million) Forecast by Test Stage , 2021 to 2036

- Table 9: Latin America Market Value (USD Million) Forecast by Solution Type, 2021 to 2036

- Table 10: Western Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 11: Western Europe Market Value (USD Million) Forecast by Test Stage , 2021 to 2036

- Table 12: Western Europe Market Value (USD Million) Forecast by Solution Type, 2021 to 2036

- Table 13: Eastern Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 14: Eastern Europe Market Value (USD Million) Forecast by Test Stage , 2021 to 2036

- Table 15: Eastern Europe Market Value (USD Million) Forecast by Solution Type, 2021 to 2036

- Table 16: East Asia Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 17: East Asia Market Value (USD Million) Forecast by Test Stage , 2021 to 2036

- Table 18: East Asia Market Value (USD Million) Forecast by Solution Type, 2021 to 2036

- Table 19: South Asia and Pacific Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 20: South Asia and Pacific Market Value (USD Million) Forecast by Test Stage , 2021 to 2036

- Table 21: South Asia and Pacific Market Value (USD Million) Forecast by Solution Type, 2021 to 2036

- Table 22: Middle East & Africa Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 23: Middle East & Africa Market Value (USD Million) Forecast by Test Stage , 2021 to 2036

- Table 24: Middle East & Africa Market Value (USD Million) Forecast by Solution Type, 2021 to 2036

List of Figures

- Figure 1: Global Market Pricing Analysis

- Figure 2: Global Market Value (USD Million) Forecast 2021-2036

- Figure 3: Global Market Value Share and BPS Analysis by Test Stage , 2026 and 2036

- Figure 4: Global Market Y-o-Y Growth Comparison by Test Stage , 2026-2036

- Figure 5: Global Market Attractiveness Analysis by Test Stage

- Figure 6: Global Market Value Share and BPS Analysis by Solution Type, 2026 and 2036

- Figure 7: Global Market Y-o-Y Growth Comparison by Solution Type, 2026-2036

- Figure 8: Global Market Attractiveness Analysis by Solution Type

- Figure 9: Global Market Value (USD Million) Share and BPS Analysis by Region, 2026 and 2036

- Figure 10: Global Market Y-o-Y Growth Comparison by Region, 2026-2036

- Figure 11: Global Market Attractiveness Analysis by Region

- Figure 12: North America Market Incremental Dollar Opportunity, 2026-2036

- Figure 13: Latin America Market Incremental Dollar Opportunity, 2026-2036

- Figure 14: Western Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 15: Eastern Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 16: East Asia Market Incremental Dollar Opportunity, 2026-2036

- Figure 17: South Asia and Pacific Market Incremental Dollar Opportunity, 2026-2036

- Figure 18: Middle East & Africa Market Incremental Dollar Opportunity, 2026-2036

- Figure 19: North America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 20: North America Market Value Share and BPS Analysis by Test Stage , 2026 and 2036

- Figure 21: North America Market Y-o-Y Growth Comparison by Test Stage , 2026-2036

- Figure 22: North America Market Attractiveness Analysis by Test Stage

- Figure 23: North America Market Value Share and BPS Analysis by Solution Type, 2026 and 2036

- Figure 24: North America Market Y-o-Y Growth Comparison by Solution Type, 2026-2036

- Figure 25: North America Market Attractiveness Analysis by Solution Type

- Figure 26: Latin America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 27: Latin America Market Value Share and BPS Analysis by Test Stage , 2026 and 2036

- Figure 28: Latin America Market Y-o-Y Growth Comparison by Test Stage , 2026-2036

- Figure 29: Latin America Market Attractiveness Analysis by Test Stage

- Figure 30: Latin America Market Value Share and BPS Analysis by Solution Type, 2026 and 2036

- Figure 31: Latin America Market Y-o-Y Growth Comparison by Solution Type, 2026-2036

- Figure 32: Latin America Market Attractiveness Analysis by Solution Type

- Figure 33: Western Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 34: Western Europe Market Value Share and BPS Analysis by Test Stage , 2026 and 2036

- Figure 35: Western Europe Market Y-o-Y Growth Comparison by Test Stage , 2026-2036

- Figure 36: Western Europe Market Attractiveness Analysis by Test Stage

- Figure 37: Western Europe Market Value Share and BPS Analysis by Solution Type, 2026 and 2036

- Figure 38: Western Europe Market Y-o-Y Growth Comparison by Solution Type, 2026-2036

- Figure 39: Western Europe Market Attractiveness Analysis by Solution Type

- Figure 40: Eastern Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 41: Eastern Europe Market Value Share and BPS Analysis by Test Stage , 2026 and 2036

- Figure 42: Eastern Europe Market Y-o-Y Growth Comparison by Test Stage , 2026-2036

- Figure 43: Eastern Europe Market Attractiveness Analysis by Test Stage

- Figure 44: Eastern Europe Market Value Share and BPS Analysis by Solution Type, 2026 and 2036

- Figure 45: Eastern Europe Market Y-o-Y Growth Comparison by Solution Type, 2026-2036

- Figure 46: Eastern Europe Market Attractiveness Analysis by Solution Type

- Figure 47: East Asia Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 48: East Asia Market Value Share and BPS Analysis by Test Stage , 2026 and 2036

- Figure 49: East Asia Market Y-o-Y Growth Comparison by Test Stage , 2026-2036

- Figure 50: East Asia Market Attractiveness Analysis by Test Stage

- Figure 51: East Asia Market Value Share and BPS Analysis by Solution Type, 2026 and 2036

- Figure 52: East Asia Market Y-o-Y Growth Comparison by Solution Type, 2026-2036

- Figure 53: East Asia Market Attractiveness Analysis by Solution Type

- Figure 54: South Asia and Pacific Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 55: South Asia and Pacific Market Value Share and BPS Analysis by Test Stage , 2026 and 2036

- Figure 56: South Asia and Pacific Market Y-o-Y Growth Comparison by Test Stage , 2026-2036

- Figure 57: South Asia and Pacific Market Attractiveness Analysis by Test Stage

- Figure 58: South Asia and Pacific Market Value Share and BPS Analysis by Solution Type, 2026 and 2036

- Figure 59: South Asia and Pacific Market Y-o-Y Growth Comparison by Solution Type, 2026-2036

- Figure 60: South Asia and Pacific Market Attractiveness Analysis by Solution Type

- Figure 61: Middle East & Africa Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 62: Middle East & Africa Market Value Share and BPS Analysis by Test Stage , 2026 and 2036

- Figure 63: Middle East & Africa Market Y-o-Y Growth Comparison by Test Stage , 2026-2036

- Figure 64: Middle East & Africa Market Attractiveness Analysis by Test Stage

- Figure 65: Middle East & Africa Market Value Share and BPS Analysis by Solution Type, 2026 and 2036

- Figure 66: Middle East & Africa Market Y-o-Y Growth Comparison by Solution Type, 2026-2036

- Figure 67: Middle East & Africa Market Attractiveness Analysis by Solution Type

- Figure 68: Global Market - Tier Structure Analysis

- Figure 69: Global Market - Company Share Analysis