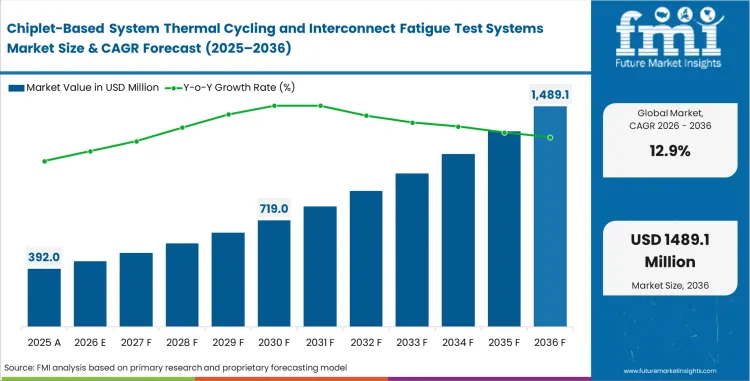

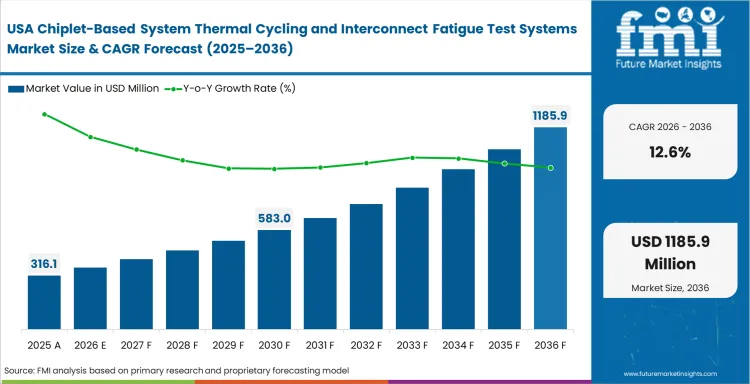

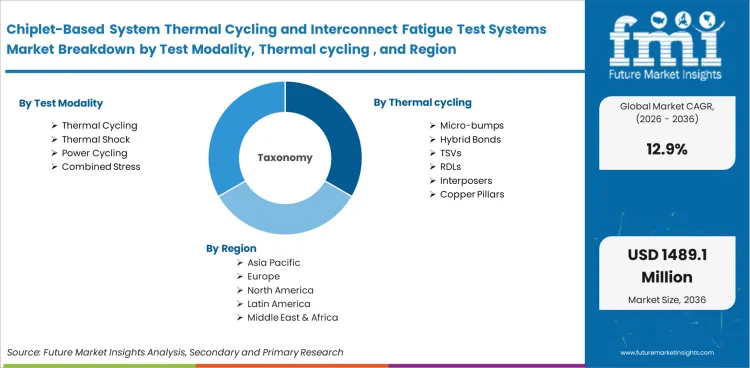

The chiplet-based system thermal cycling and interconnect fatigue test systems market surpassed a valuation of USD 348.0 million in 2025 and is estimated to reach USD 392.0 million in 2026. Industry valuation is projected to expand at a CAGR of 12.9% from 2026 to 2036, reaching nearly USD 1,313.0 million by 2036.

| Parameter | Details |

|---|---|

| Market value (2026) | USD 392.0 million |

| Forecast value (2036) | USD 1,313.0 million |

| CAGR (2026 to 2036) | 12.9% |

| Estimated market value (2025) | USD 348.0 million |

| Incremental opportunity | USD 921.0 million |

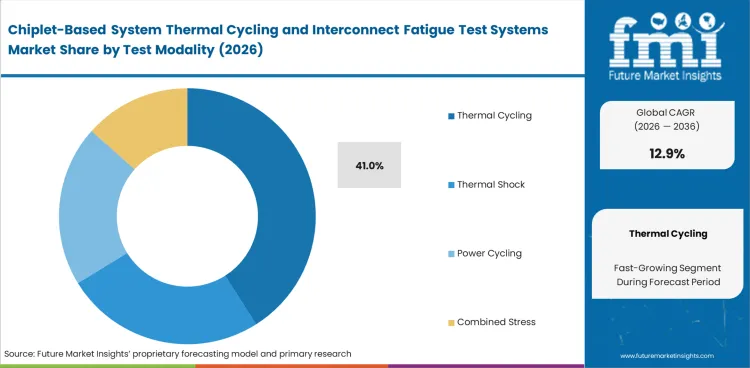

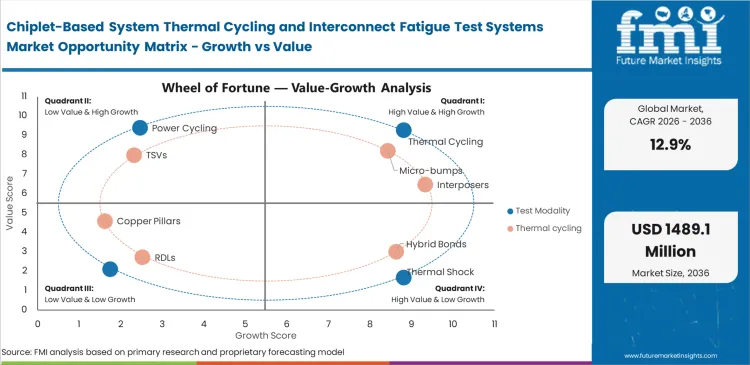

| Leading test modality | Thermal Cycling |

| Leading interconnect focus | Micro-bumps |

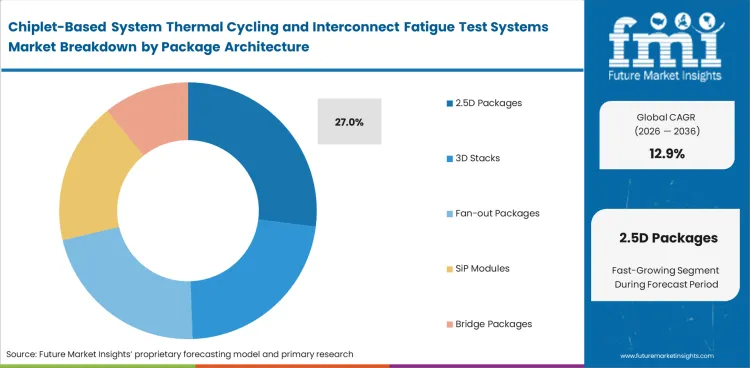

| Leading package architecture | 2.5D Packages |

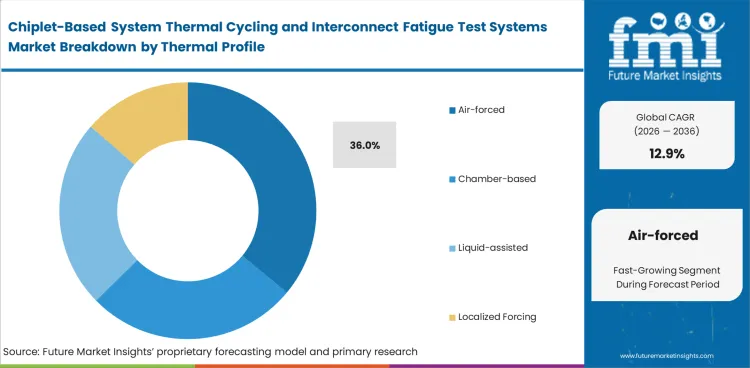

| Leading thermal profile | Air-forced |

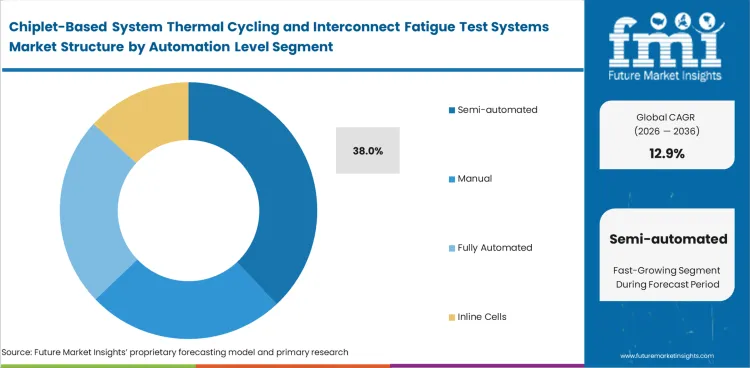

| Leading automation level | Semi-automated systems |

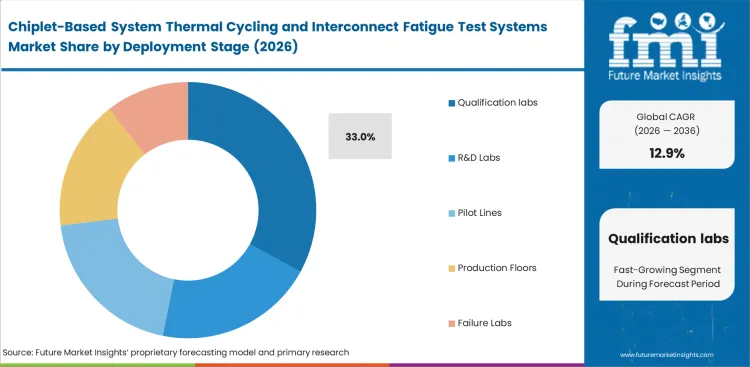

| Leading deployment stage | Qualification Labs |

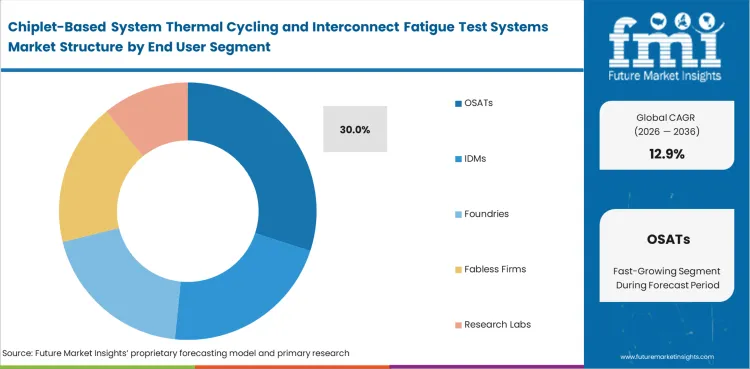

| Leading end user | OSATs |

| Leading measurement stack | Daisy-chain methods |

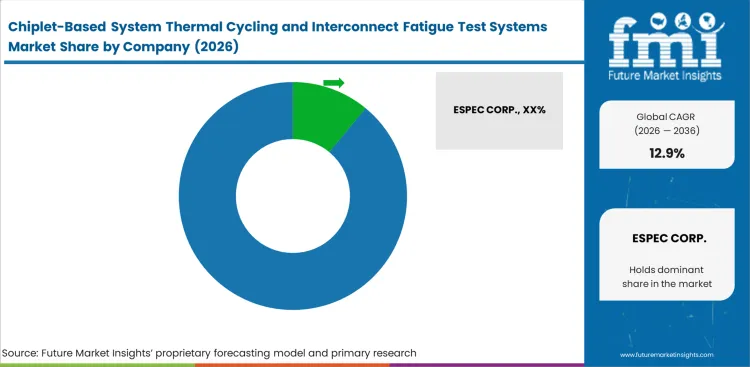

| Key supplier brands referenced in market landscape | ESPEC CORP., Advantest, MPI Corporation |

| Brands referenced in market landscape | ESPEC CORP., Advantest, MPI Corporation, Thermotron, inTEST Thermal Solutions, Cohu |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Purchase urgency rises when interconnect fatigue results become part of package signoff rather than a follow-up check after electrical drift appears. Semiconductor assembly and testing service providers, IDMs, and foundry-linked packaging groups move in that direction when customer release schedules start depending on faster fault isolation and tighter test consistency within semiconductor packaging operations. System demand strengthens once ownership is tied directly to release timing and qualification accountability.

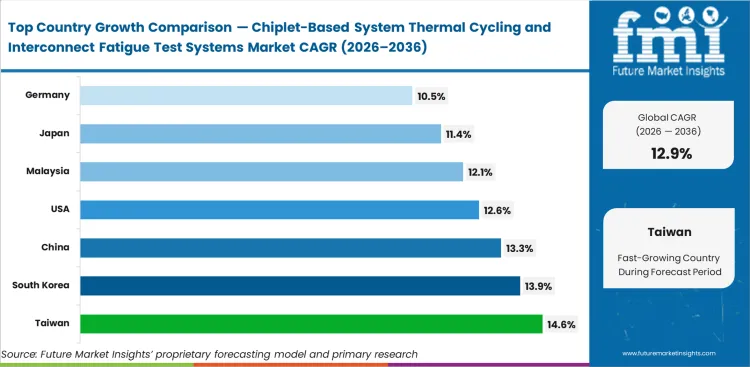

Taiwan is projected to record a 14.6% CAGR through 2036, supported by its deep concentration of chiplet development, backend engineering activity, and tight linkage between package design and qualification execution. South Korea is likely to expand at 13.9%, reflecting strong package complexity and heavy reliability demands tied to advanced memory and logic integration. China is expected to register 13.3% as domestic packaging capability continues to widen and more qualification work is retained closer to local development cycles. The United States is anticipated to post 12.6%, backed by high-value chiplet programs and strong demand for cleaner interconnect validation across complex package architectures. Malaysia is set to grow at 12.1%, helped by its role in outsourced backend operations and rising qualification depth across export-oriented packaging lines. Japan is projected to advance at 11.4%, where reliability discipline remains strong, but adoption tends to move through more selective program ramps. Germany is likely to expand at 10.5%, with growth still tied to narrower high-specification use cases and a more measured pace of backend qualification investment.

For chiplet-based systems, thermal cycling is no longer a back-end validation step; it is increasingly shaping architecture choices much earlier in development. That matters because chiplets bring together dies, bridges, substrates, underfills, and interconnect structures with different thermal expansion behaviors, which raises the probability of fatigue, delamination, and time-dependent failure at package level. UCIe’s published direction on expanded reliability mechanisms and health monitoring reinforces that the industry is treating interconnect robustness as a system issue, not a narrow PHY issue.

Thermal cycling is expected to account for 41.0% share in 2026. Package reliability work in chiplet systems still leans first toward repeated thermal stress rather than broader one-time screening routines because interconnect weakness usually develops gradually across expansion and contraction cycles. Buyers rely on this modality when they need to understand how micro-bumps, hybrid-bond joints, and substrate connections behave over time under controlled conditions. Thermal shock and power cycling still matter, but they are used more selectively when a narrower failure pattern needs to be isolated. Thermal cycling stays ahead because it fits qualification workflows better than other test methods used in package reliability work. Engineering teams also prefer the repeatability of this setup when comparing package revisions or customer-specific builds. Early fatigue signs become easier to interpret when the stress path remains disciplined across long runs. Commercial value stays strongest where the method helps labs turn interconnect behavior into approval-grade reliability evidence rather than isolated failure snapshots.

Interconnect testing in chiplet systems begins where mechanical weakness is most likely to be built under repeated thermal exposure. Micro-bumps stay at the center of that effort because they support many die-to-die and package-level connections where pitch is tight, and tolerance for continuity loss is low. Engineering teams return to this interconnect type repeatedly, since small shifts in joint behavior can affect signal integrity, usable package life, and eventual customer acceptance. Market estimates suggest micro-bumps will represent 29.0% share in 2026. Hybrid bonds, TSVs, RDLs, interposers, and copper pillars also remain relevant, but their testing priority depends more directly on the package route being qualified. Micro-bumps keep the lead because they remain one of the clearest fatigue-sensitive points in current chiplet designs. That is also why adjacent demand is rising around chiplet integration and die-to-die interconnect test solutions where joint-level behavior matters early.

Package architecture shapes how thermal stress travels through a chiplet assembly and where reliability teams place their first attention. Buyers working on AI, HPC, and memory-linked designs often prefer 2.5D routes when they need dense integration without taking on the full process burden of more vertically stacked structures. Their lead comes from a practical balance between performance ambition and packaging manageability. In 2026, 2.5D packages are projected to contribute 27.0% of total market share because they are widely used in designs that depend on interposers and high-density die integration. Three-dimensional stacks, fan-out packages, SiP modules, and bridge-based designs all create testing demand as well, but 2.5D remains tied more broadly to current qualification programs. Its commercial base is therefore wider than that of narrower architecture choices. That position also keeps testing demand closely linked with the broader advanced packaging space, where adoption of width strongly influences reliability spending.

Thermal forcing choice depends on how buyers balance control, facility burden, maintenance effort, and day-to-day usability in the lab. Many programs prefer air-based systems for routine qualification work because they are easier to deploy, easier to maintain, and easier to adapt across changing package studies. Chamber-based setups, liquid-assisted methods, and localized forcing approaches still serve specific needs, especially when tighter profile control or faster response matters more than operating simplicity. Even so, broader use remains with air-forced systems because they cover a wide range of qualification conditions without pushing complexity too far. That practical fit keeps them ahead in a market where routine usability still matters as much as performance precision. Air-forced systems are likely to secure 36.0% share in 2026. Their lead also overlaps clearly with the broader automated test equipment environment, where deployment ease can outweigh more specialized thermal extremes.

Test automation in this market is shaped less by full production logic and more by the need to balance flexibility with consistency across changing package designs. Full manual setups slow work too much once chiplet programs expand, while fully automated cells are not always justified where sample volumes remain limited or thermal conditions keep changing. Semi-automated systems are set to make up 38.0% of the market in 2026. These tools fit the middle ground because they reduce handling variation, improve logging discipline, and still leave room for engineering adjustment during qualification work. That balance becomes especially important when package structures vary from one program to another and the work remains design-specific rather than fully standardized. Similar mixed deployment logic can be seen in system level test platforms, where rigid automation does not always match early-stage validation reality. Buyers usually prefer this level when full automation cannot yet be justified by sample volume or program maturity.

Deployment stage reveals how this market still behaves commercially because much of the demand remains tied to proving package reliability before broader volume use begins. Chiplet programs bring enough design variation that approval work stays concentrated inside controlled validation settings rather than moving quickly into routine production-floor operation. R&D labs help with early learning, pilot lines bridge the move toward scaling, and failure labs step in when root-cause work becomes necessary. Qualification labs still lead because they sit at the point where engineering intent meets customer acceptance. Buyers continue to spend here first since weak package reliability at this stage can delay entire programs, which also explains the wider relevance of semiconductor inspection systems. Qualification labs are expected to account for 33.0% share in 2026. Spending concentration at this stage reflects the fact that approval pressure arrives before standardization does.

Backend assembly and validation activity makes OSATs one of the most visible demand centers in this market. Their role places them close to package assembly, customer qualification, and failure screening across a wide mix of chiplet programs. That exposure matters because OSATs face reliability demands from several customers rather than from one internal product line, which keeps equipment use cases active across more programs. IDMs and foundries remain important users, especially where advanced package work stays in-house, while fabless firms and research labs shape demand through design and qualification activity. OSATs lead demand because they carry much of the package qualification burden across multiple customer programs. That commercial position also links naturally with the broader semiconductor assembly and testing services value chain. OSATs are anticipated to represent 30.0% share in 2026. Value in this segment comes from supporting users embedded in repeated customer‑facing reliability reviews, where a shared platform can shape multiple package qualifications and release decisions in parallel.

Measurement-stack choice determines how quickly fatigue behavior can be noticed and how clearly failure progression can be interpreted during repeated stress work. Many users begin with daisy-chain methods because the first question in qualification is often whether interconnect continuity is degrading at all before deeper diagnosis is layered in. Kelvin sensing, resistance logging, warpage tracking, and event monitoring all deepen the analysis, but they usually add complexity beyond what standard approval routines require in the first pass. Daisy-chain methods remain popular because they are easier to deploy, easier to compare across runs, and easier to explain in routine package review settings. Their commercial lead therefore reflects usability as much as technical relevance. Buyers often start here before moving into more detailed monitoring layers, especially where workflows connect with wider semiconductor-packaging qualification practices. Daisy-chain methods are forecast to account for 32.0% share in 2026. Commercial value is highest when the measurement stack identifies continuity drift early while keeping the output practical enough for routine reliability decisions across multiple chiplet programs.

Package release requirements are making thermal cycling and interconnect fatigue tools more central to chiplet qualification. Reliability groups are being asked to show earlier proof that package joints and die-to-die paths can survive repeated thermal stress before wider customer acceptance begins. That shift matters because late failure discovery now carries a higher cost once advanced packaging work becomes more complex and more tightly scheduled. Demand also benefits from adjacent stress validation habits already visible in Burn-In and System-Level Test (SLT) platforms for AI accelerators, where heat, package density, and system conditions are increasingly judged together. Buyers who move earlier usually gain cleaner debug loops and faster handoff into qualification review.

Internal approval still slows this market more than broad interest does. Many labs already own environmental chambers, so a dedicated chiplet fatigue system must prove that it improves repeatability, data clarity, and release timing rather than simply adding another piece of hardware. That hesitation exists because ownership often sits across package reliability, lab operations, and capital budgeting groups. Some suppliers offer modular setups or smaller entry systems, but these options do not always reduce integration effort, training needs, or software mismatch. Spending can stall when buyers see the need clearly but cannot agree on where the tool belongs in the release process.

Opportunities in the Chiplet-Based System Thermal Cycling and Interconnect Fatigue Test Systems Market

Based on the regional analysis, the chiplet-based system thermal cycling and interconnect fatigue test systems market is segmented into Asia Pacific, North America, and Europe across 40 plus countries.

.webp)

| Country | CAGR (2026 to 2036) |

|---|---|

| Taiwan | 14.6% |

| South Korea | 13.9% |

| China | 13.3% |

| United States | 12.6% |

| Malaysia | 12.1% |

| Japan | 11.4% |

| Germany | 10.5% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Package qualification work in Asia Pacific sits closest to active backend lines, so buying decisions tend to move when package programs move rather than when broad lab budgets reopen. Taiwan, South Korea, China, Malaysia, and Japan all bring different strengths, yet they share the same pressure: interconnect failures must be found early enough to protect expensive package turns. Demand in this region also rises because advanced packaging, memory integration, and substrate work are clustered across a small number of production corridors linked to AI-enabled semiconductor defect classification and review systems and related package verification needs. General chambers can still support early study, but dedicated fatigue tools become easier to defend once release timing tightens.

FMI's report also reviews Singapore, India, and other Asia Pacific markets where advanced packaging capability is developing at different speeds. Wider regional demand does not move in one line. Countries with strong backend concentration adopt sooner, while countries with early-stage packaging plans first build test knowledge through shared labs and pilot programs.

In North America, demand is shaped more by design ownership and qualification planning than by backend manufacturing scale. Package architects and validation groups often define stress requirements before assembly scale is fixed, which changes how systems are evaluated. Equipment selection leans heavily on data quality, software fit, and the ability to align with wider demand for automated test equipment in USA decisions rather than on chamber hardware alone. Package groups also spend more time deciding whether dedicated chiplet fatigue tools should sit in central reliability labs or near pilot packaging lines. That internal placement question can slow orders, yet it also makes requirements sharper once budgets are approved. Buying mistakes here show up as longer release cycles rather than simple lab inconvenience.

FMI's report also covers Canada and Mexico, where electronics manufacturing and test activity create narrower but still relevant demand pockets. Regional growth remains tied to design concentration in the United States, while nearby markets benefit when validation work or assembly support spreads across the broader semiconductor base.

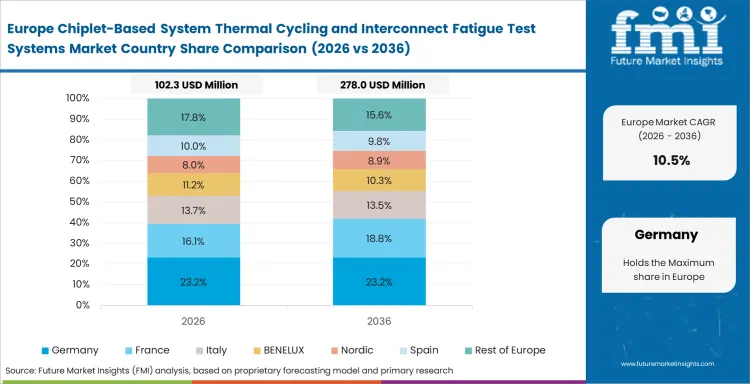

Europe approaches this market with a stronger reliability and application-fit lens than a pure volume lens. Buying decisions often sit closer to automotive, industrial, and specialized semiconductor requirements, which means system choice is judged by stability and service support before it is judged by raw throughput. That pattern keeps the regional opportunity relevant even without the same backend scale seen in Asia Pacific. Interest also overlaps with advanced node wafer defect inspection systems and other precision test tools because package verification is rarely purchased in isolation. Slow approval can limit near-term installs, yet qualified demand stays durable when devices serve long-life applications.

FMI's report further reviews France, the United Kingdom, the Netherlands, Italy, and other Europe segment where demand builds around automotive electronics, power devices, and specialist packaging programs. Regional expansion is shaped less by broad packaging scale and more by how strongly each country links advanced semiconductor work to local end-use industries.

Service depth continues to play a defining role in vendor selection, often outweighing headline chamber specifications. Buyers place sustained emphasis on stable thermal performance, dependable control behavior, and maintenance support that does not slow active qualification programs. Suppliers that perform well in localized stress work tend to remain in shortlists because they help limit variability during fatigue testing and reduce diagnosis time after long stress runs. Weaknesses in software export or service response can quickly negate hardware strengths once package schedules begin to tighten.

Evaluation criteria also extend beyond the tool to how well a system fits into existing test environments and purchasing logic. Vendors with broad semiconductor test exposure, such as Advantest, are often reviewed through the lens of advanced packaging share analysis and established backend relationships. At the same time, buyers favor solutions that can be positioned alongside semiconductor defect inspection equipment without adding workflow friction. Across both approaches, training effort, system upkeep, and ease of integration remain central to final approval decisions.

Looking forward, the vendor landscape is not expected to converge around a single dominant group, as chiplet fatigue testing continues to sit between environmental stress, reliability engineering, and semiconductor test operations. Buyer tolerance for loosely connected systems is likely to narrow as package complexity increases. Vendors such as Cohu and inTEST Thermal Solutions stay relevant by addressing complementary aspects of the requirement, from chamber‑level performance to alignment with wider test workflows. Competitive differentiation will depend on local service availability, usable software, and the ability to adapt the system to daily package qualification work.

| Metric | Value |

|---|---|

| Quantitative Units | USD 392.0 million to USD 1,313.0 million, at a CAGR of 12.90% |

| Market Definition | Thermal cycling and interconnect fatigue systems used to qualify chiplet packages, expose package-level failure paths, and support release-stage reliability decisions for multi-die assemblies. |

| Test Modality Segmentation | Thermal Cycling, Thermal Shock, Power Cycling, Combined Stress |

| Interconnect Focus Segmentation | Micro-bumps, Hybrid Bonds, TSVs, RDLs, Interposers, Copper Pillars |

| Package Architecture Segmentation | 2.5D Packages, 3D Stacks, Fan-out Packages, SiP Modules, Bridge Packages |

| End User Segmentation | OSATs, IDMs, Foundries, Fabless Firms, Research Labs |

| Regions Covered | Asia Pacific, North America, Europe |

| Countries Covered | Taiwan, South Korea, China, United States, Malaysia, Japan, Germany, and 40 plus countries |

| Key Companies Profiled | ESPEC CORP., Advantest, MPI Corporation, Thermotron, inTEST Thermal Solutions, Cohu |

| Forecast Period | 2026 to 2036 |

| Approach | FMI combines supplier mapping, package qualification workflow analysis, technical review of chiplet interconnect stress needs, and primary interviews across reliability, packaging, and backend validation roles. Market sizing follows the portion of advanced packaging and semiconductor test spend that is directed toward dedicated thermal cycling and interconnect fatigue use cases. |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

This bibliography is provided for reader reference. The full FMI report contains the complete reference list with primary source documentation.

What is the current value of the chiplet thermal cycling and interconnect fatigue test systems industry?

FMI estimates the industry at USD 348.0 million in 2025 and expects it to reach USD 392.0 million in 2026.

How fast is the industry expected to grow through 2036?

FMI projects demand to expand at a CAGR of 12.9% from 2026 to 2036.

What valuation is expected by the end of the forecast period?

Industry value is forecast to reach USD 1,313.0 million by 2036.

Why are thermal cycling systems leading this space?

Thermal cycling remains the most widely used approach because repeated temperature exposure gives a clearer view of interconnect fatigue in chiplet packages.

Which interconnect type generates the highest testing focus?

Micro-bumps lead the interconnect focus segment since they are among the first connection points where thermal stress can affect long-term package reliability.

Which package architecture is creating the most demand for these systems?

2.5D packages are expected to stay ahead because they are widely used in advanced multi-die integration and need close qualification work at the package level.

Who are the main end users of these test systems?

OSATs, IDMs, foundries, fabless firms, and research labs are the main user groups, with OSATs holding the strongest position in current demand.

Which end user segment is expected to lead in 2026?

OSATs are projected to remain the leading end user group as backend assembly and customer qualification work continue to concentrate there.

Which countries are likely to see the fastest expansion?

Taiwan, South Korea, and China are expected to post the strongest growth, supported by advanced packaging activity and rising chiplet validation needs.

What is driving adoption of chiplet interconnect fatigue test systems?

Adoption is rising because package complexity is increasing and buyers need more dependable ways to check how die-to-die connections behave under repeated thermal stress.

What does this report include within its scope?

The report covers thermal cycling and related fatigue test systems used for chiplet package validation across test modality, interconnect focus, package architecture, thermal profile, automation level, deployment stage, end user, and measurement stack.

Which companies are discussed in the competitive landscape?

Key companies covered in the report include ESPEC CORP., Advantest, MPI Corporation, Thermotron, inTEST Thermal Solutions, and Cohu.

Full Research Suite comprises of:

Market outlook & trends analysis

Interviews & case studies

Strategic recommendations

Vendor profiles & capabilities analysis

5-year forecasts

8 regions and 60+ country-level data splits

Market segment data splits

12 months of continuous data updates

DELIVERED AS:

PDF EXCEL ONLINE

Thank you!

You will receive an email from our Business Development Manager. Please be sure to check your SPAM/JUNK folder too.