High-Aspect-Ratio 3D NAND Metrology Equipment Market

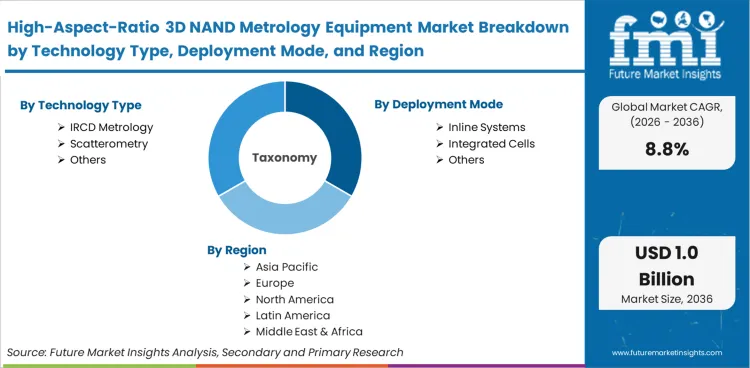

High-aspect-ratio 3D NAND metrology equipment market is segmented by Technology type (IRCD metrology, Scatterometry, CD-SEM, X-ray metrology, Hybrid metrology), Deployment mode (Inline systems, Integrated cells, Offline labs, Hybrid workflows), Measurement focus (Channel holes, W-recess, Staircase profiles, Overlay control, Film thickness), End user (Memory IDMs, Tool labs, Foundries, Research institutes), Process stage (Etch control, Deposition control, CMP control, Module integration, Failure analysis), Fab generation (128–176 layers, 200–300 layers, 300+ layers), and Region. Forecast for 2026 to 2036.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Size, Market Forecast and Outlook By FMI

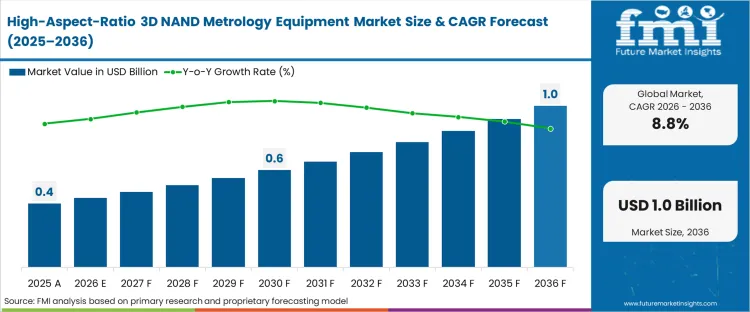

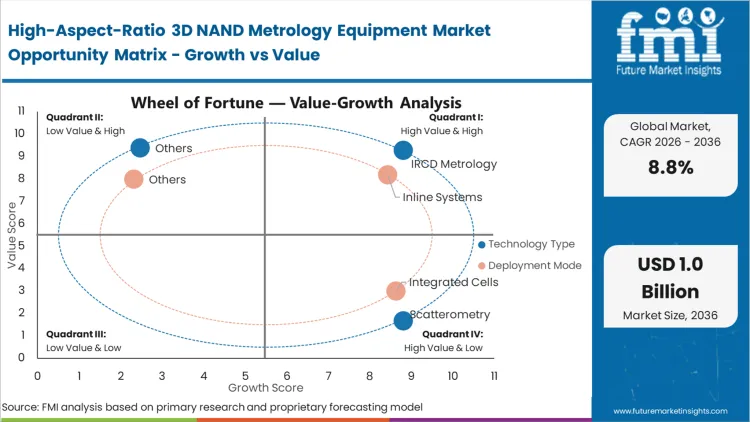

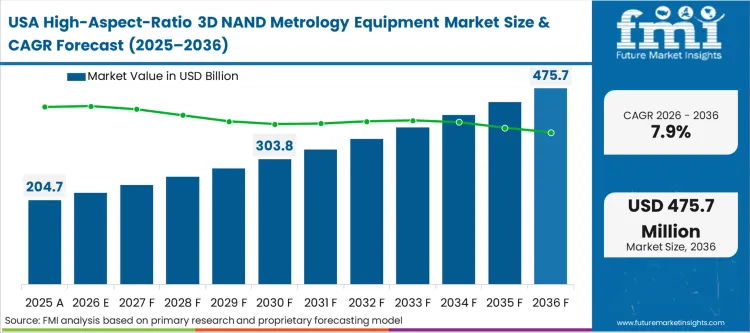

The high-aspect-ratio 3D NAND metrology equipment market was valued at USD 0.40 billion in 2025. Revenue within the broader semiconductor metrology market is set to surpass USD 0.43 billion in 2026 at a CAGR of 8.80% during 2026 to 2036. Continued investment propels the overall 3D NAND metrology market size to USD 1.00 billion through 2036 as fab nodes cross 200-layer thresholds demanding non-destructive metrology for deep NAND features.

Procurement directors at major memory IDMs face an immediate yield crisis when evaluating the 3D NAND technology roadmap beyond 128 layers. Blindly etching micron-deep channels creates bowing and tilting defects in 3D NAND that destroy device functionality before wafer testing even begins. Delaying capital equipment upgrades forces semiconductor metrology and inspection teams to rely on destructive cross-sectioning, consuming days of critical cycle time per lot. Fab operators now prioritize inline 3D NAND metrology platform vendors over raw etch speed to prevent scrap events, shifting focus toward specialized high aspect ratio metrology for 3D NAND.

Summary of High-Aspect-Ratio 3D NAND Metrology Equipment Market

- High-Aspect-Ratio 3D NAND Metrology Equipment Market Definition

- This sector encompasses measurement platforms capable of characterizing deep trench geometries, channel hole profiles, and hidden layer alignments in vertical memory architectures. Systems utilize penetrating wavelengths to capture subsurface data without destroying processed wafers.

- Demand Drivers in the Market

- Profile bowing defects compel yield engineers to implement inline interferometry during high-aspect-ratio etch steps.

- Stringent overlay tolerances force fab directors to procure penetrating X-ray metrology for opaque staircase structures.

- Escalating wafer scrap costs push capital equipment buyers to replace destructive testing with optical scatterometry solutions.

- Key Segments Analyzed in the FMI Report

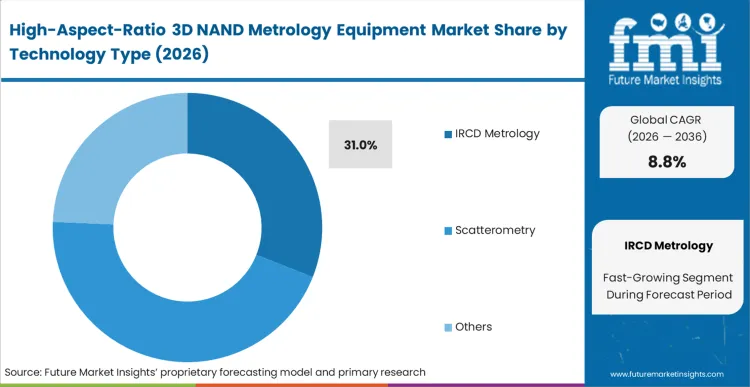

- IRCD metrology is poised to hold 31.0% share in 2026, as infrared wavelengths penetrate thick dielectric stacks without electron charging artifacts.

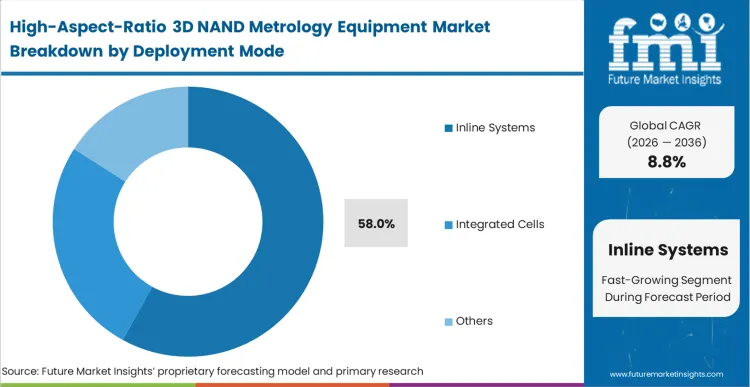

- Inline systems is expected to record 58.0% share in 2026, driven by yield managers demanding lot-to-lot feedback.

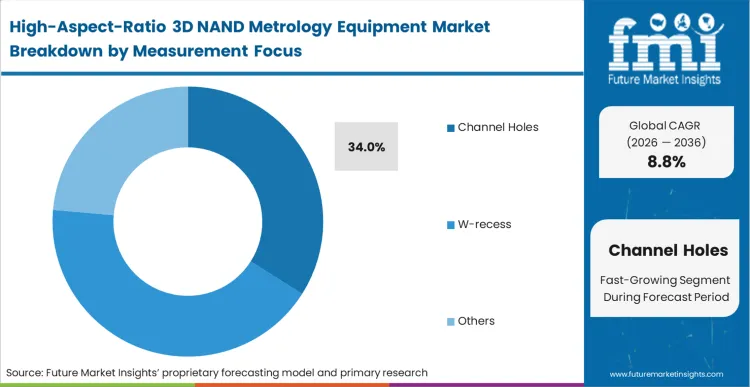

- Channel holes is estimated to capture 34.0% share in 2026, representing incredibly deep structures requiring advanced profile characterization.

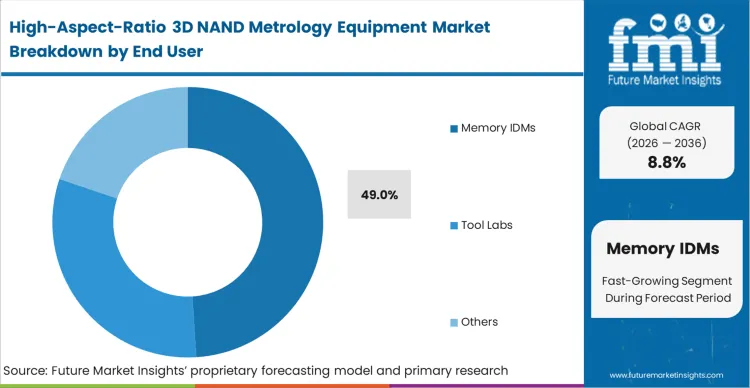

- Memory IDMs is anticipated to grab 49.0% share in 2026, operating massive gigafabs dedicated entirely to vertical storage arrays.

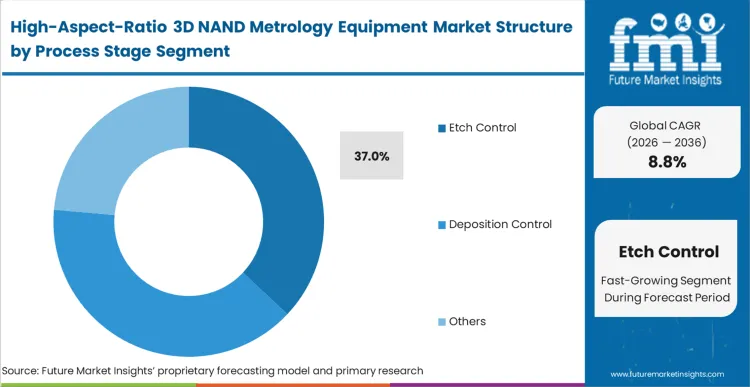

- Etch control is projected to garner 37.0% share in 2026, preventing critical dimension variations during deep plasma etching.

- 200-300 layers is set to account for 41.0% share in 2026, forming today's absolute bleeding-edge battleground for high-volume manufacturing scaling.

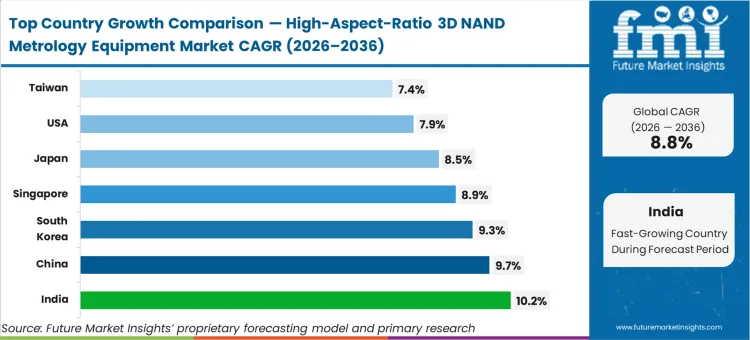

- India: 10.2% compound growth, propelled by aggressive federal capital expenditure subsidies for greenfield semiconductor facilities.

- Analyst Opinion at FMI

- Sudip saha, Principal Analyst, Technology, at FMI, observes that, "Generalist models assume higher layer counts linearly drive metrology tool purchases. Metrology directors running 200-layer fabs know that tool speed degrades exponentially as aspect ratios increase. Measuring a 300-layer channel hole requires significantly longer signal acquisition times than a 128-layer equivalent, cratering total wafer throughput. Fab managers must procure drastically more measurement units per thousand wafer starts just to maintain existing sampling rates. This throughput collapse dictates equipment demand far more than raw fab expansion plans."

- Strategic Implications / Executive Takeaways

- Equipment suppliers must integrate machine learning algorithms to reduce signal acquisition times for yield managers.

- Memory fab operators face escalating capital intensity per wafer start requiring renegotiated tool pricing models.

- Tool developers avoiding infrared or X-ray modalities risk complete exclusion from next-generation 300-layer factory floors.

Key Takeaways

| Metric | Details |

|---|---|

| Industry Size (2026) | USD 0.43 Billion |

| Industry Value (2036) | USD 1.00 Billion |

| CAGR (2026-2036) | 8.80% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Once memory architects trigger 300 layer 3D NAND process control requirements, optical overlay tools hit fundamental physics limitations. Opaque tier stacks require penetrating infrared or X-ray semiconductor defect inspection equipment capability to accurately capture 3D NAND deep hole profile measurement. Transitioning from generic scatterometry to advanced interferometric measurement allows continuous volume manufacturing without relying on delayed offline sampling.

India leads at 10.2% on aggressive greenfield semiconductor subsidies, presenting a massive India semiconductor metrology opportunity, while China tracks at 9.7% as domestic IDMs accelerate indigenous 3d nand flash memory scaling despite export controls. South Korea expands at 9.3% through persistent leading-edge tool deployments by local incumbents. Singapore grows at 8.9% due to concentrated capacity expansions by foreign-headquartered memory makers. Japan advances at 8.5% driven by continuous Kioxia capital investments. The United States progresses at 7.9%, focusing on localised pilot lines, whereas Taiwan records 7.4% owing to foundry dominance over pure memory output. Geographic divergence in the 3D NAND inspection and metrology market stems strictly from national-level semiconductor self-sufficiency mandates overriding standard commercial cycle timing.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Definition

High-Aspect-Ratio 3D NAND Metrology Equipment Market comprises specialized measurement systems engineered explicitly to characterize critical dimensions, profiles, and overlay structures in vertical memory stacks exceeding 20:1 depth-to-width ratios. Equipment architectures utilize infrared, X-ray, or advanced electron beams to penetrate thick multi-layer dielectric films non-destructively, supporting dedicated memory fab metrology tools. Measurement platforms integrate tightly with dry etch and deposition chambers to provide near-real-time feedback for memory device fabrication.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Inclusions

Scope incorporates optical scatterometry platforms, critical dimension scanning electron microscopes, infrared interferometry tools, and X-ray systems deployed within memory fabrication facilities. Optical wafer inspection system components sold explicitly for vertical profile characterization fall within bounds. Standalone algorithms bundled with high-aspect-ratio measurement hardware remain in scope, defining the core of the advanced memory inspection equipment category.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Exclusions

Bare semiconductor wafers and chemical mechanical planarization equipment are excluded because they represent substrates and processing steps rather than measurement technologies. General-purpose defect review microscopes utilized for front-end logic fabrication fall outside bounds due to insufficient electron landing energies required for deep trench penetration. Backend packaging inspection tools are omitted entirely since high-aspect-ratio challenges remain strictly confined to front-end cell array formation.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Research Methodology

- Primary Research: Fab directors, yield engineering managers, and capital equipment procurement officers evaluating 3D NAND metrology equipment manufacturers

- Desk Research: Capital expenditure filings from pure-play memory manufacturers, SEMI equipment billings reports, and advanced node technical papers

- Market-Sizing and Forecasting: Fab equipment run-rates and node transition roadmaps at 200+ layer architectures establish baseline tool demand

- Data Validation and Update Cycle: Semiconductor equipment manufacturer earnings transcripts and quarterly bookings data cross-verify final volume projections

Segmental Analysis

High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis by Technology Type

Conventional optical scatterometry fails entirely to penetrate opaque memory stacks exceeding 100 layers. FMI's analysis indicates IRCD metrology holds 31.0% share in 2026 as yield engineers recognise infrared wavelengths bypass electron charging issues inherent to scanning electron microscopes. Fab directors adopting semiconductor manufacturing equipment utilizing IRCD for 3D NAND avoid destructive wafer cross-sectioning entirely. What equipment share data obscures is that IRCD tools suffer from severe spot-size limitations, forcing metrologists to sacrifice spatial resolution for depth penetration. Fabs lacking advanced infrared platforms suffer massive unyielding silicon when etch profiles bow invisibly deep within channel holes.

- Wavelength penetration: Infrared light transmits through thick amorphous carbon hardmasks allowing bottom critical dimension measurement. Yield engineers avoid blind wafer processing.

- Charging immunity: Non-conductive dielectric stacks accumulate heavy surface charge under electron beam inspection causing severe image distortion. Metrology managers bypass charging artifacts entirely utilizing optical IRCD systems.

- Spot-size trade-off: Diffraction limits inherent to longer infrared wavelengths restrict measurement of tightly pitched memory cells. Optical physicists must integrate advanced algorithms to extract meaningful data from blurred spectral signatures.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis by Deployment Mode

Wafer transport logistics dictate metrology placement when cycle times stretch beyond three months for advanced memory chips. Inline systems command 58.0% share in 2026 based on FMI's assessment, enabling lot-to-lot etch recipe correction without breaking factory automation flow. Manufacturing executives eliminate queue time delays associated with routing wafers to offline metrology software laboratories. Procuring standalone systems rather than integrated chamber metrology actually provides superior vibration isolation, a detail equipment buyers rarely highlight externally. Relying strictly on offline analysis causes fab managers to process hundreds of defective wafers before detecting dangerous process drift.

- Transport automation: Overhead hoists deliver carriers directly to inline metrology bays eliminating manual wafer transfer. Fab managers maintain continuous factory flow.

- Vibration isolation: High-resolution optical interferometers require massive granite bases separated from heavy vacuum pumps. Facilities engineers achieve nanometer-scale stability impossible within active etch chambers.

- Queue time elimination: Rapid inline measurements feed predictive control systems instantly. Process control directors prevent multi-lot scrap events caused by drifting plasma parameters.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis by Measurement Focus

Tension between etch rate and profile verticality defines memory cell yield. Based on FMI's projection, Channel holes retain 34.0% share in 2026, representing complex structures etched through oxide-nitride pairs within the 3D NAND channel hole metrology market. Dry etch modules blast plasma downward, requiring process engineers to monitor critical dimensions at top, middle, and bottom locations. Generalist observers assume measuring word-line recesses requires identical capability, but channel holes uniquely suffer from twisting defects invisible to standard semiconductor inspection system platforms. Failing to measure bottom CD accurately results in open circuits across entire gigabyte arrays.

- Profile twisting: High-aspect-ratio plasma etching inevitably induces microscopic lateral twisting as ions travel downward. Process engineers must characterize this twisting to calibrate etch module magnetic fields.

- Bottom dimensioning: Extracting accurate hole diameters at aspect ratios exceeding 50:1 pushes spectral interferometry limits. Yield managers face total die failure if bottom CDs shrink beyond specification.

- Hardmask consumption: Measuring remaining carbon hardmask thickness during channel etch prevents catastrophic collapse. Integration engineers require precise thickness data to optimize mask deposition steps.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis by End user

Massive capital requirements restrict advanced memory production to heavily consolidated corporate entities. Memory IDMs hold 49.0% share in 2026; operating semiconductor capital equipment fleets measured in tens of billions of dollars. Procurement directors at these firms dictate roadmap requirements directly to metrology tool vendors. FMI analysts note that captive tool evaluation labs run by these IDMs generate more fundamental measurement physics research than commercial vendors themselves. Tool manufacturers ignoring IDM beta-site feedback find their platforms permanently disqualified from high-volume factory floors.

- Volume leverage: Gigafab operators purchase metrology tools in bulk units simultaneously. Procurement directors secure heavily discounted pricing structures impossible for smaller foundries.

- Beta-site validation: Memory giants dedicate entire pilot lines explicitly for testing unreleased metrology hardware. R&D directors shape equipment specifications years before commercial launch.

- Ecosystem lock-in: Once IDMs qualify specific inspection platforms for a node, transitioning requires breaking established statistical process control models. Factory managers treat vendor substitution as an unacceptable yield risk.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis by Process Stage

Plasma physics instability demands constant parameter monitoring during deep material removal. FMI observes Etch control captures 37.0% share in 2026 as chamber components degrade daily, drifting baseline etch rates. Etch module owners require continuous feedback loops from advanced process control software to adjust RF bias power. While deposition steps appear equally critical, etching defines actual device geometry whereas deposition merely fills it. Module engineers operating without rapid metrology feedback spend millions processing dummy wafers just to qualify chamber stability.

- Chamber drift: Polymer buildup inside plasma chambers alters internal gas flow dynamics over time. Etch engineers utilize metrology data to trigger necessary chamber cleaning cycles.

- Profile tuning: Adjusting RF pulsing frequencies alters side-wall passivation during deep trench etching. Process integration specialists require precise profile measurements to dial in optimal pulse parameters.

- Dummy wafer reduction: Reliable inline measurement allows continuous production without pausing for offline verification. Fab directors maximize expensive tool utilization rates by eliminating qualification lots.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis by Fab generation

Transitioning beyond double-deck architectures requires completely reinventing overlay alignment methodologies. The 200-300 layers segment is set to claim 41.0% share in 2026, forming today's battleground for high-volume memory scaling. Integration directors face unprecedented challenges aligning upper-tier stacks flawlessly onto lower tiers. FMI's estimates indicate wafer manufacturing equipment capability peaks here before requiring exotic cryogenic etching. Factories stuck on 128-layer technologies suffer brutal margin compression as leading-edge competitors slash per-bit manufacturing costs.

- Tier alignment: Stacking two independent modules requires perfect overlay accuracy to connect vertical channels. Integration directors rely on penetrating X-ray metrology to view buried alignment marks.

- Stress management: Hundreds of alternating film layers induce severe mechanical bowing across 300mm silicon substrates. Wafer geometry metrology alerts engineers before excessive warpage shatters wafers during subsequent processing.

- Cryogenic transition: Pushing past 300 layers forces fabs to adopt ultra-low temperature etch chemistry. Procurement officers must re-qualify entirely new metrology platforms compatible with cryogenic defect signatures.

High-Aspect-Ratio 3D NAND Metrology Equipment Market Drivers, Restraints, and Opportunities

Yield crashes resulting from invisible subsurface defects force metrology engineering directors to abandon legacy scatterometry immediately. Delaying upgrades to advanced infrared or X-ray platforms guarantees catastrophic wafer scrap once vertical memory stacks exceed 200 layers. Optical wavelengths physically cannot penetrate opaque hardmasks and thick multi-tier dielectric films, rendering traditional wafer processing equipment measurement useless. Fab managers facing multi-million dollar lot losses demand tools capable of characterizing deep channel hole bowing and bottom critical dimensions without destructive cross-sectioning. Urgency strips away typical multi-year qualification cycles, accelerating immediate capital deployments.

Throughput collapse prevents fab directors from achieving target wafer output despite massive capital investments. As aspect ratios increase exponentially, metrology systems require significantly longer signal integration times to capture weak photons bouncing from trench bottoms. Tool vendors patch this physics constraint with stronger light sources, yet fundamental signal-to-noise ratios remain stubbornly low. Fab operators utilizing high purity process systems must purchase three times as many measurement units to maintain historic sampling rates. Capital intensity slows broader factory expansion as available budgets evaporate into metrology bays.

Opportunities in the High-Aspect-Ratio 3D NAND Metrology Equipment Market

- Cryogenic etch compatibility: Metrology vendors developing optical models specifically tuned for ultra-cold fluorocarbon polymer residues win immediate qualification from leading memory IDMs.

- X-ray source miniaturization: Engineering compact X-ray tubes capable of fitting onto standard semiconductor memory inline platforms breaks offline laboratory bottlenecks entirely.

- Machine learning noise reduction: Software teams deploying neural networks to extract clean profiles from heavily blurred optical signals allow fabs to increase tool throughput without hardware upgrades.

Regional Analysis

The regional analysis divides the High-Aspect-Ratio 3D NAND Metrology Equipment Market into North America, Latin America, Western and Eastern Europe, East Asia, South Asia & Pacific, and the Middle East & Africa, covering more than 40 countries.

.webp)

| Country | CAGR (2026 to 2036) |

|---|---|

| India | 10.2% |

| China | 9.7% |

| South Korea | 9.3% |

| Singapore | 8.9% |

| Japan | 8.5% |

| United States | 7.9% |

| Taiwan | 7.4% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

South Asia and Pacific High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis

Greenfield factory initiatives rewrite baseline capital expenditure patterns across emerging semiconductor hubs. FMI's analysis reveals massive federal incentive structures override traditional memory cycle economics, forcing rapid procurement of advanced inspection tools for newly constructed pilot lines. Procurement officers evaluate leading-edge metrology platforms to establish baseline yield data before committing to high-volume manufacturing toolsets. Regional dependence on semiconductor packaging shifts backward into front-end fabrication capabilities.

- India: Aggressive federal capital expenditure subsidies compel multinational consortia to establish greenfield semiconductor facilities. Metrology engineering directors face severe skills shortages, forcing them to purchase highly automated tools requiring minimal local calibration. With the Indian high-aspect-ratio 3D NAND metrology equipment demand expanding at 10.2%, tool vendors securing these early anchor contracts lock in decades of future volume expansion.

- Singapore: Key players unusually concentrated local footprint dictates regional metrology demand within the broader Singapore NAND metrology equipment segment. Fab managers execute aggressive 200+ layer node transitions requiring massive upgrades to existing optical scatterometry fleets. Demand grows at 8.9% as existing gigafabs swap legacy inspection bays for advanced infrared platforms. Localized supply chains insulate these facilities from broader geopolitical equipment restrictions.

East Asia High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis

Leading-edge memory manufacturing remains fundamentally anchored across three dominant coastal geographies. Yield engineering directors sitting in massive gigafabs dictate global equipment roadmaps by demanding continuous throughput improvements for extreme aspect ratio geometries. According to FMI's estimates, these facilities process massive volumes of 300mm silicon worldwide, consuming metrology tools in bulk orders. Capital depreciation schedules force fab operators to maximize utilization rates across newly installed inspection fleets.

- China: Domestic IDMs accelerate indigenous memory scaling despite sweeping export controls blocking specific ultra-violet wafer cleaning equipment platforms. Engineering directors pivot toward unrestrained metrology categories to maximize yield on existing patterning tools, fueling the China 3D NAND metrology equipment industry. Revenue scales at 9.7% as national self-sufficiency mandates guarantee unlimited capital funding for critical measurement hardware. Indigenous tool vendors capture massive share behind this geopolitical firewall.

- South Korea: Persistent leading-edge tool deployments by local incumbents define capital cycles. Metrology managers coordinate directly with national equipment champions to beta-test next-generation X-ray interferometry systems. Advancing at 9.3%, the South Korea 3D NAND metrology industry reflects massive 300-layer wafer starts required to maintain global memory dominance. Smaller foundries simply cannot match this concentrated capital intensity.

- Japan: Continuous Kioxia capital investments sustain robust metrology procurement cycles. Integration directors prioritize highly reliable CD-SEM platforms optimized for their specific BiCS memory architectures. Generating 8.5% compound growth, localized equipment vendors maintain tightly integrated development partnerships with domestic memory giants to secure Japan NAND metrology equipment demand. Breaking these entrenched vendor relationships requires breakthrough physics rather than localisedal cost savings.

- Taiwan: Foundry dominance over pure memory output caps dedicated NAND metrology upside. Fab operators optimize capital spending toward logic-focused inspection rather than deep trench infrared systems. Growing at 7.4%, the Taiwan process control equipment segment demand relies on smaller specialty memory manufacturers rather than massive IDM gigafabs. Yield strategies here favor generic defect review over hyper-specialized high-aspect-ratio measurement.

North America High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis

Federal supply chain resilience legislation drives localized pilot line construction isolated from Asian manufacturing hubs. FMI observes R&D directors operating these facilities focus explicitly on next-generation 300+ layer architectures rather than matching legacy volume production. Equipment buyers evaluate exotic X-ray and acoustic metrology concepts long before commercial viability. This innovation-first approach heavily favors domestic equipment suppliers holding strong intellectual property portfolios.

- United States: Localized pilot lines absorb initial waves of federal funding. R&D directors specify maximum-capability inspection tools regardless of throughput limitations to characterize experimental cryogenic etch profiles. Expanding at 7.9%, the US high-aspect-ratio 3D NAND metrology equipment segment skews heavily toward low-volume, high-precision laboratory tools rather than inline factory automation. This creates a lucrative niche for highly specialized spectral interferometry developers.

FMI's report includes extensive analysis covering Latin America, Western Europe, and Eastern Europe markets. Equipment developers targeting these regions focus on specialized consumable parts distribution rather than installing massive gigafab tool fleets.

Competitive Aligners for Market Players

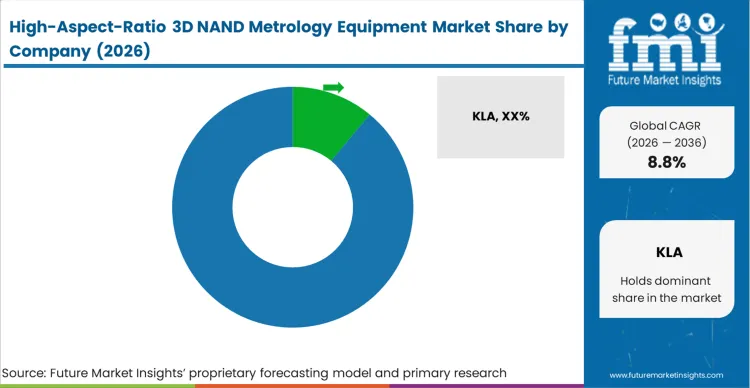

Vendor qualification cycles create nearly impenetrable barriers for emerging metrology developers. KLA and Onto Innovation maintain deep engineering partnerships with memory IDMs, embedding their proprietary algorithms directly into factory yield management systems. Metrology engineering directors rarely risk replacing an installed optical platform because new thin wafer processing and dicing equipment tools require entirely different statistical baseline data. Incumbents extract massive recurring revenue by selling software license upgrades rather than shipping fresh iron, defining the competitive strategies of 3D NAND metrology key players.

Tool matching capability dictates which suppliers win bulk gigafab orders. Applied Materials and Hitachi High-Tech demonstrate superior fleet-level precision, ensuring twenty different inline CD-SEMs output identical measurement values across active factory floors. Fab operators reject vendors lacking this fleet-matching capability, regardless of individual tool resolution. Equipment buyers demand integrated semiconductor bonding equipment calibration routines that eliminate manual engineer intervention during daily operations.

Memory IDMs actively fund secondary equipment suppliers to prevent absolute monopoly pricing power. Procurement officers deliberately purchase Nova systems to maintain negotiating leverage against larger incumbents, ensuring competitive pricing on maintenance contracts. Strategic multi-sourcing ensures continuous physics innovation while punishing suppliers attempting to lock in extortionate service margins. Inspecting ic packaging materials requires vastly different wavelengths, meaning 3D NAND metrology equipment suppliers survive exclusively by proving their optical models reduce actual wafer scrap faster than competing mathematical approaches.

Key Players in High-Aspect-Ratio 3D NAND Metrology Equipment Market

- KLA

- Onto Innovation

- Nova

- Hitachi High-Tech

- Applied Materials

- Lasertec

- Camtek

Scope of the Report

| Metric | Value |

|---|---|

| Quantitative Units | USD 0.40 Billion to USD 1.00 Billion, at a CAGR of 8.80% |

| Market Definition | Specialized measurement systems engineered explicitly to characterize critical dimensions and profiles in vertical memory stacks exceeding 20:1 depth-to-width ratios. Utilizing penetrating wavelengths, these platforms capture subsurface data without destroying processed wafers. |

| Segmentation | Technology type, Deployment mode, Measurement focus, End user, Process stage, Fab generation, and Region |

| Regions Covered | North America, Latin America, Western Europe, Eastern Europe, East Asia, South Asia and Pacific, Middle East and Africa |

| Countries Covered | United States, China, Japan, South Korea, Taiwan, India, Singapore |

| Key Companies Profiled | KLA, Onto Innovation, Nova, Hitachi High-Tech, Applied Materials, Lasertec, Camtek |

| Forecast Period | 2026 to 2036 |

| Approach | Fab equipment run-rates and node transition roadmaps at 200+ layer architectures establish baseline tool demand |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

High-Aspect-Ratio 3D NAND Metrology Equipment Market Analysis by Segments

Technology type:

- IRCD metrology

- Scatterometry

- CD-SEM

- X-ray metrology

- Hybrid metrology

Deployment mode:

- Inline systems

- Integrated cells

- Offline labs

- Hybrid workflows

Measurement focus:

- Channel holes

- W-recess

- Staircase profiles

- Overlay control

- Film thickness

End user:

- Memory IDMs

- Tool labs

- Foundries

- Research institutes

Process stage:

- Etch control

- Deposition control

- CMP control

- Module integration

- Failure analysis

Fab generation:

- 128-176 layers

- 200-300 layers

- 300+ layers

Region:

- North America

- United States

- Canada

- Europe

- Germany

- United Kingdom

- France

- Italy

- Spain

- Asia Pacific

- China

- Japan

- South Korea

- Taiwan

- Singapore

- Latin America

- Brazil

- Mexico

- Argentina

- Middle East & Africa

- GCC Countries

- South Africa

Bibliography

- Jang, J., et al. (2024, April). CDSAXS study of 3D NAND channel hole etch pattern edge effects and etched hole pattern variance. Proceedings of SPIE.

- Association for Computing Machinery. (2025, June). NAND Flash Memory Scaling and Process Technology Modeling in the AI Era. ACM Digital Library.

- SEMI. (2025, July). SEMI Reports Global Total Semiconductor Equipment Sales Forecast to Reach $125.5 Billion in 2025. SEMI Press Release.

- Onto Innovation Inc. (2025). Annual report 2024. Onto Innovation Investor Relations.

- Nova Ltd. (2024, April). Unique Spectral Interferometry solutions for complex High AspectRatio 3D NAND structures. Nova Publications.

- Kioxia Holdings Corporation. (2024, September). Kioxia Established a Loan Facility for Capital Investment. Kioxia News.

- Micron Technology. (2026, January). Micron Breaks Ground on Advanced Wafer Fabrication Facility in Singapore. Micron Investor News.

- Hitachi High-Tech Corporation. (2024, November). Hitachi High-Tech Launches DCR Etch System 9060 Series, Supporting Isotropic Etching of Advanced 3D Devices at the Atomic Level. Hitachi News.

This bibliography is provided for reader reference. The full FMI report contains the complete reference list with primary source documentation.

Frequently Asked Questions

Explain the high-aspect-ratio 3D NAND metrology equipment market?

This sector comprises measurement platforms capable of characterizing deep trench geometries, channel hole profiles, and hidden layer alignments in vertical memory architectures. Systems utilize penetrating wavelengths to capture subsurface data without destroying processed wafers.

Why does 3D NAND need infrared metrology over legacy optical systems?

Infrared wavelengths physically penetrate thick amorphous carbon hardmasks and opaque dielectric stacks. Legacy optical scatterometry fails entirely to transmit through 200-layer stacks, leaving yield engineers completely blind to bottom critical dimensions during deep trench etching.

How are channel hole defects measured in 3D NAND?

Channel holes require etching highly complex cylinders at aspect ratios exceeding 50:1. Microscopic lateral twisting occurs continuously as ions travel downward, causing open circuits if metrologists fail to characterize bottom dimensions accurately using specialized interferometry.

What tools are used for 3D NAND metrology most frequently?

Fab operators refuse to break automated wafer transport flow. Routing wafers to offline laboratories consumes days of cycle time, forcing process engineers to rely heavily on best inline metrology for channel hole profile control directly attached to etch modules.

What drives growth in the 3D NAND metrology market?

Plasma chamber components degrade continuously, drifting baseline material removal rates. Etch engineers require constant, real-time metrology feedback to tune RF pulsing frequencies and prevent severe profile variations across 300mm silicon substrates, fueling continuous equipment upgrades.

Who are the leading 3D NAND metrology equipment suppliers?

Memory IDMs embed proprietary vendor algorithms directly into their statistical process control software. Industry stalwarts like KLA, Onto Innovation, and Nova dominate because transitioning to new optical platforms requires completely regenerating historical baseline data.

Where is demand strongest for 3D NAND metrology equipment?

Massive federal capital expenditure subsidies create greenfield semiconductor ecosystems from scratch in Asia. Procurement officers lacking legacy tool fleets purchase highly automated, leading-edge metrology platforms immediately to establish baseline yield data for pilot lines.

Summarize 3D NAND metrology equipment trends through 2036?

As aspect ratios climb, signal acquisition times increase exponentially. Fab directors must purchase significantly more measurement units simply to maintain historic wafer sampling rates, absorbing budget previously allocated for raw production expansion, driving sustained 3D NAND metrology market forecast 2036 valuations.

Which metrology technologies are best for deep 3D NAND holes?

Pushing past 300 layers requires ultra-low temperature fluorocarbon chemistry. Procurement officers must re-qualify entirely new metrology platforms capable of detecting unique cold-polymer residues invisible to current generation optical inspection tools.

Compare IRCD vs CD-SEM for 3D NAND metrology?

While CD-SEM provides exceptional surface resolution, it physically cannot penetrate deep dielectric structures and suffers from electron charging artifacts. IRCD bypasses these limitations by transmitting infrared light through the stack, allowing true bottom-dimension measurement.

Which regions will buy more 3D NAND metrology tools?

National self-sufficiency mandates guarantee unlimited capital funding for critical measurement hardware in China and Korea. Engineering directors pivot heavily toward unrestrained metrology categories to maximize yield on existing patterning tools behind established geopolitical firewalls.

Give me 3D NAND metrology market size and key players?

Valued at USD 0.40 billion in 2025, the market is projected to reach USD 1.00 billion by 2036. Dominant forces include KLA, Onto Innovation, Nova, and Hitachi High-Tech, maintaining deeply entrenched relationships with global memory IDMs.

How to choose a 3D NAND metrology platform for gigafab deployment?

Fab operators demand identical measurement values across twenty different inline CD-SEMs. Equipment buyers reject vendors lacking fleet-matching precision, regardless of individual tool resolution or baseline hardware costs.

What are the main challenges in measuring high-aspect-ratio NAND holes?

Diffraction limits inherent to longer infrared wavelengths restrict spatial resolution. Optical physicists must integrate advanced algorithms to extract meaningful data, leaving labs exposed to interpretation errors when modeling tightly pitched memory cells.

What is the total cost of ownership 3D NAND metrology tools impact?

Software teams deploying neural networks extract clean profiles from heavily blurred optical signals. Yield managers successfully increase tool throughput and reduce capital intensity without requiring fundamental hardware physics upgrades.

What commercial opportunity opens for new equipment developers?

Metrology vendors engineering compact, inline X-ray tubes bypass optical physics limitations entirely. Developers solving this offline laboratory bottleneck win immediate qualification and massive bulk orders from leading memory IDMs.

Why is non-destructive metrology for deep NAND features critical?

Integration engineers require precise remaining thickness data to optimize mask deposition steps. Measuring carbon hardmask thickness during channel etch prevents catastrophic collapse across entire gigabyte arrays.

How does multi-deck 3D NAND metrology differ from logic inspection?

Stacking two independent 128-layer modules forces integration directors to align buried marks perfectly. Penetrating X-ray capability becomes mandatory here to connect vertical channels, rendering previous generation alignment methods obsolete.

Table of Content

- Executive Summary

- Global Market Outlook

- Demand to side Trends

- Supply to side Trends

- Technology Roadmap Analysis

- Analysis and Recommendations

- Market Overview

- Market Coverage / Taxonomy

- Market Definition / Scope / Limitations

- Research Methodology

- Chapter Orientation

- Analytical Lens and Working Hypotheses

- Market Structure, Signals, and Trend Drivers

- Benchmarking and Cross-market Comparability

- Market Sizing, Forecasting, and Opportunity Mapping

- Research Design and Evidence Framework

- Desk Research Programme (Secondary Evidence)

- Company Annual and Sustainability Reports

- Peer-reviewed Journals and Academic Literature

- Corporate Websites, Product Literature, and Technical Notes

- Earnings Decks and Investor Briefings

- Statutory Filings and Regulatory Disclosures

- Technical White Papers and Standards Notes

- Trade Journals, Industry Magazines, and Analyst Briefs

- Conference Proceedings, Webinars, and Seminar Materials

- Government Statistics Portals and Public Data Releases

- Press Releases and Reputable Media Coverage

- Specialist Newsletters and Curated Briefings

- Sector Databases and Reference Repositories

- FMI Internal Proprietary Databases and Historical Market Datasets

- Subscription Datasets and Paid Sources

- Social Channels, Communities, and Digital Listening Inputs

- Additional Desk Sources

- Expert Input and Fieldwork (Primary Evidence)

- Primary Modes

- Qualitative Interviews and Expert Elicitation

- Quantitative Surveys and Structured Data Capture

- Blended Approach

- Why Primary Evidence is Used

- Field Techniques

- Interviews

- Surveys

- Focus Groups

- Observational and In-context Research

- Social and Community Interactions

- Stakeholder Universe Engaged

- C-suite Leaders

- Board Members

- Presidents and Vice Presidents

- R&D and Innovation Heads

- Technical Specialists

- Domain Subject-matter Experts

- Scientists

- Physicians and Other Healthcare Professionals

- Governance, Ethics, and Data Stewardship

- Research Ethics

- Data Integrity and Handling

- Primary Modes

- Tooling, Models, and Reference Databases

- Desk Research Programme (Secondary Evidence)

- Data Engineering and Model Build

- Data Acquisition and Ingestion

- Cleaning, Normalisation, and Verification

- Synthesis, Triangulation, and Analysis

- Quality Assurance and Audit Trail

- Market Background

- Market Dynamics

- Drivers

- Restraints

- Opportunity

- Trends

- Scenario Forecast

- Demand in Optimistic Scenario

- Demand in Likely Scenario

- Demand in Conservative Scenario

- Opportunity Map Analysis

- Product Life Cycle Analysis

- Supply Chain Analysis

- Investment Feasibility Matrix

- Value Chain Analysis

- PESTLE and Porter’s Analysis

- Regulatory Landscape

- Regional Parent Market Outlook

- Production and Consumption Statistics

- Import and Export Statistics

- Market Dynamics

- Global Market Analysis 2021 to 2025 and Forecast, 2026 to 2036

- Historical Market Size Value (USD Million) Analysis, 2021 to 2025

- Current and Future Market Size Value (USD Million) Projections, 2026 to 2036

- Y to o to Y Growth Trend Analysis

- Absolute $ Opportunity Analysis

- Global Market Pricing Analysis 2021 to 2025 and Forecast 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Technology Type

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Technology Type , 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Technology Type , 2026 to 2036

- IRCD Metrology

- Scatterometry

- Others

- IRCD Metrology

- Y to o to Y Growth Trend Analysis By Technology Type , 2021 to 2025

- Absolute $ Opportunity Analysis By Technology Type , 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Deployment Mode

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Deployment Mode, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Deployment Mode, 2026 to 2036

- Inline Systems

- Integrated Cells

- Others

- Inline Systems

- Y to o to Y Growth Trend Analysis By Deployment Mode, 2021 to 2025

- Absolute $ Opportunity Analysis By Deployment Mode, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Measurement Focus

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Measurement Focus, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Measurement Focus, 2026 to 2036

- Channel Holes

- W-recess

- Others

- Channel Holes

- Y to o to Y Growth Trend Analysis By Measurement Focus, 2021 to 2025

- Absolute $ Opportunity Analysis By Measurement Focus, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By End User

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By End User, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By End User, 2026 to 2036

- Memory IDMs

- Tool Labs

- Others

- Memory IDMs

- Y to o to Y Growth Trend Analysis By End User, 2021 to 2025

- Absolute $ Opportunity Analysis By End User, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Process Stage

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Process Stage, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Process Stage, 2026 to 2036

- Etch Control

- Deposition Control

- Others

- Etch Control

- Y to o to Y Growth Trend Analysis By Process Stage, 2021 to 2025

- Absolute $ Opportunity Analysis By Process Stage, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Fab Generation

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Fab Generation, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Fab Generation, 2026 to 2036

- 200-300 layers

- 128-176 layers

- 300+ layers

- 200-300 layers

- Y to o to Y Growth Trend Analysis By Fab Generation, 2021 to 2025

- Absolute $ Opportunity Analysis By Fab Generation, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Region

- Introduction

- Historical Market Size Value (USD Million) Analysis By Region, 2021 to 2025

- Current Market Size Value (USD Million) Analysis and Forecast By Region, 2026 to 2036

- North America

- Latin America

- Western Europe

- Eastern Europe

- East Asia

- South Asia and Pacific

- Middle East & Africa

- Market Attractiveness Analysis By Region

- North America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- USA

- Canada

- Mexico

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Key Takeaways

- Latin America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Brazil

- Chile

- Rest of Latin America

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Key Takeaways

- Western Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Germany

- UK

- Italy

- Spain

- France

- Nordic

- BENELUX

- Rest of Western Europe

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Key Takeaways

- Eastern Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Russia

- Poland

- Hungary

- Balkan & Baltic

- Rest of Eastern Europe

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Key Takeaways

- East Asia Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- China

- Japan

- South Korea

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Key Takeaways

- South Asia and Pacific Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- India

- ASEAN

- Australia & New Zealand

- Rest of South Asia and Pacific

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Key Takeaways

- Middle East & Africa Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkiye

- South Africa

- Other African Union

- Rest of Middle East & Africa

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Key Takeaways

- Key Countries Market Analysis

- USA

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Canada

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Mexico

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Brazil

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Chile

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Germany

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- UK

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Italy

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Spain

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- France

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- India

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- ASEAN

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Australia & New Zealand

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- China

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Japan

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- South Korea

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Russia

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Poland

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Hungary

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Kingdom of Saudi Arabia

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Turkiye

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- South Africa

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- USA

- Market Structure Analysis

- Competition Dashboard

- Competition Benchmarking

- Market Share Analysis of Top Players

- By Regional

- By Technology Type

- By Deployment Mode

- By Measurement Focus

- By End User

- By Process Stage

- By Fab Generation

- Competition Analysis

- Competition Deep Dive

- KLA

- Overview

- Product Portfolio

- Profitability by Market Segments (Product/Age /Sales Channel/Region)

- Sales Footprint

- Strategy Overview

- Marketing Strategy

- Product Strategy

- Channel Strategy

- Onto Innovation

- Nova

- Hitachi High-Tech

- Applied Materials

- Lasertec

- KLA

- Competition Deep Dive

- Assumptions & Acronyms Used

List of Tables

- Table 1: Global Market Value (USD Million) Forecast by Region, 2021 to 2036

- Table 2: Global Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 3: Global Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 4: Global Market Value (USD Million) Forecast by Measurement Focus, 2021 to 2036

- Table 5: Global Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 6: Global Market Value (USD Million) Forecast by Process Stage, 2021 to 2036

- Table 7: Global Market Value (USD Million) Forecast by Fab Generation, 2021 to 2036

- Table 8: North America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 9: North America Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 10: North America Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 11: North America Market Value (USD Million) Forecast by Measurement Focus, 2021 to 2036

- Table 12: North America Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 13: North America Market Value (USD Million) Forecast by Process Stage, 2021 to 2036

- Table 14: North America Market Value (USD Million) Forecast by Fab Generation, 2021 to 2036

- Table 15: Latin America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 16: Latin America Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 17: Latin America Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 18: Latin America Market Value (USD Million) Forecast by Measurement Focus, 2021 to 2036

- Table 19: Latin America Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 20: Latin America Market Value (USD Million) Forecast by Process Stage, 2021 to 2036

- Table 21: Latin America Market Value (USD Million) Forecast by Fab Generation, 2021 to 2036

- Table 22: Western Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 23: Western Europe Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 24: Western Europe Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 25: Western Europe Market Value (USD Million) Forecast by Measurement Focus, 2021 to 2036

- Table 26: Western Europe Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 27: Western Europe Market Value (USD Million) Forecast by Process Stage, 2021 to 2036

- Table 28: Western Europe Market Value (USD Million) Forecast by Fab Generation, 2021 to 2036

- Table 29: Eastern Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 30: Eastern Europe Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 31: Eastern Europe Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 32: Eastern Europe Market Value (USD Million) Forecast by Measurement Focus, 2021 to 2036

- Table 33: Eastern Europe Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 34: Eastern Europe Market Value (USD Million) Forecast by Process Stage, 2021 to 2036

- Table 35: Eastern Europe Market Value (USD Million) Forecast by Fab Generation, 2021 to 2036

- Table 36: East Asia Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 37: East Asia Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 38: East Asia Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 39: East Asia Market Value (USD Million) Forecast by Measurement Focus, 2021 to 2036

- Table 40: East Asia Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 41: East Asia Market Value (USD Million) Forecast by Process Stage, 2021 to 2036

- Table 42: East Asia Market Value (USD Million) Forecast by Fab Generation, 2021 to 2036

- Table 43: South Asia and Pacific Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 44: South Asia and Pacific Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 45: South Asia and Pacific Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 46: South Asia and Pacific Market Value (USD Million) Forecast by Measurement Focus, 2021 to 2036

- Table 47: South Asia and Pacific Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 48: South Asia and Pacific Market Value (USD Million) Forecast by Process Stage, 2021 to 2036

- Table 49: South Asia and Pacific Market Value (USD Million) Forecast by Fab Generation, 2021 to 2036

- Table 50: Middle East & Africa Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 51: Middle East & Africa Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 52: Middle East & Africa Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 53: Middle East & Africa Market Value (USD Million) Forecast by Measurement Focus, 2021 to 2036

- Table 54: Middle East & Africa Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 55: Middle East & Africa Market Value (USD Million) Forecast by Process Stage, 2021 to 2036

- Table 56: Middle East & Africa Market Value (USD Million) Forecast by Fab Generation, 2021 to 2036

List of Figures

- Figure 1: Global Market Pricing Analysis

- Figure 2: Global Market Value (USD Million) Forecast 2021-2036

- Figure 3: Global Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 4: Global Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 5: Global Market Attractiveness Analysis by Technology Type

- Figure 6: Global Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 7: Global Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 8: Global Market Attractiveness Analysis by Deployment Mode

- Figure 9: Global Market Value Share and BPS Analysis by Measurement Focus, 2026 and 2036

- Figure 10: Global Market Y-o-Y Growth Comparison by Measurement Focus, 2026-2036

- Figure 11: Global Market Attractiveness Analysis by Measurement Focus

- Figure 12: Global Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 13: Global Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 14: Global Market Attractiveness Analysis by End User

- Figure 15: Global Market Value Share and BPS Analysis by Process Stage, 2026 and 2036

- Figure 16: Global Market Y-o-Y Growth Comparison by Process Stage, 2026-2036

- Figure 17: Global Market Attractiveness Analysis by Process Stage

- Figure 18: Global Market Value Share and BPS Analysis by Fab Generation, 2026 and 2036

- Figure 19: Global Market Y-o-Y Growth Comparison by Fab Generation, 2026-2036

- Figure 20: Global Market Attractiveness Analysis by Fab Generation

- Figure 21: Global Market Value (USD Million) Share and BPS Analysis by Region, 2026 and 2036

- Figure 22: Global Market Y-o-Y Growth Comparison by Region, 2026-2036

- Figure 23: Global Market Attractiveness Analysis by Region

- Figure 24: North America Market Incremental Dollar Opportunity, 2026-2036

- Figure 25: Latin America Market Incremental Dollar Opportunity, 2026-2036

- Figure 26: Western Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 27: Eastern Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 28: East Asia Market Incremental Dollar Opportunity, 2026-2036

- Figure 29: South Asia and Pacific Market Incremental Dollar Opportunity, 2026-2036

- Figure 30: Middle East & Africa Market Incremental Dollar Opportunity, 2026-2036

- Figure 31: North America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 32: North America Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 33: North America Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 34: North America Market Attractiveness Analysis by Technology Type

- Figure 35: North America Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 36: North America Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 37: North America Market Attractiveness Analysis by Deployment Mode

- Figure 38: North America Market Value Share and BPS Analysis by Measurement Focus, 2026 and 2036

- Figure 39: North America Market Y-o-Y Growth Comparison by Measurement Focus, 2026-2036

- Figure 40: North America Market Attractiveness Analysis by Measurement Focus

- Figure 41: North America Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 42: North America Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 43: North America Market Attractiveness Analysis by End User

- Figure 44: North America Market Value Share and BPS Analysis by Process Stage, 2026 and 2036

- Figure 45: North America Market Y-o-Y Growth Comparison by Process Stage, 2026-2036

- Figure 46: North America Market Attractiveness Analysis by Process Stage

- Figure 47: North America Market Value Share and BPS Analysis by Fab Generation, 2026 and 2036

- Figure 48: North America Market Y-o-Y Growth Comparison by Fab Generation, 2026-2036

- Figure 49: North America Market Attractiveness Analysis by Fab Generation

- Figure 50: Latin America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 51: Latin America Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 52: Latin America Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 53: Latin America Market Attractiveness Analysis by Technology Type

- Figure 54: Latin America Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 55: Latin America Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 56: Latin America Market Attractiveness Analysis by Deployment Mode

- Figure 57: Latin America Market Value Share and BPS Analysis by Measurement Focus, 2026 and 2036

- Figure 58: Latin America Market Y-o-Y Growth Comparison by Measurement Focus, 2026-2036

- Figure 59: Latin America Market Attractiveness Analysis by Measurement Focus

- Figure 60: Latin America Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 61: Latin America Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 62: Latin America Market Attractiveness Analysis by End User

- Figure 63: Latin America Market Value Share and BPS Analysis by Process Stage, 2026 and 2036

- Figure 64: Latin America Market Y-o-Y Growth Comparison by Process Stage, 2026-2036

- Figure 65: Latin America Market Attractiveness Analysis by Process Stage

- Figure 66: Latin America Market Value Share and BPS Analysis by Fab Generation, 2026 and 2036

- Figure 67: Latin America Market Y-o-Y Growth Comparison by Fab Generation, 2026-2036

- Figure 68: Latin America Market Attractiveness Analysis by Fab Generation

- Figure 69: Western Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 70: Western Europe Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 71: Western Europe Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 72: Western Europe Market Attractiveness Analysis by Technology Type

- Figure 73: Western Europe Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 74: Western Europe Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 75: Western Europe Market Attractiveness Analysis by Deployment Mode

- Figure 76: Western Europe Market Value Share and BPS Analysis by Measurement Focus, 2026 and 2036

- Figure 77: Western Europe Market Y-o-Y Growth Comparison by Measurement Focus, 2026-2036

- Figure 78: Western Europe Market Attractiveness Analysis by Measurement Focus

- Figure 79: Western Europe Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 80: Western Europe Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 81: Western Europe Market Attractiveness Analysis by End User

- Figure 82: Western Europe Market Value Share and BPS Analysis by Process Stage, 2026 and 2036

- Figure 83: Western Europe Market Y-o-Y Growth Comparison by Process Stage, 2026-2036

- Figure 84: Western Europe Market Attractiveness Analysis by Process Stage

- Figure 85: Western Europe Market Value Share and BPS Analysis by Fab Generation, 2026 and 2036

- Figure 86: Western Europe Market Y-o-Y Growth Comparison by Fab Generation, 2026-2036

- Figure 87: Western Europe Market Attractiveness Analysis by Fab Generation

- Figure 88: Eastern Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 89: Eastern Europe Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 90: Eastern Europe Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 91: Eastern Europe Market Attractiveness Analysis by Technology Type

- Figure 92: Eastern Europe Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 93: Eastern Europe Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 94: Eastern Europe Market Attractiveness Analysis by Deployment Mode

- Figure 95: Eastern Europe Market Value Share and BPS Analysis by Measurement Focus, 2026 and 2036

- Figure 96: Eastern Europe Market Y-o-Y Growth Comparison by Measurement Focus, 2026-2036

- Figure 97: Eastern Europe Market Attractiveness Analysis by Measurement Focus

- Figure 98: Eastern Europe Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 99: Eastern Europe Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 100: Eastern Europe Market Attractiveness Analysis by End User

- Figure 101: Eastern Europe Market Value Share and BPS Analysis by Process Stage, 2026 and 2036

- Figure 102: Eastern Europe Market Y-o-Y Growth Comparison by Process Stage, 2026-2036

- Figure 103: Eastern Europe Market Attractiveness Analysis by Process Stage

- Figure 104: Eastern Europe Market Value Share and BPS Analysis by Fab Generation, 2026 and 2036

- Figure 105: Eastern Europe Market Y-o-Y Growth Comparison by Fab Generation, 2026-2036

- Figure 106: Eastern Europe Market Attractiveness Analysis by Fab Generation

- Figure 107: East Asia Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 108: East Asia Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 109: East Asia Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 110: East Asia Market Attractiveness Analysis by Technology Type

- Figure 111: East Asia Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 112: East Asia Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 113: East Asia Market Attractiveness Analysis by Deployment Mode

- Figure 114: East Asia Market Value Share and BPS Analysis by Measurement Focus, 2026 and 2036

- Figure 115: East Asia Market Y-o-Y Growth Comparison by Measurement Focus, 2026-2036

- Figure 116: East Asia Market Attractiveness Analysis by Measurement Focus

- Figure 117: East Asia Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 118: East Asia Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 119: East Asia Market Attractiveness Analysis by End User

- Figure 120: East Asia Market Value Share and BPS Analysis by Process Stage, 2026 and 2036

- Figure 121: East Asia Market Y-o-Y Growth Comparison by Process Stage, 2026-2036

- Figure 122: East Asia Market Attractiveness Analysis by Process Stage

- Figure 123: East Asia Market Value Share and BPS Analysis by Fab Generation, 2026 and 2036

- Figure 124: East Asia Market Y-o-Y Growth Comparison by Fab Generation, 2026-2036

- Figure 125: East Asia Market Attractiveness Analysis by Fab Generation

- Figure 126: South Asia and Pacific Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 127: South Asia and Pacific Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 128: South Asia and Pacific Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 129: South Asia and Pacific Market Attractiveness Analysis by Technology Type

- Figure 130: South Asia and Pacific Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 131: South Asia and Pacific Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 132: South Asia and Pacific Market Attractiveness Analysis by Deployment Mode

- Figure 133: South Asia and Pacific Market Value Share and BPS Analysis by Measurement Focus, 2026 and 2036

- Figure 134: South Asia and Pacific Market Y-o-Y Growth Comparison by Measurement Focus, 2026-2036

- Figure 135: South Asia and Pacific Market Attractiveness Analysis by Measurement Focus

- Figure 136: South Asia and Pacific Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 137: South Asia and Pacific Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 138: South Asia and Pacific Market Attractiveness Analysis by End User

- Figure 139: South Asia and Pacific Market Value Share and BPS Analysis by Process Stage, 2026 and 2036

- Figure 140: South Asia and Pacific Market Y-o-Y Growth Comparison by Process Stage, 2026-2036

- Figure 141: South Asia and Pacific Market Attractiveness Analysis by Process Stage

- Figure 142: South Asia and Pacific Market Value Share and BPS Analysis by Fab Generation, 2026 and 2036

- Figure 143: South Asia and Pacific Market Y-o-Y Growth Comparison by Fab Generation, 2026-2036

- Figure 144: South Asia and Pacific Market Attractiveness Analysis by Fab Generation

- Figure 145: Middle East & Africa Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 146: Middle East & Africa Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 147: Middle East & Africa Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 148: Middle East & Africa Market Attractiveness Analysis by Technology Type

- Figure 149: Middle East & Africa Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 150: Middle East & Africa Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 151: Middle East & Africa Market Attractiveness Analysis by Deployment Mode

- Figure 152: Middle East & Africa Market Value Share and BPS Analysis by Measurement Focus, 2026 and 2036

- Figure 153: Middle East & Africa Market Y-o-Y Growth Comparison by Measurement Focus, 2026-2036

- Figure 154: Middle East & Africa Market Attractiveness Analysis by Measurement Focus

- Figure 155: Middle East & Africa Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 156: Middle East & Africa Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 157: Middle East & Africa Market Attractiveness Analysis by End User

- Figure 158: Middle East & Africa Market Value Share and BPS Analysis by Process Stage, 2026 and 2036

- Figure 159: Middle East & Africa Market Y-o-Y Growth Comparison by Process Stage, 2026-2036

- Figure 160: Middle East & Africa Market Attractiveness Analysis by Process Stage

- Figure 161: Middle East & Africa Market Value Share and BPS Analysis by Fab Generation, 2026 and 2036

- Figure 162: Middle East & Africa Market Y-o-Y Growth Comparison by Fab Generation, 2026-2036

- Figure 163: Middle East & Africa Market Attractiveness Analysis by Fab Generation

- Figure 164: Global Market - Tier Structure Analysis

- Figure 165: Global Market - Company Share Analysis

Full Research Suite comprises of:

Market outlook & trends analysis

Interviews & case studies

Strategic recommendations

Vendor profiles & capabilities analysis

5-year forecasts

8 regions and 60+ country-level data splits

Market segment data splits

12 months of continuous data updates

DELIVERED AS:

PDF EXCEL ONLINE