In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market

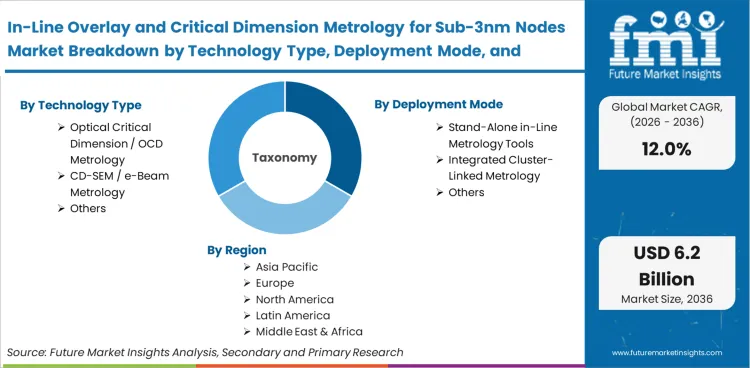

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market is segmented by Technology type (Optical critical dimension / OCD metrology, Overlay metrology systems, CD-SEM / e-beam metrology, Hybrid metrology software-linked platforms), Deployment mode (Stand-alone in-line metrology tools, Integrated cluster-linked metrology, Offline recipe-development metrology, Virtual metrology / model-assisted layers), Fab application (Lithography module control, Etch profile and line-shape control, Backside power / buried-feature verification, High-NA EUV process-window monitoring), End user (Pure-play foundries, Integrated device manufacturers, Leading-edge logic specialists, Research consortia / pilot lines), Node focus (2nm and equivalent GAA ramps, 3nm family production optimization, 18A / angstrom-class pilot and early HVM, Sub-3nm R&D and pathfinding flows), and Region. Forecast for 2026 to 2036.

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Size, Market Forecast and Outlook By FMI

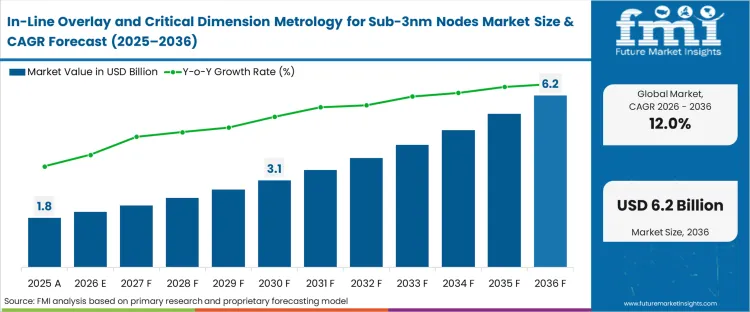

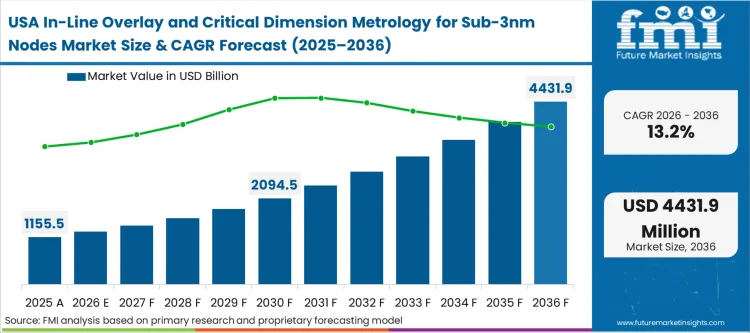

The in-line overlay and critical dimension metrology for sub-3nm nodes market was valued at USD 1.8 billion in 2025. Demand within the sub-3nm overlay metrology market is poised to cross USD 2.0 billion in 2026 at a CAGR of 12.00% during this forecast period. Continued investment is expected to drive total revenue in the sub‑3nm critical dimension metrology market to USD 6.3 billion by 2036, as increasingly stringent sub‑angstrom defect tolerances push fabs to transition from sampling-based inspection toward large‑scale computational metrology.

Sub-3nm architecture transitions from FinFET to gate-all-around nanosheets compress overlay error budgets below 2 nanometers, driving the advanced-node overlay metrology market. Yield-control directors at leading-edge fabs face an immediate commercial ultimatum: either deploy high-frequency inline measurement loops across every critical lithography equipment pass, or suffer catastrophic multi-wafer scrap events when hidden buried-feature defects cascade through subsequent deposition steps. What generalist observers miss about process control for 2nm chips is how this transition moves value capture away from raw imaging resolution toward multi-sensor data fusion capabilities.

Summary of In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market

- In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Definition

- Highly specialized measurement hardware and software platforms characterize this capital equipment category, designed exclusively to verify nanometer-scale geometry and layer alignment during advanced semiconductor manufacturing within active production lines.

- Demand Drivers in the Market

- Multi-patterning complexity forces yield-control directors to triple measurement frequency per wafer pass.

- Backside power delivery network transitions compel metrology engineers to adopt entirely novel buried-feature verification techniques.

- Extreme ultraviolet lithography stochastics push process-control managers toward massive parallel computational inspection architectures.

- Key Segments Analyzed in the FMI Report

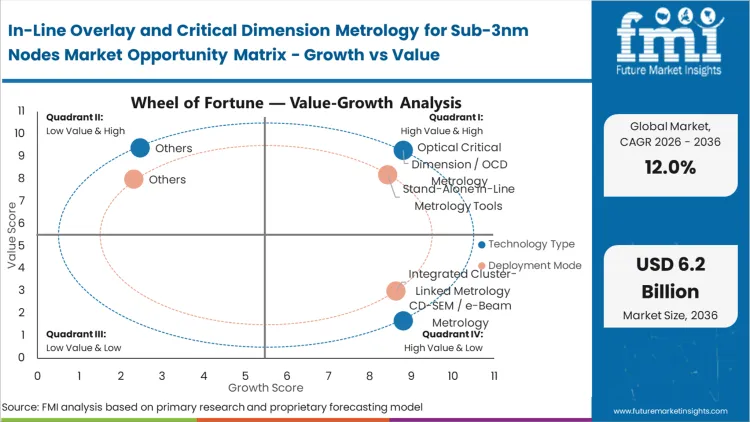

- Optical critical dimension / OCD metrology is projected to capture 39.0% share in 2026, driven by unparalleled throughput speeds required for continuous production monitoring.

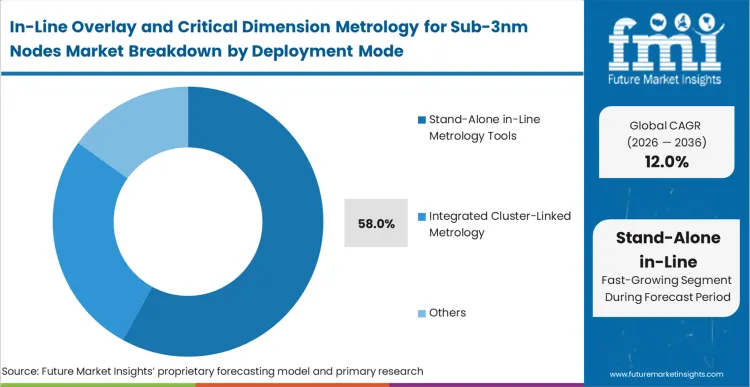

- Stand-alone in-line metrology tools is anticipated to lead deployment modes through 2036, reflecting strict vibration isolation requirements inherent in sub-angstrom measurement tasks.

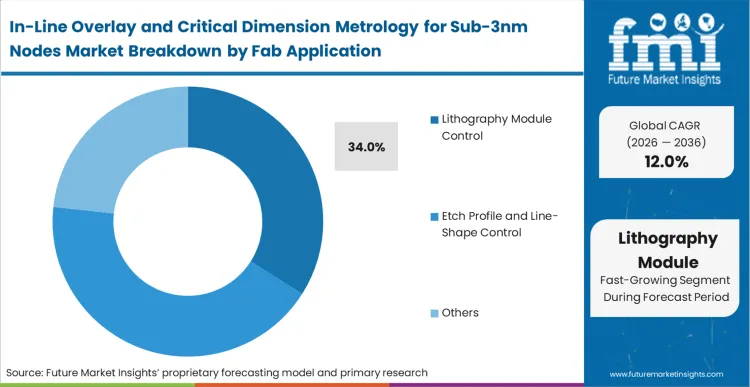

- Lithography module control is poised to hold 34.0% share in 2026 as photoresist exposure tolerances shrink exponentially.

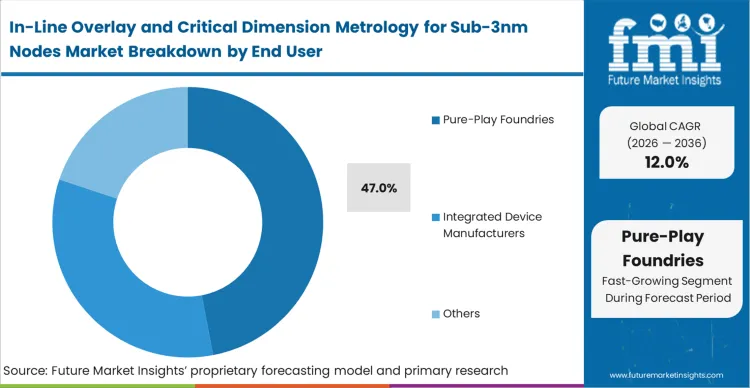

- Pure-play foundries is set to command 47.0% share in 2026, matching their dominance in bleeding-edge gate-all-around transistor commercialization efforts.

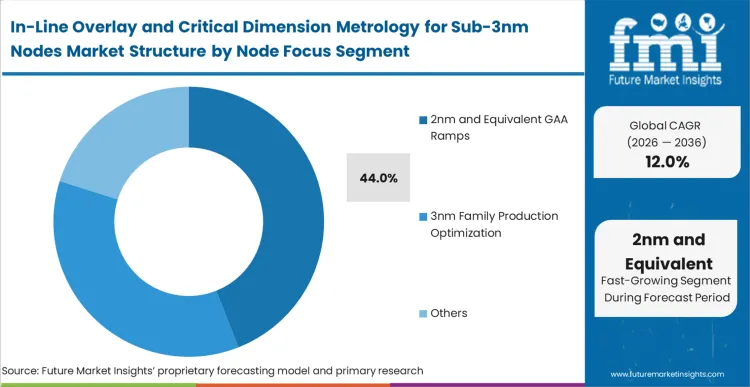

- 2nm and equivalent GAA ramps is expected to dominate with 44.0% share in 2026 as major logic producers transition from pathfinding into early high-volume manufacturing.

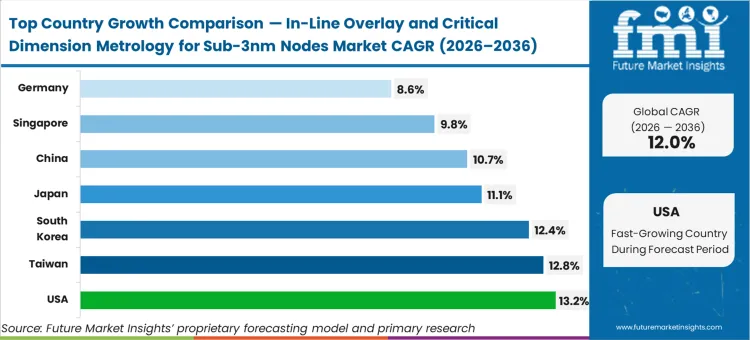

- United States 13.2% compound growth, sustained by massive strategic fab construction initiatives funded through aggressive domestic policy incentives.

- Analyst Opinion at FMI

- Rahul Pandita, Principal Analyst, Technology, at FMI, notes that, "Generalist narratives assume hardware resolution defines metrology leadership in gate-all-around nodes. Sheer algorithmic fusion dictates yield success today. Tool accuracy means nothing if a fab cannot process petabytes of scatterometry data fast enough to adjust etch parameters before next wafer lots arrive. We see foundries accepting slightly lower raw optical resolution in exchange for vastly superior machine-learning feed-forward loops."

- Strategic Implications / Executive Takeaways

- Yield-control directors must prioritize software-integration capabilities over isolated hardware specifications to prevent data-processing bottlenecks.

- Metrology fleet managers face intense pressure to hybridize measurement workflows, combining optical speed with e-beam precision.

- Procurement leaders risk severe capacity constraints if they delay multi-year purchase orders for critical extreme ultraviolet-compatible inspection platforms.

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Key Takeaways

| Metric | Details |

|---|---|

| Industry Size (2026) | USD 2.0 billion |

| Industry Value (2036) | USD 6.3 billion |

| CAGR (2026 to 2036) | 12.00% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Process-window qualification times dictate ultimate foundry competitiveness in angstrom-class nodes. Once a logic manufacturer successfully correlates sparse scanning electron microscope baseline data with dense semiconductor metrology scatterometry streams, yield-ramp cycles accelerate dramatically. Foundries crossing this hybrid-metrology integration threshold routinely slash defect root-cause analysis periods from weeks to mere hours.

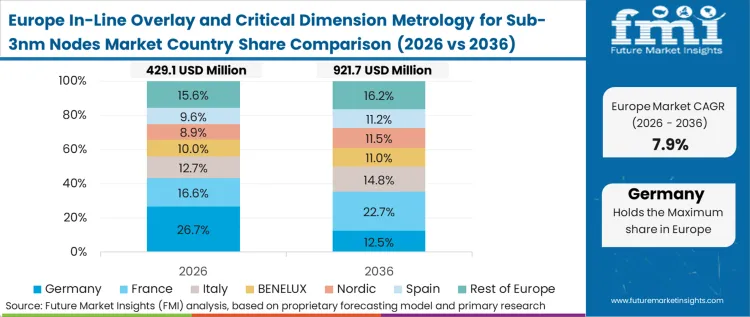

The trajectory of how fast is the sub-3nm metrology market growing is directly tied to United States logic producers, who drive demand at 13.2% as aggressive domestic fab construction schedules mandate massive simultaneous tool installations. Taiwan follows closely at 12.8% on continuous yield optimization requirements across established 3nm manufacturing lines. South Korea tracks at 12.4% due to early memory-to-logic cross-pollination efforts. Japan outpaces broader semiconductor capital equipment baselines at 11.1% while Rapidus accelerates specific 2nm pathfinding workflows. China advances at 10.7% under intense domestic supply chain localization pressures. Singapore expands at 9.8% alongside steady packaging innovations. Germany registers 8.6% growth as automotive-grade precision filters into legacy infrastructure overhauls.

Market Definition

Defining what is overlay metrology in sub-3nm semiconductor manufacturing requires examining functional boundary parameters that isolate this specific class of capital equipment as precisely calibrated measurement hardware and integrated algorithms designed strictly for sub-3nm fabrication workflows. This tier of technology quantifies nanometer-scale feature variations, layer-to-layer alignments, and complex 3D transistor geometries immediately after critical processing steps.

Inclusions

Scope strictly covers inline overlay and CD metrology platforms, optical scatterometry tools, automated semiconductor defect inspection platforms, scanning electron microscopes configured for critical dimension measurement, and integrated algorithmic platforms that fuse multi-sensor output. Hardware components spanning acoustic monitoring sensors, advanced vacuum chucks, and precision stage mechanisms fall within boundaries when sold directly as integrated upgrades.

Exclusions

Standalone offline laboratory microscopy suites sit outside analytical boundaries because they fail to meet inline throughput requirements for mass production. Bare silicon substrate preparation metrics and final packaged-chip testing procedures are excluded as they address fundamentally different phases of semiconductor creation. Reagents and chemical mechanical planarization slurries used during actual wafer shaping are similarly omitted since they constitute consumables rather than permanent measurement capital.

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Research Methodology

- Primary Research: Procurement directors at pure-play foundries and advanced packaging engineering leads provide ground-truth insight into hardware qualification cycles.

- Desk Research: Vendor 10-K filings, SPIE conference technical proceedings, and IRDS roadmap documentation anchor baseline technical capability claims.

- Market-Sizing and Forecasting: Fab utilization rates and publicly announced multi-billion-dollar greenfield logic plant construction schedules serve as primary quantitative anchors.

- Data Validation and Update Cycle: Independent semiconductor equipment billing reports from regional industry associations cross-validate aggregated supplier revenue declarations.

Segmental Analysis

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis by Technology Type

Throughput economics explain why Optical critical dimension / OCD metrology dominates baseline fab operations, even as engineers expand the semiconductor CD-SEM market. When buyers evaluate optical metrology vs e-beam metrology, FMI's analysis indicates this modality commands 39.0% share because yield-control directors cannot afford massive vacuum-pumping delays associated with electron beam physics across every single wafer slot. Optical scatterometry captures immense dimensional data instantly without destroying delicate photoresist structures.

Fab operators evaluating OCD vs CD-SEM for 2nm manufacturing sacrifice absolute atomic-level imaging for statistically significant multi-parameter profiles. Answering how does inline OCD differ from CD-SEM, observers must recognize how heavily this optical dominance relies on advanced computational inverse-modeling rather than purely superior lenses. Metrology fleet managers who over-index on slower electron-beam solutions inevitably throttle entire multi-billion-dollar production lines, turning metrology software platforms into catastrophic factory bottlenecks.

- Throughput optimization: Instantaneous photon scattering profiles allow continuous wafer scanning without vacuum-chamber staging delays. Yield-control directors gain statistical confidence across full wafer maps rather than isolated die locations.

- Algorithmic dependency: Inverse-modeling algorithms reconstruct physical transistor shapes from complex light interference signatures. Software engineers face continuous pressure to update these mathematical libraries for every new layout geometry.

- Yield-loss prevention: Non-destructive optical inspection prevents delicate photoresist degradation during measurement cycles. Lithography module owners avoid chemically altering pristine patterns before final etch stages commence.

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis by Deployment Mode

Next-generation transistor architectures brutally expose hidden limitations inside integrated track-based measurement systems. When assessing inline metrology vs offline metrology semiconductor architectures, stand-alone in-line metrology tools secure 58.0% share. FMI observes that this configuration isolates delicate optics from aggressive mechanical vibrations inherent in surrounding wet-clean or deposition equipment. Module owners configuring wafer processing equipment must route critical layers through dedicated standalone measurement bays to achieve sub-angstrom repeatability. Physics dictates this separation: acoustic energy from adjacent pumps destroys extreme ultraviolet overlay budgets instantly. One irony inside modern foundries is that as process integration tightens, measurement hardware must become physically more isolated to function. Fab layout architects who mistakenly prioritize cluster-tool space savings over standalone vibration isolation routinely fail to achieve baseline qualification metrics during initial pilot runs.

- Acoustic isolation: Dedicated granite isolation tables separate sensitive measurement optics from factory floor vibrations. Fab layout architects ensure sub-nanometer stability during prolonged scanning electron microscopy sessions.

- Fleet routing flexibility: Standalone configurations permit dynamic lot routing when specific inspection tools require unexpected calibration. Production managers avoid halting entire deposition clusters merely because one optical sensor drifts out of specification.

- Calibration stability: Thermal and environmental controls inside standalone chassis operate independently from surrounding process tools. Metrology technicians maintain pristine baseline accuracy over extended operational changes.

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis by Fab Application

High-NA exposure stochastics constantly battle against chemically amplified resist limitations, driving urgent demand for high-NA EUV overlay measurement systems. Lithography module control holds 34.0% share as patterning engineers frantically track in-device overlay measurement after etch before committing wafers to irreversible plasma etching. Based on FMI's projection, procurement teams seeking the best overlay metrology system for high-NA EUV face massive capital requirements due to sheer measurement repetition. Wafers circulate through lithography bays up to thirty separate times for multi-patterned logic designs to ensure strict overlay control for EUV lithography. While euv lithography equipment suppliers advertise sub-nanometer capabilities, practical factory implementation often reveals that thermal expansion of silicon substrates itself consumes half allowable error budgets. Etch module owners conducting wafer-level CD uniformity monitoring face impossible geometry correction tasks if initial lithography metrology fails.

- Pre-etch validation: Edge placement error quantification occurs immediately after photoresist development but before plasma transfer. Lithography module owners authorize lot continuation or mandate costly chemical stripping and rework protocols.

- Thermal drift compensation: Continuous alignment marker scanning feeds real-time correction coordinates directly back into scanner software. Patterning engineers mitigate microscopic wafer expansion caused by intense ambient fab energy loads.

- Overlay verification: Multi-layer registration checks confirm that new transistor vias land precisely atop buried interconnect trenches. Yield-control directors prevent catastrophic electrical short circuits from ruining entire production batches.

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis by End user

Bleeding-edge logic architects within the foundry metrology equipment market face brutal capital allocation choices regarding pathfinding measurement capability versus immediate capacity expansion. Pure-play foundries maintain 47.0% share, reflecting the massive concentration of sub-3nm production volume within just two or three global manufacturing giants. According to FMI's estimates, these elite operators effectively dictate hardware roadmaps for all sub-3nm metrology equipment suppliers and inline overlay metrology system vendors. They demand highly customised hybrid metrology architectures that fuse optical and electron-beam data seamlessly across semiconductor manufacturing equipment suites.

This dynamic shapes the entire landscape for logic semiconductor process control tools. Interestingly, while smaller integrated device manufacturers wait for standardized commercial inspection recipes, dominant foundries employ hundreds of dedicated data scientists purely to write proprietary machine-learning metrology models. Tool suppliers who fail to secure early evaluation slots within these specific pure-play foundry pilot lines essentially forfeit any chance of participating in subsequent high-volume manufacturing deployments.

- Roadmap dictation: Massive capital expenditures allow leading manufacturers to demand bespoke sensor configurations from tier-one equipment suppliers. Procurement directors leverage immense purchasing power to monopolize early deliveries of next-generation metrology platforms.

- Algorithm customization: Proprietary machine-learning models interpret raw scatterometry data using highly classified factory baseline metrics. Data scientists optimize yield curves faster than competitors relying solely on generic vendor software packages.

- Pilot qualification: Early beta-tool installations generate critical feedback loops for hardware refinement. Foundries capture first-mover cost advantages while suppliers gain necessary field validation data.

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis by Node Focus

To explain the inline overlay metrology market for 2nm fabs, gate-all-around transistor geometry entirely redefines traditional cross-sectional measurement paradigms. Engineers deploying 2nm overlay metrology tools command 44.0% share, driven by module owners struggling to verify buried epitaxial cavity depths using conventional top-down imaging. FMI analysts note that this node generation forces a permanent switch toward multi-sensor hybrid metrology arrays. This explicitly answers why is critical dimension metrology essential at 2nm nodes.

Nanosheet architectures contain hidden vertical profiles that remain completely invisible to standard wafer manufacturing equipment scattering techniques. Operators rely heavily on GAA transistor CD metrology and critical dimension monitoring for nanosheet transistors because 2nm yield optimization depends more on destructive transmission electron microscopy calibration than fab managers openly admit. Operators attempting to scale 2nm production using legacy 3nm inline measurement strategies encounter massive invisible defect cascades during middle-of-line metallization.

- Buried feature analysis: Multi-wavelength optical platforms attempt to penetrate upper silicon layers to measure lower nanosheet dimensions. Metrology engineers struggle to separate legitimate signals from background crystalline noise.

- Virtual modeling: Machine learning algorithms predict unmeasurable internal transistor dimensions based on peripheral surface indicators. Yield-control directors bridge physical hardware limitations using aggressive computational inference strategies.

- Destructive calibration: Frequent wafer cross-sectioning provides necessary ground-truth data to anchor inline optical algorithms. Failure analysis labs face immense throughput pressure to return baseline coordinates to active production floors quickly.

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Drivers, Restraints, and Opportunities

Backside power delivery network transitions strictly force yield-control directors to adopt completely novel metrology for backside power delivery immediately, driving demand for buried feature overlay metrology. This change buries critical interconnects beneath semiconductor wafers, rendering traditional top-down optical inspection entirely blind. Fab operators must deploy infrared-transparent metrology solutions or face catastrophic misalignment when attempting to connect microscopic front-side transistors to hidden rear-side power rails. Delaying this equipment upgrade guarantees zero-percent yield on advanced logic designs, as blind via-drilling inevitably destroys active device channels. Compression timelines act ruthlessly, forcing procurement teams to secure limited infrared metrology tool allocations years before actual fab construction finishes.

Algorithmic training data scarcity restricts rapid virtual metrology deployment across new node generations. Foundries want machine-learning models to predict complex transistor shapes instantly, but these algorithms require thousands of perfectly annotated destructive cross-sections to achieve baseline accuracy. Yield-control engineers cannot generate this physical ground-truth data without sacrificing highly expensive processed silicon. Calibration friction persists because every minor photoresist electronic chemical tweak alters optical scatterometry signatures, instantly invalidating existing predictive models. While hybrid platforms attempt to simulate these variations computationally, fab managers still require months of slow physical iterative testing to trust new automated recipes entirely.

Opportunities in the In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market

- EUV stochastic monitoring: Module owners require dedicated fast-scanning defect platforms capable of differentiating true particle contamination from photoresist ancillary chemicals printing failures.

- Emerging architecture tracking: CFET inline OCD metrology and nanosheet transistor metrology architectures present lucrative avenues for bridging high-resolution direct write semiconductor imaging with commercial throughput.

- AI-driven recipe generation: Software engineers face immense demand for generative algorithms that automatically create optical scatterometry models, eliminating weeks of manual advanced packaging measurement tuning.

Regional Analysis

Based on regional analysis, In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes is segmented into North America, Latin America, Europe, East Asia, South Asia & Pacific, and Middle East & Africa across 40 plus countries.

.webp)

| Country | CAGR (2026 to 2036) |

|---|---|

| United States | 13.2% |

| Taiwan | 12.8% |

| South Korea | 12.4% |

| Japan | 11.1% |

| China | 10.7% |

| Singapore | 9.8% |

| Germany | 8.6% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

North America In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis

Massive strategic fab construction initiatives define the US 18A metrology equipment market and surrounding North American procurement cycles. Major foundry operators building greenfield sites across this region completely bypass legacy equipment upgrades, opting instead to install purely sub-3nm capable baseline fleets. Procurement directors orchestrate these multi-billion-dollar tool move-ins simultaneously, creating unprecedented logistical pressure on global metrology suppliers. FMI observes that this concentrated burst of leading-edge hardware deployment forces tool vendors to permanently relocate their most experienced application engineers directly to these new facility clusters. Success here hinges entirely on software integration speed, as empty cleanrooms transition into high-volume logic manufacturing hubs over severely compressed timelines.

- United States: Strict localised supply chain mandates force domestic pure-play foundries to aggressively adopt extreme ultraviolet-compatible wafer inspection system hardware immediately. Consequently, the United States In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes industry registers an impressive 13.2% compound growth through 2036. Procurement directors actively lock in multi-year service contracts alongside massive initial tool purchases, directly securing long-term strategic silicon independence for domestic fab operators.

East Asia In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis

Relentless yield optimization across established 3nm lines and aggressive gate-all-around pilot pathfinding completely dominate East Asian metrology dynamics. Fab module owners in this territory process immense volumes of leading-edge wafers daily, generating unprecedented amounts of scatterometry data. Based on FMI's assessment, this massive operational scale allows regional foundries to push optical metrology algorithms far beyond standard vendor specifications. Local engineering teams write proprietary machine-learning extensions that extract deeper geometric insights from standard optical signals. Fierce technological cross-pollination between high-bandwidth memory architectures and angstrom-class logic nodes creates uniquely demanding environments for next-generation semiconductor packaging measurement hardware evaluation.

- Taiwan: The relentless operational scale drives the Taiwan In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes expands at a 12.8% CAGR. Yield-control directors managing existing massive 3nm logic output strictly enforce sub-nanometer overlay budgets across continuous multi-wafer runs. Regional operators continuously upgrade inline optical algorithms, maintaining dominant commercial wafer-pricing leverage globally while pushing standard optical hardware significantly beyond official factory measurement limits.

- South Korea: Memory-to-logic architectural convergence forces local metrology engineers to dramatically adapt high-aspect-ratio trench measurement techniques for novel gate-all-around nanosheet inspection. Driven by this workflow cross-pollination, the South Korea In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes segment advances at a 12.4% CAGR. This specialised capability allows local integrated device manufacturers to accelerate 2nm pilot yields remarkably fast, securing vital competitive positioning against dominant pure-play foundries.

- Japan: Rapidus-led pilot-line pathfinding workflows specifically targeting 2nm commercialization compel regional researchers to rapidly adopt novel hybrid e-beam platforms. Propelled by this targeted technological leapfrogging, the Japan In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes sector expands at an 11.1% CAGR. This highly focused investment successfully positions domestic consortiums to confidently re-enter extreme leading-edge logic competition, capturing lucrative pathfinding contracts globally before high-volume manufacturing begins.

- China: The In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes industry in China advances at a 10.7% CAGR. Intense domestic supply chain localization pressure compels fab operators to creatively maximize yield using highly restricted multi-patterning lithography fleets. Local yield engineers actively compensate for absent extreme ultraviolet tools by over-indexing heavily on rigorous computational inline measurement, pushing legacy inspection hardware to absolute theoretical geometric resolution limits.

Europe and Southeast Asia In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis

Automotive-grade precision requirements and heterogeneous integration innovations drive metrology upgrades across these geographically distinct but operationally linked specialty hubs. Fab managers face strict sub-nanometer tolerance mandates driven by complex automotive silicon and dense packaging schemes. FMI analysts note that older analog-focused foundries unexpectedly procure leading-edge scatterometry platforms just to verify highly complex semiconductor bonding equipment interconnects reliably. Metrology budgets here expand through aggressive horizontal diffusion of advanced measurement requirements into specialty technology nodes and backend processing centers.

- Singapore: Steady heterogeneous integration innovations compel advanced packaging engineers to aggressively adopt front-end-grade optical overlay tools for complex multi-die alignment verification. Reflecting this specific technical switch, the Singapore In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes segment tracks at a 9.8% CAGR. Local operators executing these advanced measurement workflows successfully secure highly lucrative specialty integration contracts from global logic designers demanding sub-nanometer verification.

- Germany: Facility directors retrofitting established automotive semiconductor lines suddenly face severe acoustic isolation challenges when installing modern high-precision scatterometry tools. Overcoming these infrastructure hurdles helps the Germany In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes industry register an 8.6% CAGR. These operators successfully transition mature fabrication facilities into highly profitable speciality node production centers, leveraging extreme measurement precision to guarantee critical automotive-grade silicon reliability.

FMI's report includes detailed metrology adoption models for Israel, France, Malaysia, and Ireland. Secondary logic manufacturing centers globally confront similar threshold pressures, discovering that legacy inspection hardware simply cannot resolve advanced node defect signatures. Fab managers in these emerging technology clusters consistently underestimate massive data-processing infrastructure requirements necessary to support modern metrology fleets, often stalling otherwise successful capacity expansions.

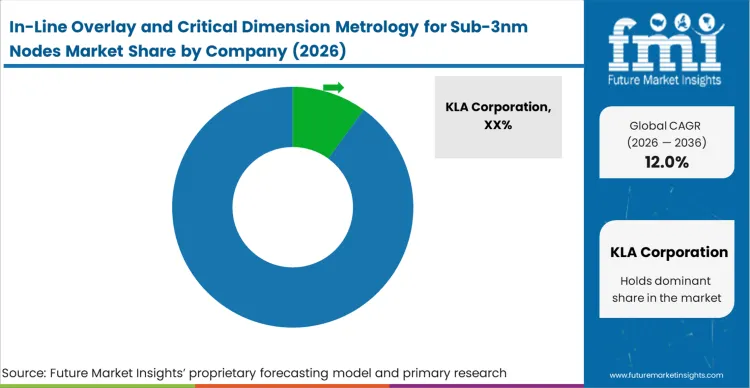

Competitive Aligners for Market Players

When evaluating what are the leading sub-3nm metrology vendors, immense technological barriers dictate competitive survival where hardware resolution alone no longer guarantees tool placement inside sub-3nm fabs. Leading equipment vendors secure their positions not merely through superior electron-beam optics, but by commanding dominant machine-learning software ecosystems that ingest raw factory data faster than rivals. KLA Corporation and ASML Holding N.V. aggressively cross-link their optical scatterometry and semiconductor inspection system hardware. Fab operators who compare optical CD metrology and e-beam metrology for 2nm force yield-control directors to buy integrated metrology suites rather than piecemeal standalone tools. This specific architectural lock-in occurs precisely because standalone instruments struggle to contextualize random stochastic defects without accessing proprietary lithography baseline models.

As buyers evaluate yieldstar vs archer overlay metrology (or other semiconductor yieldstar alternatives), incumbent equipment providers protect their dominant shares by hoarding massive proprietary libraries of destructive cross-section training data. Challengers attempting to introduce novel multi-beam electron photomask inspection systems face rigorous metrology tool qualification for 2nm fab environments, creating brutal qualification headwinds; fab operators refuse to deploy new hardware unless its predictive algorithms already perfectly match existing legacy baselines. Nova Ltd. and Onto Innovation Inc. navigate this friction by focusing intensely on advanced computational models that require significantly less physical calibration silicon, effectively lowering evaluation costs for hesitant procurement teams.

Procurement directors systematically resist encroaching single-vendor software lock-in by aggressively funding open-source metrology data standard initiatives. Major foundries deliberately split their extreme ultraviolet lithography monitoring fleets across multiple hardware suppliers, intentionally running overlapping optical and e-beam systems to maintain commercial leverage during service contract negotiations. Structural realities dictate that future angstrom-class yield optimization requires unprecedented multi-sensor data fusion, compelling fiercely competitive equipment vendors to reluctantly open their application programming interfaces to third-party advanced analytics platforms.

Key Players in In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market

- KLA Corporation

- ASML Holding N.V.

- Nova Ltd.

- Onto Innovation Inc.

- Applied Materials, Inc.

- Hitachi High-Tech Corporation

- SCREEN Semiconductor Solutions Co., Ltd.

Scope of the Report

| Metric | Value |

|---|---|

| Quantitative Units | USD 2.0 billion in 2026 to USD 6.3 billion by 2036, at a CAGR of 12.00% |

| Market Definition | Functional boundary parameters define this specific class of capital equipment as precisely calibrated measurement hardware and integrated algorithms designed strictly for sub-3nm semiconductor fabrication workflows. This tier of technology quantifies nanometer-scale feature variations, layer-to-layer alignments, and complex 3D transistor geometries immediately after critical processing steps. Tooling must operate continuously within high-volume manufacturing environments without breaking vacuum or delaying adjacent wafer transport mechanisms. |

| Segmentation | By Technology type, Deployment mode, Fab application, End user, Node focus, Measurement target, Metrology engine, Region |

| Regions Covered | North America, Latin America, Europe, East Asia, South Asia & Pacific, Middle East & Africa |

| Countries Covered | United States, Taiwan, South Korea, Japan, China, Singapore, Germany |

| Key Companies Profiled | KLA Corporation, ASML Holding N.V., Nova Ltd., Onto Innovation Inc., Applied Materials, Inc., Hitachi High-Tech Corporation, SCREEN Semiconductor Solutions Co., Ltd. |

| Forecast Period | 2026 to 2036 |

| Approach | Bottom-up aggregation of global advanced node wafer start projections. |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

In-Line Overlay and Critical Dimension Metrology for Sub-3nm Nodes Market Analysis by Segments

Technology type:

- Optical critical dimension / OCD metrology

- Overlay metrology systems

- CD-SEM / e-beam metrology

- Hybrid metrology software-linked platforms

Deployment mode:

- Stand-alone in-line metrology tools

- Integrated cluster-linked metrology

- Offline recipe-development metrology

- Virtual metrology / model-assisted layers

Fab application:

- Lithography module control

- Etch profile and line-shape control

- Backside power / buried-feature verification

- High-NA EUV process-window monitoring

End user:

- Pure-play foundries

- Integrated device manufacturers

- Leading-edge logic specialists

- Research consortia / pilot lines

Node focus:

- 2nm and equivalent GAA ramps

- 3nm family production optimization

- 18A / angstrom-class pilot and early HVM

- Sub-3nm R&D and pathfinding flows

Measurement target:

- In-device overlay

- Post-etch overlay

- Line width/CD

- Sidewall/profile CD

- Buried-feature CD

Metrology engine:

- Imaging-based

- Scatterometry-based

- SEM-based

- Multi-sensor hybrid

- ML-assisted virtual metrology

Region:

- North America

- United States

- Canada

- Europe

- Germany

- United Kingdom

- France

- Italy

- Spain

- Asia Pacific

- China

- Japan

- South Korea

- Taiwan

- Singapore

- Latin America

- Brazil

- Mexico

- Argentina

- Middle East & Africa

- GCC Countries

- South Africa

Bibliography

- International Roadmap for Devices and Systems. (2024). Metrology. IEEE IRDS.

- International Roadmap for Devices and Systems. (2024). Yield enhancement. IEEE IRDS.

- Kahn, J. (2025). Semiconductors and microelectronics standards working group annual report for 2024 (NIST Interagency/Internal Report 8577). National Institute of Standards and Technology.

- National Institute of Standards and Technology. (2024, February 22). Advanced metrology to enable next generation EUV photoresists.

- Secula, E., & Liddle, J. (2024, December 5). Frontiers of characterization and metrology for nanoelectronics: 2024. National Institute of Standards and Technology.

- Schmidt, D. (2024, April 15). In-line metrology for sub-2nm technology nodes [Invited talk, FCMN 2024]. IBM Research.

- Lorusso, G. F. (2024, April). Trends in e-beam metrology and inspection. In Metrology, Inspection, and Process Control XXXVIII (Proceedings of SPIE).

- van Schoot, J., van Ballegoij, R., Butler, H., & van Setten, E. (2024, December). Next step in Moore’s law: High NA EUV system overview and first imaging and overlay performance. Journal of Micro/Nanopatterning, Materials, and Metrology, 24(1), 011009.

- Ronse, K. (2024, June). Continued dimensional scaling through projection lithography. Micro and Nano Engineering, 23, 100263.

- Barnes, B., Chew, A., Jenkins, N., Shao, Y., Sohn, M., Kline, R., Sunday, D., Balakrishnan, P., Germer, T., Grantham, S., Klein, C., Moffitt, S., Shirley, E., Kapteyn, H., & Murnane, M. (2025, April). Lab-based multi-wavelength EUV diffractometry for critical dimension metrology. In Metrology, Inspection, and Process Control XXXIX (Proceedings of SPIE).

This bibliography is provided for reader reference. The full FMI report contains the complete reference list with primary source documentation.

Frequently Asked Questions

What is the difference between overlay metrology and critical dimension metrology at sub-3nm nodes?

Overlay metrology strictly measures layer-to-layer alignment registration to prevent electrical short circuits between interconnects. Critical dimension metrology quantifies the absolute physical width and geometric profile of individual printed transistor features to ensure consistent electrical performance across the wafer.

Why does sub-3nm manufacturing require more metrology intensity than 5nm or 7nm?

Sub-angstrom error margins in gate-all-around architectures force module owners to measure exponentially more frequently. Multi-patterning schemes at sub-3nm nodes require wafers to pass through lithography cells dozens of times, with each pass demanding immediate edge-placement verification to prevent cascading yield failures.

Which companies lead the in-line overlay and CD metrology market?

Leading equipment suppliers heavily driving sub-3nm process control include KLA Corporation, ASML Holding N.V., Nova Ltd., Onto Innovation Inc., Applied Materials, Inc., and Hitachi High-Tech Corporation, each securing positions through sophisticated algorithmic fusion and hardware precision.

How large is the sub-3nm metrology market in 2025, 2026, and 2036?

FMI calculates baseline valuation at USD 1.8 billion in 2025 and USD 2.0 billion in 2026. This figure reflects intense capital concentration, propelling cumulative revenue to USD 6.3 billion by 2036 as fab operators overhaul legacy measurement fleets completely.

What role does high-NA EUV play in future overlay measurement demand?

High-NA EUV introduces severe depth-of-focus constraints and stochastic photoresist printing errors. Patterning engineers require exceptionally fast imaging algorithms to catch these microscopic chemical failures, forcing equipment vendors to deploy massive parallel processing servers specifically for EUV process-window monitoring.

Why are foundries the largest buyers of sub-3nm metrology systems?

Massive capital scale allows just two or three global pure-play foundries to effectively monopolize early deliveries of next-generation hybrid measurement platforms. They dictate hardware roadmaps because sub-3nm production volume is overwhelmingly concentrated within their specialized mega-fab networks.

How do optical metrology and e-beam metrology compare for advanced nodes?

Optical scatterometry provides instantaneous high-throughput wafer scanning necessary for active production lines but sacrifices absolute atomic imaging. Electron-beam (e-beam) metrology delivers true nanometer-level resolution but imposes catastrophic vacuum-chamber delays, restricting its use primarily to highly targeted sampling or destructive calibration.

Which countries will grow fastest in advanced-node metrology demand?

The United States leads at 13.2% compound growth driven by massive greenfield fab construction. Taiwan and South Korea follow closely at 12.8% and 12.4% respectively, fueled by relentless yield optimization across existing high-volume logic manufacturing lines.

How does CD-SEM fit alongside OCD and hybrid metrology?

CD-SEM provides the vital high-resolution physical ground-truth data required to continuously train and calibrate optical critical dimension (OCD) inverse-modeling algorithms. Hybrid metrology platforms fuse these two distinct data streams, allowing foundries to predict unmeasurable geometries computationally.

What fab applications create the highest demand for inline overlay control?

Lithography module control consumes massive portions of fab metrology budgets due to sheer repetition. Wafers circulate through exposure bays up to thirty separate times, requiring constant alignment marker scanning to feed real-time correction coordinates back into the scanner software.

Can optical metrology still work below 3nm?

Yes, but only through extreme reliance on machine-learning inference. Optical wavelengths physically cannot resolve angstrom-class nanosheet features directly; instead, complex algorithms predict internal transistor dimensions based on peripheral surface light-scattering signatures, bridging the physical hardware limitation.

What drives demand for standalone deployment architectures?

Advanced optics require absolute granite-table acoustic isolation to capture sub-angstrom variations accurately. Standalone configurations physically shield highly sensitive measurement lasers from aggressive mechanical vibrations generated by adjacent multi-chamber deposition and chemical mechanical planarization cluster tools.

What shift occurs during 2nm gate-all-around transitions?

Nanosheet geometry introduces complex vertical profiles completely invisible to traditional top-down scanning microscopes. Metrology engineers must implement highly experimental multi-wavelength infrared techniques just to verify internal cavity depths without physically slicing silicon wafers open.

How does United States metrology trajectory differ from South Korea?

American procurement relies on massive simultaneous greenfield tool installations driven by strict domestic localization mandates. Conversely, South Korean expansion depends heavily on adapting highly refined memory-trench inspection techniques directly into emerging leading-edge logic pilot-line workflows.

Why is algorithmic training data considered a major adoption friction?

Machine-learning defect predictors require thousands of perfectly annotated physical cross-sections to establish baseline operational accuracy. Fab managers struggle to generate this necessary ground-truth data without intentionally sacrificing highly expensive processed silicon batches during initial node ramp-up phases.

What forces integration of multi-beam electron systems?

Traditional single-beam microscopes simply scan too slowly to capture statistically relevant defect data across modern massive 300mm wafer maps. Fleet managers actively sponsor multi-beam development to finally blend high-resolution atomic imaging with commercially viable inline factory throughput speeds.

How do backside power architectures impact measurement strategies?

Moving power delivery networks beneath active device layers completely obfuscates critical alignment markers from conventional overhead cameras. Yield-control teams desperately evaluate novel infrared-transparent imaging solutions to prevent catastrophic via-drilling misalignment during deep substrate backend processing.

Why do thermal drift considerations complicate lithography overlay?

Intense ambient energy loads inside modern fabs microscopically expand silicon substrates during actual processing steps. Continuous alignment marker scanning feeds real-time correction coordinates back into exposure software, preventing catastrophic pattern registration failures before they permanently ruin active transistor channels.

What role does virtual metrology play in high-volume manufacturing?

Computational inference bridges physical gaps where hardware imaging cannot penetrate dense transistor geometries fast enough. Data scientists predict unmeasurable internal dimensions using surface-level optical scatterometry signatures, allowing fabs to maintain throughput without sacrificing ultimate yield confidence.

How do equipment vendors attempt to lock in fab customers?

Major suppliers fuse proprietary lithography baseline data directly with their optical inspection software platforms. Module owners quickly discover that integrating third-party measurement tools into these closed digital ecosystems destroys established defect-prediction accuracy, essentially forcing continuous single-vendor hardware upgrades.

What strategy do foundries use to resist single-vendor lock-in?

Procurement directors deliberately fund open-source data standard initiatives and intentionally split inspection fleets across multiple competing hardware providers. Maintaining overlapping optical and e-beam ecosystems ensures foundries retain critical commercial leverage during multi-year service contract negotiations.

Why do European fabs procure leading-edge scatterometry tools?

Automotive-grade silicon increasingly requires advanced driver-assistance system functionality, pushing specialty mixed-signal designs into sub-nanometer tolerance regimes. Facility directors must unexpectedly upgrade legacy analog inspection lines just to verify complex heterogeneous advanced packaging interconnects reliably.

What causes yield-ramp cycles to accelerate dramatically?

Successfully correlating sparse high-resolution electron baseline data with dense continuous optical scatterometry streams unlocks rapid defect root-cause analysis. Fabs crossing this specific algorithmic threshold routinely slash problem-identification timelines from multiple weeks down to mere operational hours.

Why do pilot-line installations dictate ultimate supplier success?

Early beta-tool placements inside dominant foundries generate critical machine-learning feedback loops necessary for hardware refinement. Suppliers failing to secure these specific evaluation slots permanently lose crucial opportunities to train their algorithms against actual leading-edge physical transistor geometry.

Table of Content

- Executive Summary

- Global Market Outlook

- Demand to side Trends

- Supply to side Trends

- Technology Roadmap Analysis

- Analysis and Recommendations

- Market Overview

- Market Coverage / Taxonomy

- Market Definition / Scope / Limitations

- Research Methodology

- Chapter Orientation

- Analytical Lens and Working Hypotheses

- Market Structure, Signals, and Trend Drivers

- Benchmarking and Cross-market Comparability

- Market Sizing, Forecasting, and Opportunity Mapping

- Research Design and Evidence Framework

- Desk Research Programme (Secondary Evidence)

- Company Annual and Sustainability Reports

- Peer-reviewed Journals and Academic Literature

- Corporate Websites, Product Literature, and Technical Notes

- Earnings Decks and Investor Briefings

- Statutory Filings and Regulatory Disclosures

- Technical White Papers and Standards Notes

- Trade Journals, Industry Magazines, and Analyst Briefs

- Conference Proceedings, Webinars, and Seminar Materials

- Government Statistics Portals and Public Data Releases

- Press Releases and Reputable Media Coverage

- Specialist Newsletters and Curated Briefings

- Sector Databases and Reference Repositories

- FMI Internal Proprietary Databases and Historical Market Datasets

- Subscription Datasets and Paid Sources

- Social Channels, Communities, and Digital Listening Inputs

- Additional Desk Sources

- Expert Input and Fieldwork (Primary Evidence)

- Primary Modes

- Qualitative Interviews and Expert Elicitation

- Quantitative Surveys and Structured Data Capture

- Blended Approach

- Why Primary Evidence is Used

- Field Techniques

- Interviews

- Surveys

- Focus Groups

- Observational and In-context Research

- Social and Community Interactions

- Stakeholder Universe Engaged

- C-suite Leaders

- Board Members

- Presidents and Vice Presidents

- R&D and Innovation Heads

- Technical Specialists

- Domain Subject-matter Experts

- Scientists

- Physicians and Other Healthcare Professionals

- Governance, Ethics, and Data Stewardship

- Research Ethics

- Data Integrity and Handling

- Primary Modes

- Tooling, Models, and Reference Databases

- Desk Research Programme (Secondary Evidence)

- Data Engineering and Model Build

- Data Acquisition and Ingestion

- Cleaning, Normalisation, and Verification

- Synthesis, Triangulation, and Analysis

- Quality Assurance and Audit Trail

- Market Background

- Market Dynamics

- Drivers

- Restraints

- Opportunity

- Trends

- Scenario Forecast

- Demand in Optimistic Scenario

- Demand in Likely Scenario

- Demand in Conservative Scenario

- Opportunity Map Analysis

- Product Life Cycle Analysis

- Supply Chain Analysis

- Investment Feasibility Matrix

- Value Chain Analysis

- PESTLE and Porter’s Analysis

- Regulatory Landscape

- Regional Parent Market Outlook

- Production and Consumption Statistics

- Import and Export Statistics

- Market Dynamics

- Global Market Analysis 2021 to 2025 and Forecast, 2026 to 2036

- Historical Market Size Value (USD Million) Analysis, 2021 to 2025

- Current and Future Market Size Value (USD Million) Projections, 2026 to 2036

- Y to o to Y Growth Trend Analysis

- Absolute $ Opportunity Analysis

- Global Market Pricing Analysis 2021 to 2025 and Forecast 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Technology Type

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Technology Type , 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Technology Type , 2026 to 2036

- Optical Critical Dimension / OCD Metrology

- CD-SEM / e-Beam Metrology

- Others

- Optical Critical Dimension / OCD Metrology

- Y to o to Y Growth Trend Analysis By Technology Type , 2021 to 2025

- Absolute $ Opportunity Analysis By Technology Type , 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Deployment Mode

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Deployment Mode, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Deployment Mode, 2026 to 2036

- Stand-Alone in-Line Metrology Tools

- Integrated Cluster-Linked Metrology

- Others

- Stand-Alone in-Line Metrology Tools

- Y to o to Y Growth Trend Analysis By Deployment Mode, 2021 to 2025

- Absolute $ Opportunity Analysis By Deployment Mode, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Fab Application

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Fab Application, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Fab Application, 2026 to 2036

- Lithography Module Control

- Etch Profile and Line-Shape Control

- Others

- Lithography Module Control

- Y to o to Y Growth Trend Analysis By Fab Application, 2021 to 2025

- Absolute $ Opportunity Analysis By Fab Application, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By End User

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By End User, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By End User, 2026 to 2036

- Pure-Play Foundries

- Integrated Device Manufacturers

- Others

- Pure-Play Foundries

- Y to o to Y Growth Trend Analysis By End User, 2021 to 2025

- Absolute $ Opportunity Analysis By End User, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Node Focus

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Node Focus, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Node Focus, 2026 to 2036

- 2nm and Equivalent GAA Ramps

- 3nm Family Production Optimization

- Others

- 2nm and Equivalent GAA Ramps

- Y to o to Y Growth Trend Analysis By Node Focus, 2021 to 2025

- Absolute $ Opportunity Analysis By Node Focus, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Region

- Introduction

- Historical Market Size Value (USD Million) Analysis By Region, 2021 to 2025

- Current Market Size Value (USD Million) Analysis and Forecast By Region, 2026 to 2036

- North America

- Latin America

- Western Europe

- Eastern Europe

- East Asia

- South Asia and Pacific

- Middle East & Africa

- Market Attractiveness Analysis By Region

- North America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- USA

- Canada

- Mexico

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Key Takeaways

- Latin America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Brazil

- Chile

- Rest of Latin America

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Key Takeaways

- Western Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Germany

- UK

- Italy

- Spain

- France

- Nordic

- BENELUX

- Rest of Western Europe

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Key Takeaways

- Eastern Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Russia

- Poland

- Hungary

- Balkan & Baltic

- Rest of Eastern Europe

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Key Takeaways

- East Asia Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- China

- Japan

- South Korea

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Key Takeaways

- South Asia and Pacific Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- India

- ASEAN

- Australia & New Zealand

- Rest of South Asia and Pacific

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Key Takeaways

- Middle East & Africa Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkiye

- South Africa

- Other African Union

- Rest of Middle East & Africa

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- By Country

- Market Attractiveness Analysis

- By Country

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Key Takeaways

- Key Countries Market Analysis

- USA

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Canada

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Mexico

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Brazil

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Chile

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Germany

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- UK

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Italy

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Spain

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- France

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- India

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- ASEAN

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Australia & New Zealand

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- China

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Japan

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- South Korea

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Russia

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Poland

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Hungary

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Kingdom of Saudi Arabia

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Turkiye

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- South Africa

- Pricing Analysis

- Market Share Analysis, 2025

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- USA

- Market Structure Analysis

- Competition Dashboard

- Competition Benchmarking

- Market Share Analysis of Top Players

- By Regional

- By Technology Type

- By Deployment Mode

- By Fab Application

- By End User

- By Node Focus

- Competition Analysis

- Competition Deep Dive

- KLA Corporation

- Overview

- Product Portfolio

- Profitability by Market Segments (Product/Age /Sales Channel/Region)

- Sales Footprint

- Strategy Overview

- Marketing Strategy

- Product Strategy

- Channel Strategy

- ASML Holding N.V.

- Nova Ltd.

- Onto Innovation Inc.

- Applied Materials, Inc.

- Hitachi High-Tech Corporation

- KLA Corporation

- Competition Deep Dive

- Assumptions & Acronyms Used

List of Tables

- Table 1: Global Market Value (USD Million) Forecast by Region, 2021 to 2036

- Table 2: Global Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 3: Global Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 4: Global Market Value (USD Million) Forecast by Fab Application, 2021 to 2036

- Table 5: Global Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 6: Global Market Value (USD Million) Forecast by Node Focus, 2021 to 2036

- Table 7: North America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 8: North America Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 9: North America Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 10: North America Market Value (USD Million) Forecast by Fab Application, 2021 to 2036

- Table 11: North America Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 12: North America Market Value (USD Million) Forecast by Node Focus, 2021 to 2036

- Table 13: Latin America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 14: Latin America Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 15: Latin America Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 16: Latin America Market Value (USD Million) Forecast by Fab Application, 2021 to 2036

- Table 17: Latin America Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 18: Latin America Market Value (USD Million) Forecast by Node Focus, 2021 to 2036

- Table 19: Western Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 20: Western Europe Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 21: Western Europe Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 22: Western Europe Market Value (USD Million) Forecast by Fab Application, 2021 to 2036

- Table 23: Western Europe Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 24: Western Europe Market Value (USD Million) Forecast by Node Focus, 2021 to 2036

- Table 25: Eastern Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 26: Eastern Europe Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 27: Eastern Europe Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 28: Eastern Europe Market Value (USD Million) Forecast by Fab Application, 2021 to 2036

- Table 29: Eastern Europe Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 30: Eastern Europe Market Value (USD Million) Forecast by Node Focus, 2021 to 2036

- Table 31: East Asia Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 32: East Asia Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 33: East Asia Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 34: East Asia Market Value (USD Million) Forecast by Fab Application, 2021 to 2036

- Table 35: East Asia Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 36: East Asia Market Value (USD Million) Forecast by Node Focus, 2021 to 2036

- Table 37: South Asia and Pacific Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 38: South Asia and Pacific Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 39: South Asia and Pacific Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 40: South Asia and Pacific Market Value (USD Million) Forecast by Fab Application, 2021 to 2036

- Table 41: South Asia and Pacific Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 42: South Asia and Pacific Market Value (USD Million) Forecast by Node Focus, 2021 to 2036

- Table 43: Middle East & Africa Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 44: Middle East & Africa Market Value (USD Million) Forecast by Technology Type , 2021 to 2036

- Table 45: Middle East & Africa Market Value (USD Million) Forecast by Deployment Mode, 2021 to 2036

- Table 46: Middle East & Africa Market Value (USD Million) Forecast by Fab Application, 2021 to 2036

- Table 47: Middle East & Africa Market Value (USD Million) Forecast by End User, 2021 to 2036

- Table 48: Middle East & Africa Market Value (USD Million) Forecast by Node Focus, 2021 to 2036

List of Figures

- Figure 1: Global Market Pricing Analysis

- Figure 2: Global Market Value (USD Million) Forecast 2021-2036

- Figure 3: Global Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 4: Global Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 5: Global Market Attractiveness Analysis by Technology Type

- Figure 6: Global Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 7: Global Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 8: Global Market Attractiveness Analysis by Deployment Mode

- Figure 9: Global Market Value Share and BPS Analysis by Fab Application, 2026 and 2036

- Figure 10: Global Market Y-o-Y Growth Comparison by Fab Application, 2026-2036

- Figure 11: Global Market Attractiveness Analysis by Fab Application

- Figure 12: Global Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 13: Global Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 14: Global Market Attractiveness Analysis by End User

- Figure 15: Global Market Value Share and BPS Analysis by Node Focus, 2026 and 2036

- Figure 16: Global Market Y-o-Y Growth Comparison by Node Focus, 2026-2036

- Figure 17: Global Market Attractiveness Analysis by Node Focus

- Figure 18: Global Market Value (USD Million) Share and BPS Analysis by Region, 2026 and 2036

- Figure 19: Global Market Y-o-Y Growth Comparison by Region, 2026-2036

- Figure 20: Global Market Attractiveness Analysis by Region

- Figure 21: North America Market Incremental Dollar Opportunity, 2026-2036

- Figure 22: Latin America Market Incremental Dollar Opportunity, 2026-2036

- Figure 23: Western Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 24: Eastern Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 25: East Asia Market Incremental Dollar Opportunity, 2026-2036

- Figure 26: South Asia and Pacific Market Incremental Dollar Opportunity, 2026-2036

- Figure 27: Middle East & Africa Market Incremental Dollar Opportunity, 2026-2036

- Figure 28: North America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 29: North America Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 30: North America Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 31: North America Market Attractiveness Analysis by Technology Type

- Figure 32: North America Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 33: North America Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 34: North America Market Attractiveness Analysis by Deployment Mode

- Figure 35: North America Market Value Share and BPS Analysis by Fab Application, 2026 and 2036

- Figure 36: North America Market Y-o-Y Growth Comparison by Fab Application, 2026-2036

- Figure 37: North America Market Attractiveness Analysis by Fab Application

- Figure 38: North America Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 39: North America Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 40: North America Market Attractiveness Analysis by End User

- Figure 41: North America Market Value Share and BPS Analysis by Node Focus, 2026 and 2036

- Figure 42: North America Market Y-o-Y Growth Comparison by Node Focus, 2026-2036

- Figure 43: North America Market Attractiveness Analysis by Node Focus

- Figure 44: Latin America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 45: Latin America Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 46: Latin America Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 47: Latin America Market Attractiveness Analysis by Technology Type

- Figure 48: Latin America Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 49: Latin America Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 50: Latin America Market Attractiveness Analysis by Deployment Mode

- Figure 51: Latin America Market Value Share and BPS Analysis by Fab Application, 2026 and 2036

- Figure 52: Latin America Market Y-o-Y Growth Comparison by Fab Application, 2026-2036

- Figure 53: Latin America Market Attractiveness Analysis by Fab Application

- Figure 54: Latin America Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 55: Latin America Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 56: Latin America Market Attractiveness Analysis by End User

- Figure 57: Latin America Market Value Share and BPS Analysis by Node Focus, 2026 and 2036

- Figure 58: Latin America Market Y-o-Y Growth Comparison by Node Focus, 2026-2036

- Figure 59: Latin America Market Attractiveness Analysis by Node Focus

- Figure 60: Western Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 61: Western Europe Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 62: Western Europe Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 63: Western Europe Market Attractiveness Analysis by Technology Type

- Figure 64: Western Europe Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 65: Western Europe Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 66: Western Europe Market Attractiveness Analysis by Deployment Mode

- Figure 67: Western Europe Market Value Share and BPS Analysis by Fab Application, 2026 and 2036

- Figure 68: Western Europe Market Y-o-Y Growth Comparison by Fab Application, 2026-2036

- Figure 69: Western Europe Market Attractiveness Analysis by Fab Application

- Figure 70: Western Europe Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 71: Western Europe Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 72: Western Europe Market Attractiveness Analysis by End User

- Figure 73: Western Europe Market Value Share and BPS Analysis by Node Focus, 2026 and 2036

- Figure 74: Western Europe Market Y-o-Y Growth Comparison by Node Focus, 2026-2036

- Figure 75: Western Europe Market Attractiveness Analysis by Node Focus

- Figure 76: Eastern Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 77: Eastern Europe Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 78: Eastern Europe Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 79: Eastern Europe Market Attractiveness Analysis by Technology Type

- Figure 80: Eastern Europe Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 81: Eastern Europe Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 82: Eastern Europe Market Attractiveness Analysis by Deployment Mode

- Figure 83: Eastern Europe Market Value Share and BPS Analysis by Fab Application, 2026 and 2036

- Figure 84: Eastern Europe Market Y-o-Y Growth Comparison by Fab Application, 2026-2036

- Figure 85: Eastern Europe Market Attractiveness Analysis by Fab Application

- Figure 86: Eastern Europe Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 87: Eastern Europe Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 88: Eastern Europe Market Attractiveness Analysis by End User

- Figure 89: Eastern Europe Market Value Share and BPS Analysis by Node Focus, 2026 and 2036

- Figure 90: Eastern Europe Market Y-o-Y Growth Comparison by Node Focus, 2026-2036

- Figure 91: Eastern Europe Market Attractiveness Analysis by Node Focus

- Figure 92: East Asia Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 93: East Asia Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 94: East Asia Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 95: East Asia Market Attractiveness Analysis by Technology Type

- Figure 96: East Asia Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 97: East Asia Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036

- Figure 98: East Asia Market Attractiveness Analysis by Deployment Mode

- Figure 99: East Asia Market Value Share and BPS Analysis by Fab Application, 2026 and 2036

- Figure 100: East Asia Market Y-o-Y Growth Comparison by Fab Application, 2026-2036

- Figure 101: East Asia Market Attractiveness Analysis by Fab Application

- Figure 102: East Asia Market Value Share and BPS Analysis by End User, 2026 and 2036

- Figure 103: East Asia Market Y-o-Y Growth Comparison by End User, 2026-2036

- Figure 104: East Asia Market Attractiveness Analysis by End User

- Figure 105: East Asia Market Value Share and BPS Analysis by Node Focus, 2026 and 2036

- Figure 106: East Asia Market Y-o-Y Growth Comparison by Node Focus, 2026-2036

- Figure 107: East Asia Market Attractiveness Analysis by Node Focus

- Figure 108: South Asia and Pacific Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 109: South Asia and Pacific Market Value Share and BPS Analysis by Technology Type , 2026 and 2036

- Figure 110: South Asia and Pacific Market Y-o-Y Growth Comparison by Technology Type , 2026-2036

- Figure 111: South Asia and Pacific Market Attractiveness Analysis by Technology Type

- Figure 112: South Asia and Pacific Market Value Share and BPS Analysis by Deployment Mode, 2026 and 2036

- Figure 113: South Asia and Pacific Market Y-o-Y Growth Comparison by Deployment Mode, 2026-2036