Advanced Probe Card and Wafer Probing Test Systems Market

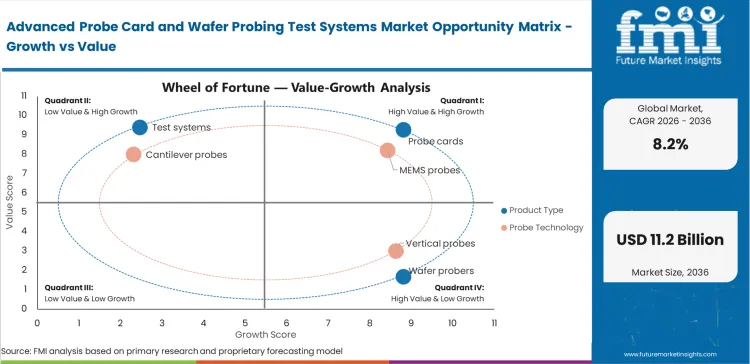

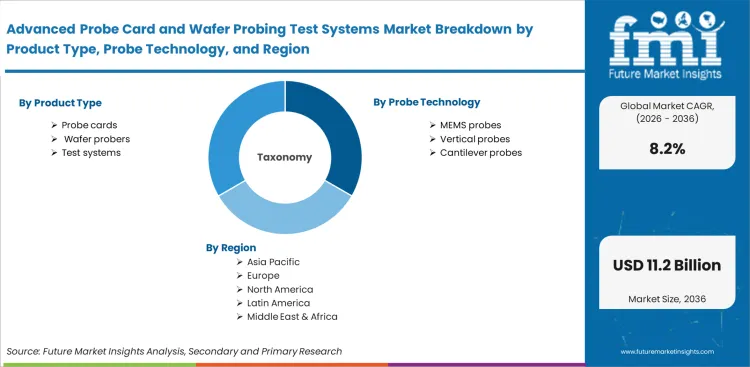

The advanced probe card and wafer probing test systems market is segmented by Product Type (Probe cards, Wafer probers, Test systems), Probe Technology (MEMS probes, Vertical probes, Cantilever probes), Application (Logic ICs, Memory ICs, Analog ICs), End User (Foundries, IDMs, OSATs), Wafer Size (300mm wafers, 200mm wafers, Others), and Region. Forecast for 2026 to 2036.

Historical Data Covered: 2016 to 2024 | Base Year: 2025 | Estimated Year: 2026 | Forecast Period: 2027 to 2036

Advanced Probe Card and Wafer Probing Test Systems Market Size, Market Forecast and Outlook By FMI

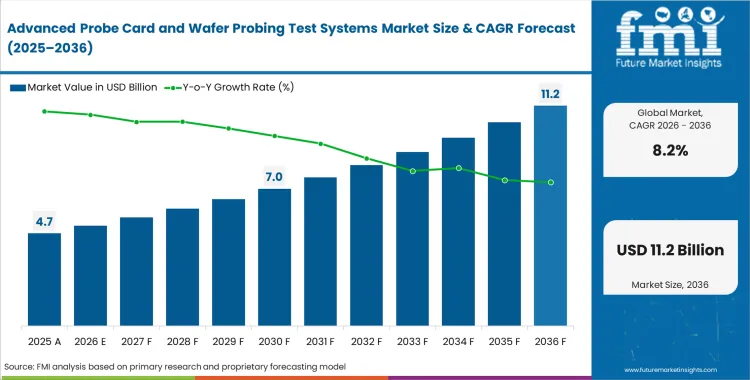

The advanced probe card and wafer probing test systems market was valued at USD 4.3 billion in 2025. Valuation is expected to cross USD 4.7 billion in 2026 at a CAGR of 8.2% during the forecast period. The cumulative revenue is expected to be USD 10.4 billion through 2036 as advanced node chiplet architectures require exponentially higher test insertion rates per die across the advanced probe card and wafer probing test systems market

Foundries and OSATs are under significant business pressure to ensure known good die prior to advanced packaging assembly. Any delay in upgrading massive parallel testing capabilities can result in significant yield loss in heterogeneous integration. Offering wafer testing services at the outset of the process flow can help prevent packaging defective dies. This cost scales non-linearly at 5nm nodes.

Summary of Advanced Probe Card and Wafer Probing Test Systems Market

- Advanced Probe Card and Wafer Probing Test Systems Market Definition

- Precision electro-mechanical interfaces and systems used to validate semiconductor die functionality directly on the silicon before dicing.

- Demand Drivers in the Market

- Yield protection pressure forces foundry operations managers to implement massive parallel testing.

- Advanced packaging complexity requires OSAT test engineers to validate known good die rigorously.

- Automotive safety standards push analog IC manufacturers to perform extreme temperature probing.

- Key Segments Analyzed in the FMI Report

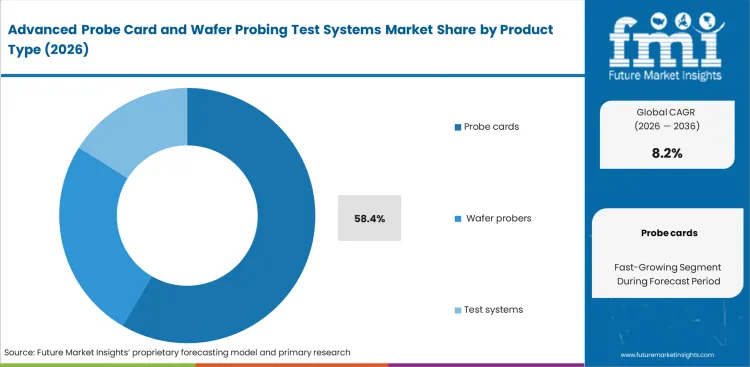

- Probe cards: This segment is expected to hold 58.4% share in 2026, benefiting from consumable replacement cycles tied to wafer volumes.

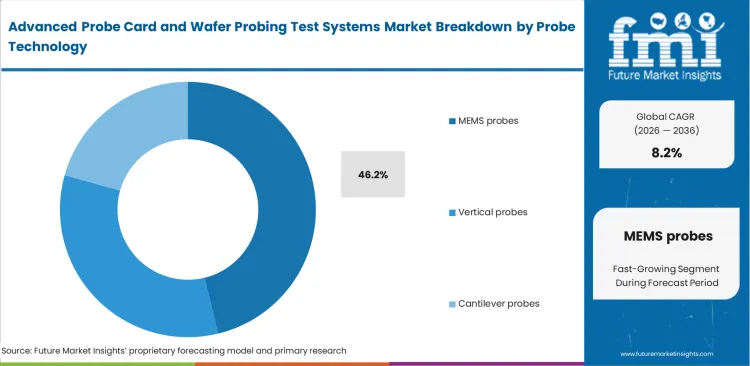

- MEMS probes: This segment is anticipated to record 46.2% share in 2026, scaling efficiently to deliver MEMS probe cards benefits at fine pitches.

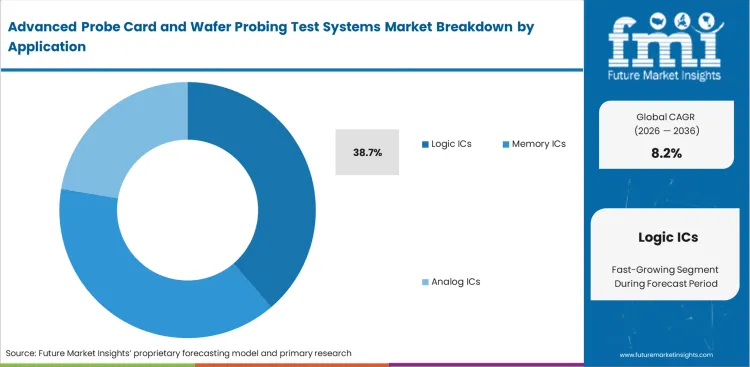

- Logic ICs: This segment is projected to garner 38.7% share in 2026, driven by high pin counts required for AI chip testing solutions.

- Foundries: This segment is set to account for 44.5% share in 2026, controlling the largest share of global wafer starts.

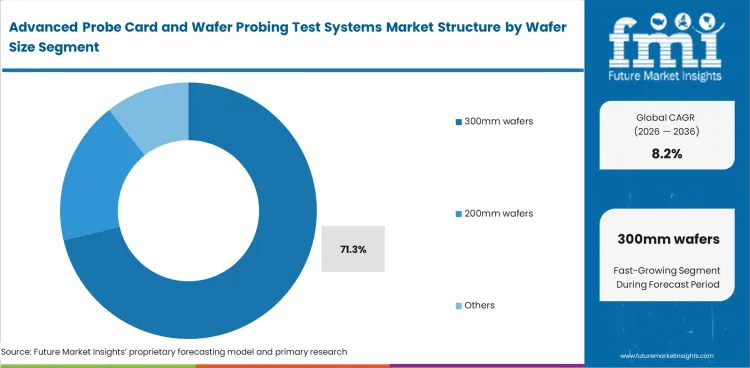

- 300mm wafers: This segment is estimated to grab 71.3% share in 2026, dominating advanced node production.

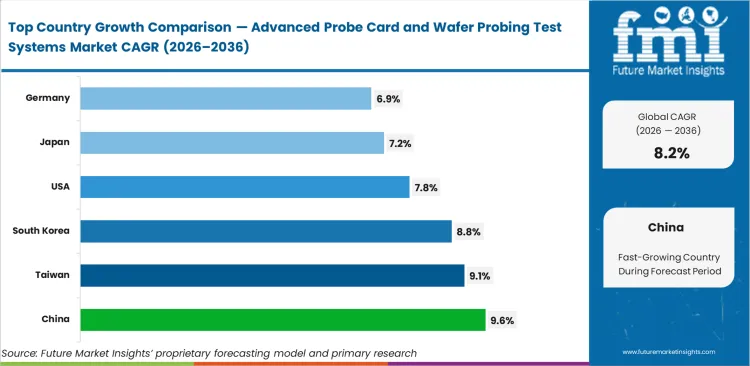

- China: The country records 9.6% compound growth, supported by localized supply chain development bypassing export restrictions.

- Analyst Opinion at FMI

- Rahul Pandita, Principal Analyst, Technology, at FMI, notes that, "Generalist models assume testing capital expenditure scales linearly with silicon volume. Operations directors at leading foundries realize the true constraint lies in thermal dissipation during full-wafer contact. Inserting a probe card onto a 3nm logic wafer generates massive localized heat distorting test signals. Tooling engineers treat active thermal management within the prober as the actual differentiator, rendering pin-count metrics secondary."

- Strategic Implications / Executive Takeaways

- Test equipment procurement directors face vendor lock-in due to proprietary prober-to-tester interfaces.

- Foundry operations managers must align equipment lead times with new node tape-outs.

- OSAT facility directors risk margin compression post consumable probe life cycles falling below expected touch-down targets.

- Methodology

- Primary Research: Primary interviews with test cell architects validate technology transition timing.

- Desk Research: SEMI equipment shipment logs provide a hard floor for installed base calculations.

- Market-Sizing and Forecasting: Wafer start capacity expansions offer a reliable leading indicator for future consumable demand.

- Data Validation and Update Cycle: Financial filings from pure-play probe card vendors triangulate bottom-up models.

Advanced Probe Card and Wafer Probing Test Systems Market Key Takeaways

| Metric | Details |

|---|---|

| Industry Size (2026) | USD 4.7 Billion |

| Industry Value (2036) | USD 10.4 Billion |

| CAGR (2026 to 2036) | 8.2% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

As test cell output equals advanced lithography output, testing moves from a bottleneck to a yield enhancer. Foundries enable this by selecting single-touch probing architectures capable of overcoming chiplet testing challenges. Operations managers then deploy these in high-volume production to stabilize module assembly using modern wafer test automation systems.

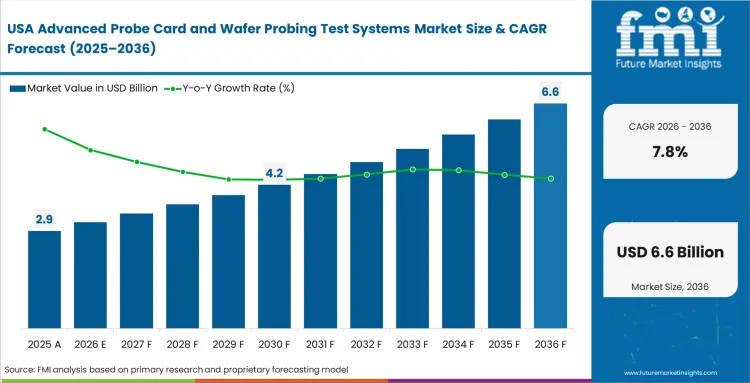

Global market along distinct regional trajectories, shaped by foundry strategies, government incentives, and technology specialization. China tracks at 9.6% CAGR, supported by domestic foundries localizing supply chains aggressively. Taiwan follows closely at 9.1% CAGR, driven by dominant outsourced semiconductor assembly operations. South Korea expands at 8.8% CAGR due to memory IC testing demands. The United States maintains a 7.8% CAGR supported by CHIPS Act incentives focusing on onshore logic production. Japan advances at 7.2% CAGR relying on its strong test equipment manufacturing base. Germany grows at 6.9% CAGR as European facilities focus primarily on automotive analog testing requirements, creating a split compared to Asian hubs prioritizing logic IC testing solutions.

Advanced Probe Card and Wafer Probing Test Systems Market Definition

Precision electro-mechanical interfaces validating semiconductor die functionality before dicing define this sector. Understanding semiconductor yield testing systems requires analyzing setups measuring electrical signals between test equipment and microscopic contact pads on silicon. Testing ensures only functional integrated circuits proceed to final packaging, preventing costly downstream failures and improving overall efficiency.

Advanced Probe Card and Wafer Probing Test Systems Market Inclusions

Scope covers probe cards, wafer probers, and integrated test systems. Equipment designed for 150mm probe station setups through 300mm platforms falls within this boundary. Analytics software directly managing wafer test process steps and associated consumable contact technologies are also evaluated.

Advanced Probe Card and Wafer Probing Test Systems Market Exclusions

Final package test equipment stands outside this boundary because it evaluates sealed chips rather than bare wafers. Optical inspection tools lacking electrical contact capabilities remain excluded. Standalone failure analysis microscopes used outside high-volume production floors are omitted from the valuation.

Advanced Probe Card and Wafer Probing Test Systems Market Research Methodology

- Primary Research: Procurement directors at Tier-1 foundries and operations managers evaluating the advanced probe card market supply base

- Desk Research: SEC filings from test equipment vendors and SEMI equipment shipment registries

- Market-Sizing and Forecasting: Annual wafer start volumes cross-referenced with test insertion frequency across the advanced semiconductor testing market

- Data Validation and Update Cycle: Capital expenditure reports from top-three semiconductor fabricators

Segmental Analysis

Advanced Probe Card and Wafer Probing Test Systems Market Analysis by Product Type

Replacement cycles of consumables describe the economic engine behind the testing environment in semiconductors. The probe cards hold 58.4% in 2026, mainly because of the high-intensity foundries, which rely on these interfaces to perform massive parallel touch-downs. Based on the analysis by FMI, tool managers replace these electro-mechanical interfaces after a definite number of touch-downs to avoid pad damage. Test facilities with mems probes have tighter pitch resolutions, but they have to cope with fluctuating probe card prices. The purchasing department in most facilities does not consider catastrophic localized fab contamination scenarios, which cause premature replacement of the probe cards, destroying consumables budgets instantly. Test engineers not optimizing the cleaning recipes result in serious reliability issues with probe cards, causing abrupt changes in yield.

- Initial selection criteria: Procurement directors choose specific card architectures based on pad pitch density requirements. Custom designs take weeks to manufacture.

- Qualification validation: Test floor engineers run hundreds of dummy wafers to verify contact resistance stability. Signal integrity must remain flawless across temperature ranges.

- Renewal mechanisms: Operations managers reorder duplicate cards automatically prior to touch-down counters approaching specified limits. Maintaining safety stock prevents catastrophic line stoppages.

Advanced Probe Card and Wafer Probing Test Systems Market Analysis by Probe Technology

Miniaturization demands that the logic designers achieve pad pitch dimensions that are impossible for conventional cantilever wires to achieve. The MEMS segment holds 46.2% revenue share in 2026, backed by the photolithography manufacturing process that enables suppliers to provide identical arrays of dense contacts that match the current probe card technology trends. Operations directors of the most prominent IDMs utilize these advanced arrays for critical microprocessor validation. According to FMI analysts, although the architectures of these fine pitches excel in performance, they are challenged during power testing that requires thicker vertical pins. Choosing wrong probe metallurgy for certain automotive analog tests causes melted contacts.

- Procurement savings: Volume pricing agreements reduce unit costs for highly standardized MEMS arrays. Consolidating orders improves overall test floor economics.

- Operational hidden costs: Tooling specialists spend significant labor hours aligning complex probe heads to advanced automated test equipment platforms. Maintenance requires specialized training.

- Lifecycle analysis: Financial controllers calculate true ownership costs by dividing capital outlay by total successful touch-downs. Durability often trumps initial purchase price.

Advanced Probe Card and Wafer Probing Test Systems Market Analysis by Application

Sophisticated artificial intelligence accelerators demand validation of thousands of signals at a time. Analysis by FMI shows that high-speed digital interfaces require pristine signal paths from tester to silicon. A study of integrated photonics test reliability systems, compared with traditional logic probing, reveals a bottleneck emerging in co-packaged optics validation. Logic ICs segment account for a commanding share of 38.7% in 2026, driven by test cell architects designing massive systems for these extreme pin counts. Test managers who do not account for thermal expansion during high-power logic testing shatter delicate silicon pads.

- Prevention focus: Rigorous logic testing prevents packaging defective components into expensive multi-chip modules. Escaping defects destroy downstream profitability.

- Residual risk: Comprehensive probing misses certain at-speed functional failures occasionally. Burn-in testing remains necessary for high-reliability automotive components.

- Full capture: Yield engineers must correlate probing data with final package test results to close the feedback loop. Isolated data limits continuous improvement efforts.

Advanced Probe Card and Wafer Probing Test Systems Market Analysis by End User

Contract manufacturers, or 'foundries,' are in charge of processing most of the world's silicon production for various clients. Unlike Integrated Device Manufacturers (IDMs), whose focus is on optimizing test cell configurations to suit their product portfolio, contract manufacturers have to invest in costly semiconductor metrology and inspection infrastructures to support varied production volumes. Foundries are expected to command a 44.5% market share in 2026, attributed to the high rate at which test cell configurations are being changed by floor managers to accommodate the varied needs of their fabless clients. These facilities, according to estimates by FMI, have the potential to achieve high utilization rates on their equipment by standardizing probing platforms while incorporating total foundry wafer testing solutions. The problem, however, is the fact that any delay in configuring the test cell may result in wafer staging issues.

- Pioneering adopters: Tier-1 foundries qualify new probing architectures first to support advanced lithography nodes. Their volume guarantees drive supplier roadmaps.

- Fast followers: Leading OSATs adopt proven setups to expand their wafer-level packaging capabilities. Standardized tools reduce their integration risks.

- Late converters: Legacy IDMs upgrade systems exclusively during existing equipment failing to support new product introductions. Capital constraints dictate their slower transition speeds.

Advanced Probe Card and Wafer Probing Test Systems Market Analysis by Wafer Size

Advanced node manufacturing is done only on maximum diameter substrates to achieve optimal edge loss economics. The 300mm wafers segment holds 71.3% revenue share in 2026, as capital equipment buyers are purchasing new mega-fabs exclusively with this support. According to FMI, extreme parallelism needs massive force to be applied to touch thousands of dies at once across the entire 300mm surface. Spec sheets on equipment do not reveal that mechanical deflection of the prober chuck occurs under extreme multi-ton forces, resulting in edge die contact failures. Operations managers who do not calibrate planarization under load will have systematic edge yield losses.

- Extreme edge conditions: Probing the outermost dies requires perfect thermal stability across the entire chuck. Small temperature gradients cause catastrophic misalignment.

- Acceptability standards: Quality directors enforce strict contact resistance variance limits across the wafer map. Failed contacts require immediate tool recalibration.

- Performance highlights: Advanced systems maintain sub-micron accuracy over extended testing campaigns. This precision maximizes overall equipment effectiveness.

Advanced Probe Card and Wafer Probing Test Systems Market Drivers, Restraints, and Opportunities

The shift toward advanced packaging requires Outsourced Semiconductor Assembly and Test (OSAT) firms to flawlessly validate bare dies before integration onto expensive multi-chip substrates. Integrating a single faulty chiplet nullifies the entire assembly, resulting in hundreds of dollars in immediate material loss. Therefore, when utilizing semiconductor assembly and testing service, absolute confidence in "known-good-die" (KGD) metrics is crucial. Test cell managers cannot tolerate false positives or escaped defects.

Consequently, moving testing operations upstream to the wafer probing stage is a financial necessity, not merely a technical choice. Foundries that bypass comprehensive full-wafer burn-in risk significant margin penalties due to downstream customer rejections of the final modules.

A major obstacle in full-wafer parallel testing is the mechanical planarization required under extreme pressure. Contacting thousands of microscopic pads simultaneously demands hundreds of kilograms of localized force. Maintaining the prober chuck's perfect flatness under this load is a continuous challenge for tooling engineers. Any resulting chuck deflection leads to uneven contact resistance, which causes spurious failures on dies at the wafer's edge. Currently, mechanisms designed to compensate for this stiffness add substantial weight to the thermal control units, thereby reducing the speed at which the system can step between different test zones.

Opportunities in the Advanced Probe Card and Wafer Probing Test Systems Market

- Active thermal chucks: The integration of liquid cooling into the probing chuck enables the logic test engineers of AI chips to dissipate massive heat during chip validation.

- Co-packaged optics testing: The integration of specialized heterogeneous integration and advanced packaging X-ray CT inspection systems into wafer probing enables OSATs to test photonic interconnects. This gives them a chance to win lucrative hyperscaler contracts.

- Predictive maintenance analytics: The analysis of changes in contact resistance allows the operations manager of a wafer probing facility to schedule the cleaning of the probe cards. This extends the life of the consumables significantly.

Regional Analysis

Based on regional analysis, the advanced probe card and wafer probing test systems market is segmented into North America, Europe, Asia Pacific, Latin America, and Middle East & Africa.

.webp)

| Country | CAGR (2026 to 2036) |

|---|---|

| China | 9.6% |

| Taiwan | 9.1% |

| South Korea | 8.8% |

| United States | 7.8% |

| Japan | 7.2% |

| Germany | 6.9% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Asia Pacific Advanced Probe Card and Wafer Probing Test Systems Market Analysis

The massive expansion of foundry capacity drives aggressive equipment procurements within this region. The local governments are heavily subsidizing the development of local supply chains to reduce dependency on imported testing technologies. FMI finds that pure-play foundries are driving the technical roadmaps for regional test equipment suppliers. Tool suppliers need to match next-generation 3D IC and 2.5D IC packaging probing technologies to specific regional tape-outs.

- China: Procurement groups are increasingly targeting local sources that have the capability to achieve tier 1 performance standards, thereby providing competitive reliability without relying on external sources. The pace at which local foundries are supporting the localization of consumable probe cards is fueling the market growth in China at 9.6% CAGR. This is underpinned by initiatives to boost regional supply chain robustness, thereby evading export control limitations on advanced testing technologies.

- Taiwan: Taiwan's dominant contract manufacturers are driving extreme parallel testing requirements to move massive 300mm wafer backlogs, which is driving market revenue at a CAGR of 9.1% during the forecast period. The industry is benefiting from the move to high-throughput test systems, which offer substantial operational benefits. Test cell architects driving the selection of these advanced testing platforms are benefiting from the efficiency improvements, which have a direct impact on scalability and competitiveness..

- South Korea: The market in South Korea requires specialized probing architectures that can withstand extreme temperature cycling during DRAM validation, which is causing the market to register a CAGR of 8.8% during the forecast period. This is because those plants that are capable of reliable hot and cold temperature testing cycles greatly increase their overall output, further emphasizing South Korea's position in memory chip testing innovation.

- Japan: Well-established test equipment companies leverage their precision engineering expertise to control the global prober system export market, sustaining a 7.2% CAGR driven by improvements in mechanical stepping accuracy. Their engineers continue to define absolute mechanical limits.

North America Advanced Probe Card and Wafer Probing Test Systems Market Analysis

The Federal Incentive Programs (FIPs) direct investments to onshore logic production facilities. The top designers of microprocessors need high-performance test cells to validate designs that can dissipate large powers. In this case, facility managers focus on complex advanced packaging designs rather than high-volume memory configurations. Delaying investment in extreme pitch capability locks fabs out of next-generation AI accelerator procurements.

- United States: Government subsidies under the CHIPS Act direct IDMs to build new fabs for advanced nodes with thousands of new probe interfaces, growing at a CAGR of 7.8% driven by onshore logic production mandates. Procurement directors who secure early allocation slots in these fabs are actively negotiating directly with the top suppliers of probe cards.

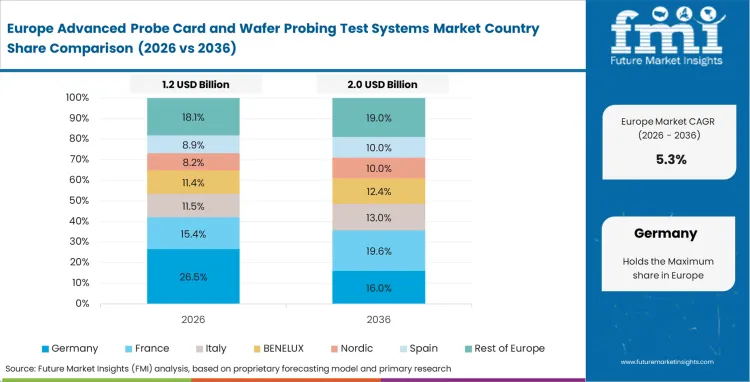

Europe Advanced Probe Card and Wafer Probing Test Systems Market Analysis

Automotive quality standards define the testing parameters to be followed in regional silicon development. Power and analog IC manufacturers require extreme voltage and temperature probing to ensure zero-defect components. From the perspective of FMI, European test cell managers prioritize system reliability and data tracing over speed. Adhering to stringent wafer-level packaging validation ensures catastrophic failure is prevented in mission-critical vehicle systems.

- Germany: Tier 1 automotive manufacturers are driving functional safety standards in regional foundries, demanding robust reliability in high-voltage wafer testing. The market is expected to grow at a CAGR of 6.9%, with the foundation being set for long-term supply contracts to guarantee future continuity and compliance. Foundry suppliers with the capability to deliver probe cell offerings in extreme thermal and electrical environments are securing lucrative contracts, securing their place in the supply chain for the automotive industry. The focus on reliability, precision, and safety highlights Germany’s influence in the development of next-generation testing solutions in the country.

Competitive Aligners for Market Players

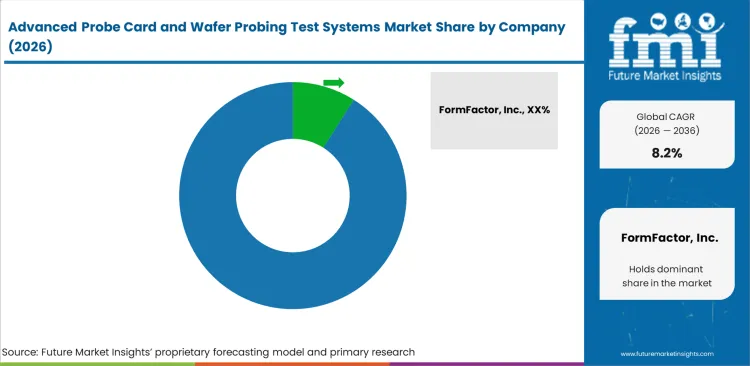

Consolidation defines the probe card tier, yet the heavy equipment prober segment remains moderately concentrated among established mechanical engineering firms. FormFactor and Technoprobe dominate the high-end MEMS interface space. Procurement directors evaluating the best probe card companies focus strictly on pitch-reduction roadmaps and thermal dissipation limits. Choosing a vendor without a proven fan out wafer level packaging test capability leaves advanced OSATs unable to support complex customer designs. Tooling engineers disregard marketing claims about pin density, demanding raw qualification data from actual 3nm tape-outs.

Incumbents possess massive libraries of validated contact metallurgies optimized for specific pad materials. Challengers cannot replicate this proprietary materials science overnight during probe card vs test sockets utility evaluations across high-volume lines. Advantest and Tokyo Electron maintain deep integration with major automated test equipment platforms, ensuring direct software handshakes between prober and tester. Facility managers resist introducing unproven semiconductor ic packaging materials testing systems threatening to disrupt this established software ecosystem. Breaking into a tier-1 foundry requires providing evaluation tools free of charge for months of rigorous parallel testing.

Leading foundries fight vendor lock-in by enforcing strict dual-sourcing policies for all consumable probe cards. Operations directors refuse to qualify any specific contact architecture assigned exclusively to one of the major wafer probing equipment suppliers possessing the sole manufacturing rights. Approaching 2036, hardware standardizations around optical probing interfaces force traditional pin-manufacturers to acquire photonics testing startups. Firms failing to offer unified electrical and optical probing heads lose their positions at high-performance hyperscaler fabs.

Key Players in Advanced Probe Card and Wafer Probing Test Systems Market

- FormFactor, Inc.

- Technoprobe S.p.A.

- Advantest Corporation

- Tokyo Electron Limited

- MPI Corporation

- Micronics Japan Co., Ltd.

- SV Probe Pte. Ltd.

Scope of the Report

| Metric | Value |

|---|---|

| Quantitative Units | USD 4.7 Billion to USD 10.4 Billion, at a CAGR of 8.2% |

| Market Definition | Precision electro-mechanical interfaces and systems used to validate semiconductor die functionality directly on the silicon before dicing. |

| Segmentation | Product Type, Probe Technology, Application, End User, Wafer Size, Region |

| Regions Covered | North America, Europe, Asia Pacific, Latin America, Middle East & Africa |

| Countries Covered | United States, Canada, Germany, United Kingdom, France, Italy, Spain, China, Japan, South Korea, Taiwan, Singapore, Brazil, Mexico, Argentina, GCC Countries, South Africa, Israel, Rest of Middle East & Africa |

| Key Companies Profiled | FormFactor, Technoprobe, Advantest, Tokyo Electron, MPI, Micronics Japan, SV Probe |

| Forecast Period | 2026 to 2036 |

| Approach | Bottom-up revenue triangulation anchored on equipment shipments |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Advanced Probe Card and Wafer Probing Test Systems Market Analysis by Segments

Product Type

- Probe cards

- Wafer probers

- Test systems

Probe Technology

- MEMS probes

- Vertical probes

- Cantilever probes

Application

- Logic ICs

- Memory ICs

- Analog ICs

End User

- Foundries

- IDMs

- OSATs

Wafer Size

- 300mm wafers

- 200mm wafers

- Others

Region

- North America

- United States

- Canada

- Europe

- Germany

- United Kingdom

- France

- Italy

- Spain

- Asia Pacific

- China

- Japan

- South Korea

- Taiwan

- Singapore

- Latin America

- Brazil

- Mexico

- Argentina

- Middle East & Africa

- GCC Countries

- South Africa

- Israel

- Rest of Middle East & Africa

Bibliography

- Chien, C. F., & Suwattananuruk, W. (2025, May). Semiconductor probe card proactive maintenance using graph self-supervised learning and an empirical study. Reliability Engineering & System Safety.

- MPI Corporation. (2024, August). Sustainability report 2024: Wafer probe card technologies and applications.

- Seica S.p.A. (2024). Probe card: The core of wafer testing.

- Seica S.p.A. (2025, November). The probe card: The core of wafer testing (updated edition).

- Wang, W., & Mian, R. (2025, June). Optimizing FPGA and wafer test coverage with spatial sampling and machine learning.

This bibliography is provided for reader reference. The full FMI report contains the complete reference list with primary source documentation.

This Report Addresses

- Pad pitch density limitations faced by tool managers operating advanced probe cards.

- Yield degradation risks managed by test engineers during logic IC evaluations.

- Thermal dissipation bottlenecks constraining parallel testing on 300mm prober chucks.

- Subsidized supply chain localization impacting OSAT procurement directors across China.

- Cleanroom tool integration challenges handled by IDM operations directors modifying ATE platforms.

- Consumable replacement cycles determining true ownership costs for procurement controllers.

- Voltage validation parameters enforced by automotive analog manufacturers ensuring zero-defect compliance.

- Dual-sourcing strategies implemented by foundry executives preventing proprietary probe lock-in.

Frequently Asked Questions

What drives the 8.2% semiconductor equipment market growth in this testing sector?

Massive parallel testing requirements for advanced multi-die packages force foundries to upgrade older prober installations. Heterogeneous integration dramatically increases the number of test insertions required per wafer. Operations managers recognize that testing intensity scales much faster than raw silicon volume.

Why do probe card manufacturers hold 58.4% share in product type?

These precision electro-mechanical assemblies act as consumables that require continuous replacement after specified touch-down limits. Foundries burn through thousands of cards annually to prevent pad damage. Tool managers prioritize safety stock to avoid catastrophic fab line stoppages.

How do MEMS probes secure their leading 46.2% position?

Advanced logic nodes require microscopic contact pitches that traditional wire bending cannot achieve. Photolithography processes create identical, highly dense MEMS arrays capable of extreme precision. Test cell architects rely entirely on this architecture for advanced microprocessors.

What operational challenge slows down complete transition to the semiconductor probing process?

Mechanical deflection of the prober chuck under multi-ton parallel testing loads creates a severe alignment bottleneck. Contacting thousands of dies simultaneously distorts the flat surface, leading to edge-die failures. Quality directors struggle to calibrate planarization consistently.

How does China achieve its 9.6% compound expansion rate?

Heavy domestic subsidies encourage local foundries to build independent supply chains immune to international export restrictions. Procurement teams actively qualify regional tool vendors to replace established imports. This aggressive localization accelerates equipment deployments across new domestic fabs.

What differentiates Taiwan's trajectory from Germany's approach?

Taiwanese OSATs focus on massive high-throughput logic testing for global fabless clients. German facilities prioritize high-voltage, extreme-temperature analog testing to satisfy local automotive supply chains. These differing priorities require fundamentally different prober configurations.

Why is thermal management critical for modern test systems?

High-performance logic dies generate tremendous heat during functional testing. Contacting a full wafer simultaneously can melt delicate pad structures if cooling fails. Equipment engineers treat active liquid cooling within the chuck as the primary system differentiator.

How does heterogeneous integration alter the testing sequence?

Assembling multiple chiplets into one package requires absolute certainty that every bare die functions perfectly. Escaping defects destroy the entire expensive module. Test floor managers must push comprehensive validation upstream into the probing stage.

What capability must test equipment suppliers develop by 2036?

Standardized optical interconnects will replace traditional electrical signals in high-speed processors. Current pin manufacturers must integrate photonics validation alongside electrical probing. Firms lacking optical capabilities will lose critical hyperscaler contracts.

Why do tier-1 foundries resist sole-sourcing advanced interfaces?

Depending entirely on one supplier for custom probe designs creates unacceptable operational risk. Supply disruptions halt billion-dollar production lines immediately. Procurement executives mandate dual-sourcing validation for all critical consumable test equipment.

How does pad pitch reduction impact probe card lifespan?

Thinner contact pins wear down faster under repeated mechanical stress. Reduced durability forces operations managers to increase replacement frequencies to maintain signal integrity. This accelerated wear cycle increases total cost of ownership significantly.

What role do OSATs play in test equipment adoption?

These contract packaging facilities purchase high volumes of standardized tools to handle diverse client requirements. While foundries pioneer custom setups, OSATs drive the broader commercialization of stable testing platforms. Their volume purchases support equipment manufacturer margins.

How does automotive safety standards shape testing parameters?

Functional safety mandates require analog chips to operate flawlessly across extreme temperature ranges. Tooling engineers must design probe environments that simulate these conditions directly on the wafer. This requirement drives demand for complex thermal prober chucks.

Why do IDMs upgrade testing infrastructure slower than pure foundries?

Integrated manufacturers only update tools when their specific product designs demand finer pitches or more power. They lack the competitive pressure to support every possible client architecture. Capital constraints keep their older prober systems running longer.

What risk does 300mm wafer testing introduce to production?

Extreme parallelism across the maximum diameter magnifies microscopic temperature gradients. A tiny thermal variance at the edge causes physical misalignment between the probe and pad. Quality directors enforce strict thermal mapping to prevent edge yield losses.

How do procurement directors evaluate true equipment costs?

Initial capital expenditure represents only a fraction of the testing budget. Financial controllers calculate total ownership by dividing tool price by expected touch-down durability. A more expensive system with longer consumable life often proves cheaper overall.

Why do cantilever probes remain relevant despite MEMS growth?

Certain power analog chips require massive electrical currents that melt delicate MEMS structures. Traditional thicker wires handle these high-voltage loads efficiently. Operations managers deploy mixed testing floors to balance precision logic and robust analog requirements.

How does burn-in testing relate to wafer probing?

Probing catches functional errors but often misses early-life degradation issues. Certain mission-critical applications still require sealed-package burn-in validation. Yield engineers combine data from both stages to improve overall fab processes.

What impact does the CHIPS Act have on United States equipment purchasing?

Federal funding covers substantial portions of capital expenditure for new onshore fabs. This artificial financial support accelerates the deployment of advanced 300mm prober systems. Facility managers secure early delivery slots to equip these subsidized lines.

Why is data integration vital for test floor operations?

Isolated test results fail to identify systemic fab issues. Tooling specialists must link prober analytics directly into the central manufacturing execution system. Direct software handshakes between prober and tester enable automated yield improvements.

How does localized fab contamination affect probing budgets?

A single microscopic particle trapped under a probe head destroys the entire custom card instantly. Procurement teams rarely model these catastrophic events into their annual budgets. Maintaining immaculate cleanroom protocols becomes a financial imperative for test managers.

What shift occurs when test cell throughput matches lithography?

Testing ceases to act as a production bottleneck and becomes a proactive yield enhancer. Operations directors scale parallel architectures to stabilize rapid new node introductions. This alignment maximizes total fab profitability while integrating memory IC testing equipment.

Table of Content

- Executive Summary

- Global Market Outlook

- Demand to side Trends

- Supply to side Trends

- Technology Roadmap Analysis

- Analysis and Recommendations

- Market Overview

- Market Coverage / Taxonomy

- Market Definition / Scope / Limitations

- Research Methodology

- Chapter Orientation

- Analytical Lens and Working Hypotheses

- Market Structure, Signals, and Trend Drivers

- Benchmarking and Cross-market Comparability

- Market Sizing, Forecasting, and Opportunity Mapping

- Research Design and Evidence Framework

- Desk Research Programme (Secondary Evidence)

- Company Annual and Sustainability Reports

- Peer-reviewed Journals and Academic Literature

- Corporate Websites, Product Literature, and Technical Notes

- Earnings Decks and Investor Briefings

- Statutory Filings and Regulatory Disclosures

- Technical White Papers and Standards Notes

- Trade Journals, Industry Magazines, and Analyst Briefs

- Conference Proceedings, Webinars, and Seminar Materials

- Government Statistics Portals and Public Data Releases

- Press Releases and Reputable Media Coverage

- Specialist Newsletters and Curated Briefings

- Sector Databases and Reference Repositories

- FMI Internal Proprietary Databases and Historical Market Datasets

- Subscription Datasets and Paid Sources

- Social Channels, Communities, and Digital Listening Inputs

- Additional Desk Sources

- Expert Input and Fieldwork (Primary Evidence)

- Primary Modes

- Qualitative Interviews and Expert Elicitation

- Quantitative Surveys and Structured Data Capture

- Blended Approach

- Why Primary Evidence is Used

- Field Techniques

- Interviews

- Surveys

- Focus Groups

- Observational and In-context Research

- Social and Community Interactions

- Stakeholder Universe Engaged

- C-suite Leaders

- Board Members

- Presidents and Vice Presidents

- R&D and Innovation Heads

- Technical Specialists

- Domain Subject-matter Experts

- Scientists

- Physicians and Other Healthcare Professionals

- Governance, Ethics, and Data Stewardship

- Research Ethics

- Data Integrity and Handling

- Primary Modes

- Tooling, Models, and Reference Databases

- Desk Research Programme (Secondary Evidence)

- Data Engineering and Model Build

- Data Acquisition and Ingestion

- Cleaning, Normalisation, and Verification

- Synthesis, Triangulation, and Analysis

- Quality Assurance and Audit Trail

- Market Background

- Market Dynamics

- Drivers

- Restraints

- Opportunity

- Trends

- Scenario Forecast

- Demand in Optimistic Scenario

- Demand in Likely Scenario

- Demand in Conservative Scenario

- Opportunity Map Analysis

- Product Life Cycle Analysis

- Supply Chain Analysis

- Investment Feasibility Matrix

- Value Chain Analysis

- PESTLE and Porter’s Analysis

- Regulatory Landscape

- Regional Parent Market Outlook

- Production and Consumption Statistics

- Import and Export Statistics

- Market Dynamics

- Global Market Analysis 2021 to 2025 and Forecast, 2026 to 2036

- Historical Market Size Value (USD Million) Analysis, 2021 to 2025

- Current and Future Market Size Value (USD Million) Projections, 2026 to 2036

- Y to o to Y Growth Trend Analysis

- Absolute $ Opportunity Analysis

- Global Market Pricing Analysis 2021 to 2025 and Forecast 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Product Type

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Product Type , 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Product Type , 2026 to 2036

- Probe cards

- Wafer probers

- Test systems

- Probe cards

- Y to o to Y Growth Trend Analysis By Product Type , 2021 to 2025

- Absolute $ Opportunity Analysis By Product Type , 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Probe Technology

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Probe Technology, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Probe Technology, 2026 to 2036

- MEMS probes

- Vertical probes

- Cantilever probes

- MEMS probes

- Y to o to Y Growth Trend Analysis By Probe Technology, 2021 to 2025

- Absolute $ Opportunity Analysis By Probe Technology, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Application

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Application, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Application, 2026 to 2036

- Logic ICs

- Memory ICs

- Analog ICs

- Logic ICs

- Y to o to Y Growth Trend Analysis By Application, 2021 to 2025

- Absolute $ Opportunity Analysis By Application, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By End Use

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By End Use, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By End Use, 2026 to 2036

- Foundries

- IDMs

- OSATs

- Foundries

- Y to o to Y Growth Trend Analysis By End Use, 2021 to 2025

- Absolute $ Opportunity Analysis By End Use, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Wafer Size

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Wafer Size, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Wafer Size, 2026 to 2036

- 300mm wafers

- 200mm wafers

- Others

- 300mm wafers

- Y to o to Y Growth Trend Analysis By Wafer Size, 2021 to 2025

- Absolute $ Opportunity Analysis By Wafer Size, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Region

- Introduction

- Historical Market Size Value (USD Million) Analysis By Region, 2021 to 2025

- Current Market Size Value (USD Million) Analysis and Forecast By Region, 2026 to 2036

- North America

- Latin America

- Western Europe

- Eastern Europe

- East Asia

- South Asia and Pacific

- Middle East & Africa

- Market Attractiveness Analysis By Region

- North America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- USA

- Canada

- Mexico

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- By Country

- Market Attractiveness Analysis

- By Country

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Key Takeaways

- Latin America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Brazil

- Chile

- Rest of Latin America

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- By Country

- Market Attractiveness Analysis

- By Country

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Key Takeaways

- Western Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Germany

- UK

- Italy

- Spain

- France

- Nordic

- BENELUX

- Rest of Western Europe

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- By Country

- Market Attractiveness Analysis

- By Country

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Key Takeaways

- Eastern Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Russia

- Poland

- Hungary

- Balkan & Baltic

- Rest of Eastern Europe

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- By Country

- Market Attractiveness Analysis

- By Country

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Key Takeaways

- East Asia Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- China

- Japan

- South Korea

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- By Country

- Market Attractiveness Analysis

- By Country

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Key Takeaways

- South Asia and Pacific Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- India

- ASEAN

- Australia & New Zealand

- Rest of South Asia and Pacific

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- By Country

- Market Attractiveness Analysis

- By Country

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Key Takeaways

- Middle East & Africa Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkiye

- South Africa

- Other African Union

- Rest of Middle East & Africa

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- By Country

- Market Attractiveness Analysis

- By Country

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Key Takeaways

- Key Countries Market Analysis

- USA

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Canada

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Mexico

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Brazil

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Chile

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Germany

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- UK

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Italy

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Spain

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- France

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- India

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- ASEAN

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Australia & New Zealand

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- China

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Japan

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- South Korea

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Russia

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Poland

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Hungary

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Kingdom of Saudi Arabia

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Turkiye

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- South Africa

- Pricing Analysis

- Market Share Analysis, 2025

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- USA

- Market Structure Analysis

- Competition Dashboard

- Competition Benchmarking

- Market Share Analysis of Top Players

- By Regional

- By Product Type

- By Probe Technology

- By Application

- By End Use

- By Wafer Size

- Competition Analysis

- Competition Deep Dive

- FormFactor, Inc.

- Overview

- Product Portfolio

- Profitability by Market Segments (Product/Age /Sales Channel/Region)

- Sales Footprint

- Strategy Overview

- Marketing Strategy

- Product Strategy

- Channel Strategy

- Technoprobe S.p.A.

- Advantest Corporation

- Tokyo Electron Limited

- MPI Corporation

- Micronics Japan Co., Ltd.

- SV Probe Pte. Ltd.

- FormFactor, Inc.

- Competition Deep Dive

- Assumptions & Acronyms Used

List of Tables

- Table 1: Global Market Value (USD Million) Forecast by Region, 2021 to 2036

- Table 2: Global Market Value (USD Million) Forecast by Product Type , 2021 to 2036

- Table 3: Global Market Value (USD Million) Forecast by Probe Technology, 2021 to 2036

- Table 4: Global Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 5: Global Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 6: Global Market Value (USD Million) Forecast by Wafer Size, 2021 to 2036

- Table 7: North America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 8: North America Market Value (USD Million) Forecast by Product Type , 2021 to 2036

- Table 9: North America Market Value (USD Million) Forecast by Probe Technology, 2021 to 2036

- Table 10: North America Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 11: North America Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 12: North America Market Value (USD Million) Forecast by Wafer Size, 2021 to 2036

- Table 13: Latin America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 14: Latin America Market Value (USD Million) Forecast by Product Type , 2021 to 2036

- Table 15: Latin America Market Value (USD Million) Forecast by Probe Technology, 2021 to 2036

- Table 16: Latin America Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 17: Latin America Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 18: Latin America Market Value (USD Million) Forecast by Wafer Size, 2021 to 2036

- Table 19: Western Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 20: Western Europe Market Value (USD Million) Forecast by Product Type , 2021 to 2036

- Table 21: Western Europe Market Value (USD Million) Forecast by Probe Technology, 2021 to 2036

- Table 22: Western Europe Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 23: Western Europe Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 24: Western Europe Market Value (USD Million) Forecast by Wafer Size, 2021 to 2036

- Table 25: Eastern Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 26: Eastern Europe Market Value (USD Million) Forecast by Product Type , 2021 to 2036

- Table 27: Eastern Europe Market Value (USD Million) Forecast by Probe Technology, 2021 to 2036

- Table 28: Eastern Europe Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 29: Eastern Europe Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 30: Eastern Europe Market Value (USD Million) Forecast by Wafer Size, 2021 to 2036

- Table 31: East Asia Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 32: East Asia Market Value (USD Million) Forecast by Product Type , 2021 to 2036

- Table 33: East Asia Market Value (USD Million) Forecast by Probe Technology, 2021 to 2036

- Table 34: East Asia Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 35: East Asia Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 36: East Asia Market Value (USD Million) Forecast by Wafer Size, 2021 to 2036

- Table 37: South Asia and Pacific Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 38: South Asia and Pacific Market Value (USD Million) Forecast by Product Type , 2021 to 2036

- Table 39: South Asia and Pacific Market Value (USD Million) Forecast by Probe Technology, 2021 to 2036

- Table 40: South Asia and Pacific Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 41: South Asia and Pacific Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 42: South Asia and Pacific Market Value (USD Million) Forecast by Wafer Size, 2021 to 2036

- Table 43: Middle East & Africa Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 44: Middle East & Africa Market Value (USD Million) Forecast by Product Type , 2021 to 2036

- Table 45: Middle East & Africa Market Value (USD Million) Forecast by Probe Technology, 2021 to 2036

- Table 46: Middle East & Africa Market Value (USD Million) Forecast by Application, 2021 to 2036

- Table 47: Middle East & Africa Market Value (USD Million) Forecast by End Use, 2021 to 2036

- Table 48: Middle East & Africa Market Value (USD Million) Forecast by Wafer Size, 2021 to 2036

List of Figures

- Figure 1: Global Market Pricing Analysis

- Figure 2: Global Market Value (USD Million) Forecast 2021-2036

- Figure 3: Global Market Value Share and BPS Analysis by Product Type , 2026 and 2036

- Figure 4: Global Market Y-o-Y Growth Comparison by Product Type , 2026-2036

- Figure 5: Global Market Attractiveness Analysis by Product Type

- Figure 6: Global Market Value Share and BPS Analysis by Probe Technology, 2026 and 2036

- Figure 7: Global Market Y-o-Y Growth Comparison by Probe Technology, 2026-2036

- Figure 8: Global Market Attractiveness Analysis by Probe Technology

- Figure 9: Global Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 10: Global Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 11: Global Market Attractiveness Analysis by Application

- Figure 12: Global Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 13: Global Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 14: Global Market Attractiveness Analysis by End Use

- Figure 15: Global Market Value Share and BPS Analysis by Wafer Size, 2026 and 2036

- Figure 16: Global Market Y-o-Y Growth Comparison by Wafer Size, 2026-2036

- Figure 17: Global Market Attractiveness Analysis by Wafer Size

- Figure 18: Global Market Value (USD Million) Share and BPS Analysis by Region, 2026 and 2036

- Figure 19: Global Market Y-o-Y Growth Comparison by Region, 2026-2036

- Figure 20: Global Market Attractiveness Analysis by Region

- Figure 21: North America Market Incremental Dollar Opportunity, 2026-2036

- Figure 22: Latin America Market Incremental Dollar Opportunity, 2026-2036

- Figure 23: Western Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 24: Eastern Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 25: East Asia Market Incremental Dollar Opportunity, 2026-2036

- Figure 26: South Asia and Pacific Market Incremental Dollar Opportunity, 2026-2036

- Figure 27: Middle East & Africa Market Incremental Dollar Opportunity, 2026-2036

- Figure 28: North America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 29: North America Market Value Share and BPS Analysis by Product Type , 2026 and 2036

- Figure 30: North America Market Y-o-Y Growth Comparison by Product Type , 2026-2036

- Figure 31: North America Market Attractiveness Analysis by Product Type

- Figure 32: North America Market Value Share and BPS Analysis by Probe Technology, 2026 and 2036

- Figure 33: North America Market Y-o-Y Growth Comparison by Probe Technology, 2026-2036

- Figure 34: North America Market Attractiveness Analysis by Probe Technology

- Figure 35: North America Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 36: North America Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 37: North America Market Attractiveness Analysis by Application

- Figure 38: North America Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 39: North America Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 40: North America Market Attractiveness Analysis by End Use

- Figure 41: North America Market Value Share and BPS Analysis by Wafer Size, 2026 and 2036

- Figure 42: North America Market Y-o-Y Growth Comparison by Wafer Size, 2026-2036

- Figure 43: North America Market Attractiveness Analysis by Wafer Size

- Figure 44: Latin America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 45: Latin America Market Value Share and BPS Analysis by Product Type , 2026 and 2036

- Figure 46: Latin America Market Y-o-Y Growth Comparison by Product Type , 2026-2036

- Figure 47: Latin America Market Attractiveness Analysis by Product Type

- Figure 48: Latin America Market Value Share and BPS Analysis by Probe Technology, 2026 and 2036

- Figure 49: Latin America Market Y-o-Y Growth Comparison by Probe Technology, 2026-2036

- Figure 50: Latin America Market Attractiveness Analysis by Probe Technology

- Figure 51: Latin America Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 52: Latin America Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 53: Latin America Market Attractiveness Analysis by Application

- Figure 54: Latin America Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 55: Latin America Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 56: Latin America Market Attractiveness Analysis by End Use

- Figure 57: Latin America Market Value Share and BPS Analysis by Wafer Size, 2026 and 2036

- Figure 58: Latin America Market Y-o-Y Growth Comparison by Wafer Size, 2026-2036

- Figure 59: Latin America Market Attractiveness Analysis by Wafer Size

- Figure 60: Western Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 61: Western Europe Market Value Share and BPS Analysis by Product Type , 2026 and 2036

- Figure 62: Western Europe Market Y-o-Y Growth Comparison by Product Type , 2026-2036

- Figure 63: Western Europe Market Attractiveness Analysis by Product Type

- Figure 64: Western Europe Market Value Share and BPS Analysis by Probe Technology, 2026 and 2036

- Figure 65: Western Europe Market Y-o-Y Growth Comparison by Probe Technology, 2026-2036

- Figure 66: Western Europe Market Attractiveness Analysis by Probe Technology

- Figure 67: Western Europe Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 68: Western Europe Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 69: Western Europe Market Attractiveness Analysis by Application

- Figure 70: Western Europe Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 71: Western Europe Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 72: Western Europe Market Attractiveness Analysis by End Use

- Figure 73: Western Europe Market Value Share and BPS Analysis by Wafer Size, 2026 and 2036

- Figure 74: Western Europe Market Y-o-Y Growth Comparison by Wafer Size, 2026-2036

- Figure 75: Western Europe Market Attractiveness Analysis by Wafer Size

- Figure 76: Eastern Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 77: Eastern Europe Market Value Share and BPS Analysis by Product Type , 2026 and 2036

- Figure 78: Eastern Europe Market Y-o-Y Growth Comparison by Product Type , 2026-2036

- Figure 79: Eastern Europe Market Attractiveness Analysis by Product Type

- Figure 80: Eastern Europe Market Value Share and BPS Analysis by Probe Technology, 2026 and 2036

- Figure 81: Eastern Europe Market Y-o-Y Growth Comparison by Probe Technology, 2026-2036

- Figure 82: Eastern Europe Market Attractiveness Analysis by Probe Technology

- Figure 83: Eastern Europe Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 84: Eastern Europe Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 85: Eastern Europe Market Attractiveness Analysis by Application

- Figure 86: Eastern Europe Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 87: Eastern Europe Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 88: Eastern Europe Market Attractiveness Analysis by End Use

- Figure 89: Eastern Europe Market Value Share and BPS Analysis by Wafer Size, 2026 and 2036

- Figure 90: Eastern Europe Market Y-o-Y Growth Comparison by Wafer Size, 2026-2036

- Figure 91: Eastern Europe Market Attractiveness Analysis by Wafer Size

- Figure 92: East Asia Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 93: East Asia Market Value Share and BPS Analysis by Product Type , 2026 and 2036

- Figure 94: East Asia Market Y-o-Y Growth Comparison by Product Type , 2026-2036

- Figure 95: East Asia Market Attractiveness Analysis by Product Type

- Figure 96: East Asia Market Value Share and BPS Analysis by Probe Technology, 2026 and 2036

- Figure 97: East Asia Market Y-o-Y Growth Comparison by Probe Technology, 2026-2036

- Figure 98: East Asia Market Attractiveness Analysis by Probe Technology

- Figure 99: East Asia Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 100: East Asia Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 101: East Asia Market Attractiveness Analysis by Application

- Figure 102: East Asia Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 103: East Asia Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 104: East Asia Market Attractiveness Analysis by End Use

- Figure 105: East Asia Market Value Share and BPS Analysis by Wafer Size, 2026 and 2036

- Figure 106: East Asia Market Y-o-Y Growth Comparison by Wafer Size, 2026-2036

- Figure 107: East Asia Market Attractiveness Analysis by Wafer Size

- Figure 108: South Asia and Pacific Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 109: South Asia and Pacific Market Value Share and BPS Analysis by Product Type , 2026 and 2036

- Figure 110: South Asia and Pacific Market Y-o-Y Growth Comparison by Product Type , 2026-2036

- Figure 111: South Asia and Pacific Market Attractiveness Analysis by Product Type

- Figure 112: South Asia and Pacific Market Value Share and BPS Analysis by Probe Technology, 2026 and 2036

- Figure 113: South Asia and Pacific Market Y-o-Y Growth Comparison by Probe Technology, 2026-2036

- Figure 114: South Asia and Pacific Market Attractiveness Analysis by Probe Technology

- Figure 115: South Asia and Pacific Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 116: South Asia and Pacific Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 117: South Asia and Pacific Market Attractiveness Analysis by Application

- Figure 118: South Asia and Pacific Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 119: South Asia and Pacific Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 120: South Asia and Pacific Market Attractiveness Analysis by End Use

- Figure 121: South Asia and Pacific Market Value Share and BPS Analysis by Wafer Size, 2026 and 2036

- Figure 122: South Asia and Pacific Market Y-o-Y Growth Comparison by Wafer Size, 2026-2036

- Figure 123: South Asia and Pacific Market Attractiveness Analysis by Wafer Size

- Figure 124: Middle East & Africa Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 125: Middle East & Africa Market Value Share and BPS Analysis by Product Type , 2026 and 2036

- Figure 126: Middle East & Africa Market Y-o-Y Growth Comparison by Product Type , 2026-2036

- Figure 127: Middle East & Africa Market Attractiveness Analysis by Product Type

- Figure 128: Middle East & Africa Market Value Share and BPS Analysis by Probe Technology, 2026 and 2036

- Figure 129: Middle East & Africa Market Y-o-Y Growth Comparison by Probe Technology, 2026-2036

- Figure 130: Middle East & Africa Market Attractiveness Analysis by Probe Technology

- Figure 131: Middle East & Africa Market Value Share and BPS Analysis by Application, 2026 and 2036

- Figure 132: Middle East & Africa Market Y-o-Y Growth Comparison by Application, 2026-2036

- Figure 133: Middle East & Africa Market Attractiveness Analysis by Application

- Figure 134: Middle East & Africa Market Value Share and BPS Analysis by End Use, 2026 and 2036

- Figure 135: Middle East & Africa Market Y-o-Y Growth Comparison by End Use, 2026-2036

- Figure 136: Middle East & Africa Market Attractiveness Analysis by End Use

- Figure 137: Middle East & Africa Market Value Share and BPS Analysis by Wafer Size, 2026 and 2036

- Figure 138: Middle East & Africa Market Y-o-Y Growth Comparison by Wafer Size, 2026-2036

- Figure 139: Middle East & Africa Market Attractiveness Analysis by Wafer Size

- Figure 140: Global Market - Tier Structure Analysis

- Figure 141: Global Market - Company Share Analysis