Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market

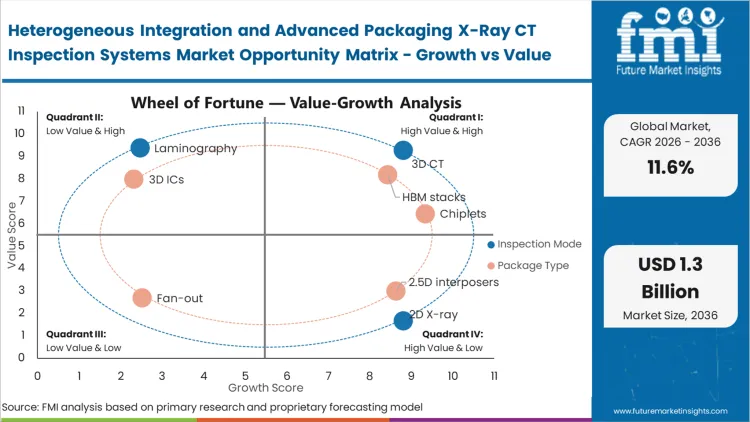

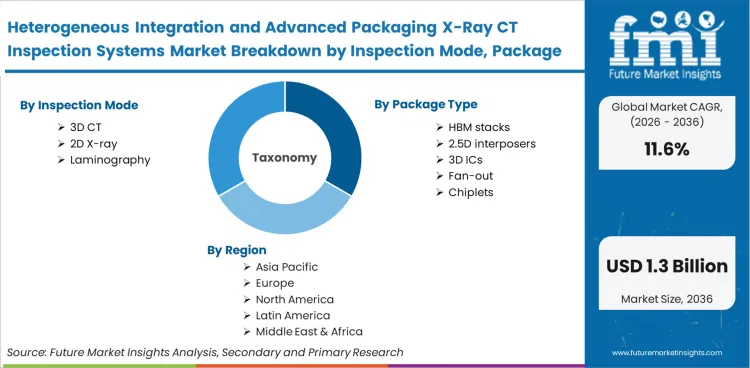

Heterogeneous integration and advanced packaging x-ray CT inspection systems market is segmented by Inspection Mode (3D CT, 2D X-ray, Laminography), Package Type (HBM stacks, 2.5D interposers, 3D ICs, Fan-out, Chiplets), Automation Level (Inline, Nearline, Offline lab), Resolution Class (Submicron, 1 to 3 µm, Above 3 µm), Buyer Type (OSATs, Foundries, IDMs, R&D labs), and Region. Forecast for 2026 to 2036.

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Size, Market Forecast and Outlook By FMI

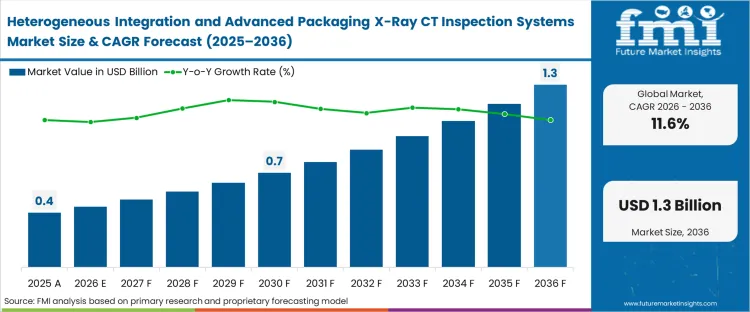

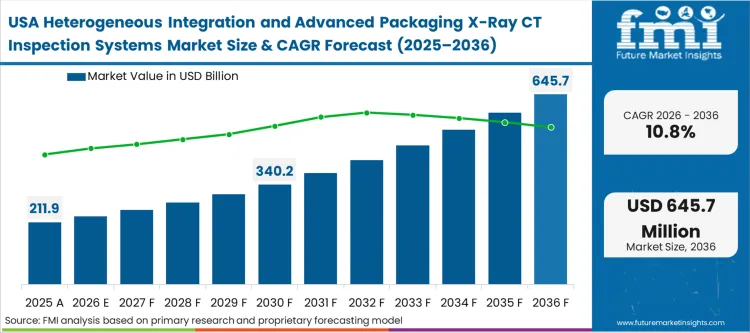

Demand across the heterogeneous integration and advanced packaging x-ray CT inspection systems market reached USD 0.39 billion in 2025. Sales hit USD 0.44 billion in 2026 at a CAGR of 11.60% during 2026 to 2036. Continued investment pushes the total valuation upward to USD 1.32 billion through 2036 as submicron fault isolation becomes a mandatory inline step before final overmolding.

OSAT engineering directors currently face intense pressure to intercept micro-voids before stacking subsequent silicon layers. Escaping a single defective 10-micron joint ruins thousands of dollars of known-good dies. Yield engineers recognize electrical testing catches failures too late, forcing direct semiconductor inspection systems integration into active production flows. Organizations navigating the advanced packaging x-ray inspection market realize commercial penalties for delay are severe: assembly houses lacking advanced packaging defect inspection systems lose lucrative fabless contracts to competitors guaranteeing known-good components.

Summary of Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market

- Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Definition

- Nondestructive volumetric imaging equipment built to isolate hidden interconnect defects inside stacked semiconductor architectures without requiring physical dissection.

- Demand Drivers in the Market

- High-bandwidth memory yield pressure forces test engineers to identify micro-voids prior to final packaging.

- Chiplet cost economics compel OSAT directors to intercept interconnection failures before adding expensive known-good dies.

- Shrinking TSV geometries push metrology heads to capture submicron alignment deviations accurately.

- Key Segments Analyzed in the FMI Report

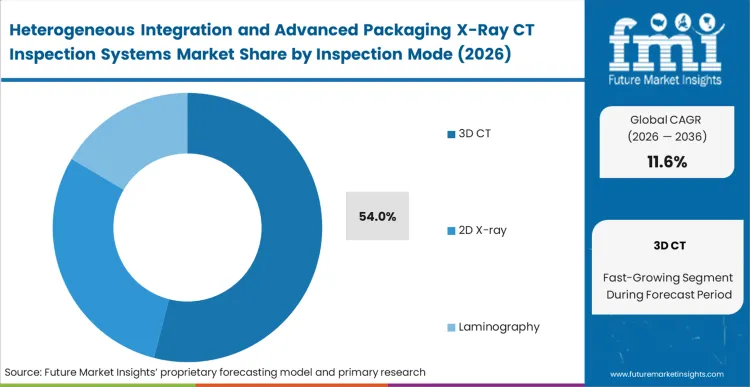

- 3D CT is expected to hold 54.0% share in 2026, satisfying volumetric fault isolation requirements.

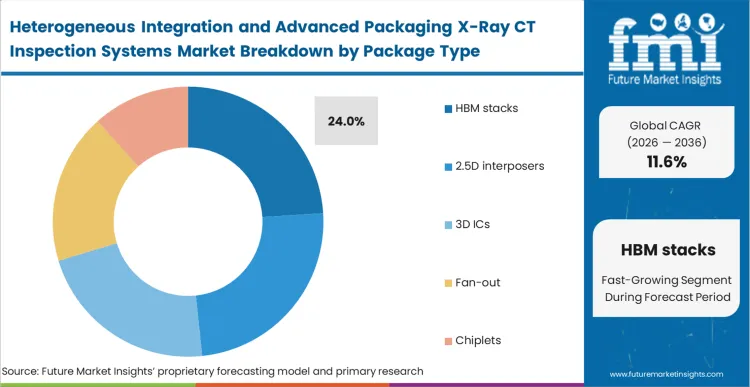

- HBM stacks captures 24.0% share in 2026, driven by intense thermal and bump-density qualification challenges.

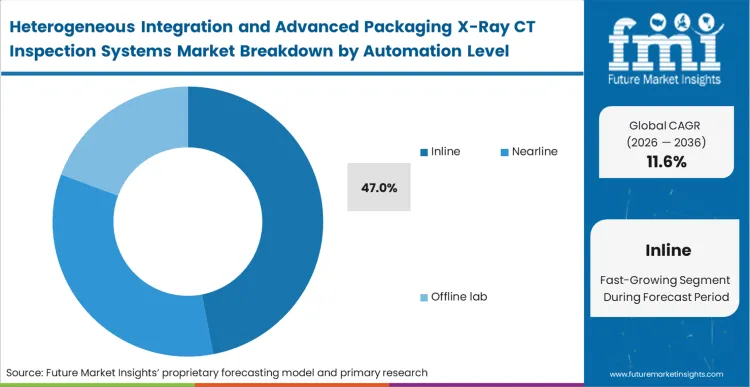

- Inline leads automation adoption by matching advanced imaging speed with production takt time.

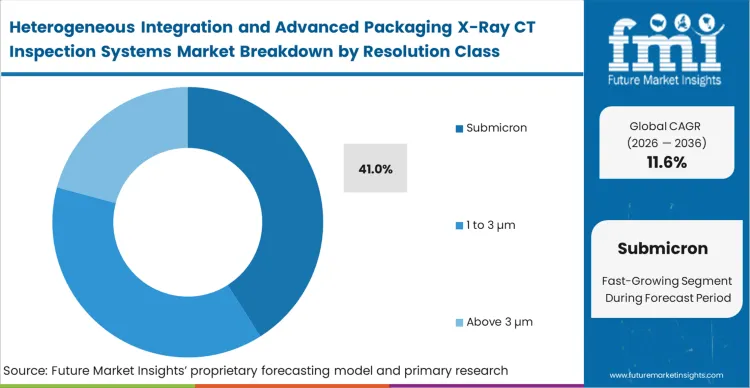

- Submicron commands 41.0% share in 2026, aligning perfectly with advanced interposer bump pitches.

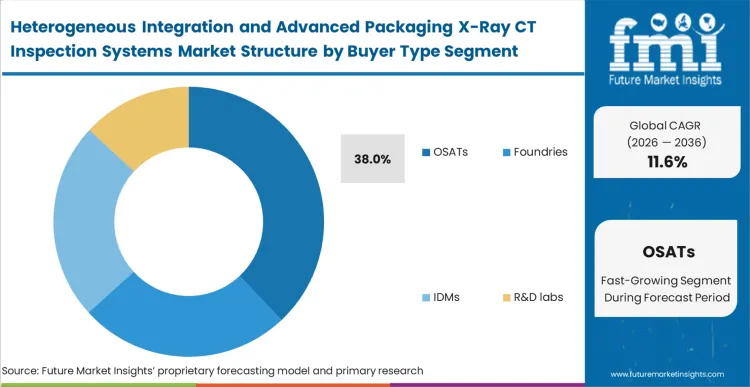

- OSATs account for 38.0% share in 2026, acting as primary assembly executors for fabless designers.

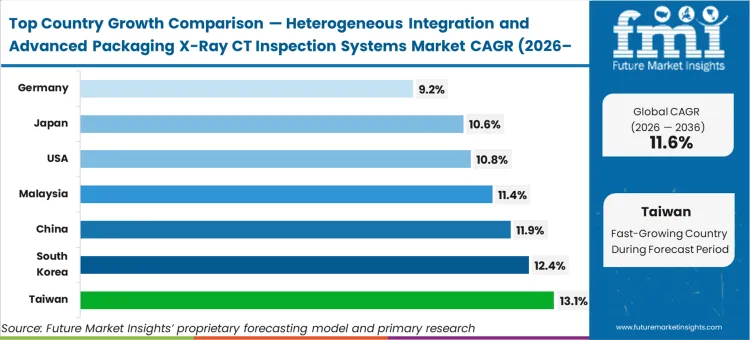

- Taiwan: 13.1% compound growth, reflecting unmatched concentration of advanced packaging capacity.

- Analyst Opinion at FMI

- Rahul Pandita, Principal Analyst, Technology, at FMI, observes, "Equipment buyers assume raw resolution determines inspection success. Cleanroom managers select platforms based on reconstruction algorithm speed. Generating a precise submicron voxel map matters little if image processing delays an entire packaging line. True competitive separation occurs when suppliers combine adequate hardware with AI defect recognition x-ray workflows that perfectly match foundry cycle times."

- Strategic Implications / Executive Takeaways

- OSAT procurement teams must evaluate software reconstruction speed alongside hardware resolution to prevent cleanroom bottlenecks.

- Foundry yield architects face mounting pressure to deploy inline volumetric scanning before committing to expensive layer stacking.

- Inspection equipment manufacturers risk replacement if platforms cannot integrate directly with automated factory transport mechanisms.

Key Takeaways

| Metric | Details |

|---|---|

| Industry Size (2026) | USD 0.44 billion |

| Industry Value (2036) | USD 1.32 billion |

| CAGR (2026 to 2036) | 11.60% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Production logic changes permanently once reconstruction algorithms process submicron voxel data faster than factory takt times. Scanning entire 300mm wafers inline without breaking vacuum environments allows foundries to implement true feed-forward process control. Engineers shift from post-mortem failure analysis to active yield rescue utilizing semiconductor packaging CT inspection systems.

Taiwan leads at 13.1% relying on intense TSMC capacity expansion. South Korea tracks closely at 12.4% with memory makers standardizing internal HBM x-ray inspection systems. China advances at 11.9% as domestic chiplet packaging inspection systems mature rapidly. Malaysia scales at 11.4% reflecting concentrated assembly modernization. The United States expands at 10.8% prioritizing high-value reshoring. Japan grows at 10.6% optimizing substrate yield limits. Germany adds 9.2% supporting industrial power packaging requirements. Divergence stems from raw scale versus specialised low-volume qualification.

Market Definition

Nondestructive volumetric imaging equipment designed specifically for resolving internal structural defects inside stacked semiconductor packages. Equipment maps solder micro-bumps, through-silicon vias, and wire bonds across multiple z-axis layers without physical cross-sectioning. Hardware integrating high-energy micro-focus tubes with specialized detector arrays forms core heterogeneous integration quality control infrastructure.

Inclusions

Systems utilizing computed tomography and specialized metrology equipment software targeted directly at semiconductor fault isolation. Hardware encompassing specific micro-focus tubes and flat panel detectors integrated with automated handlers for cleanroom environments. Analysis algorithms designed explicitly for automated defect recognition in dense integrated circuits fall under advanced packaging x-ray CT market forecast modeling.

Exclusions

General-purpose printed circuit board scanners lack submicron resolution necessary for silicon interposers and remain entirely excluded. Medical imaging hardware falls outside parameters due to insufficient focal spot density and incompatible software architectures. Destructive cross-sectioning tools sit outside volumetric imaging boundaries, while basic x-ray laminography packaging tools lacking full 3D reconstruction capabilities face separate evaluation.

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Research Methodology

- Primary Research: Yield engineering managers, OSAT cleanroom directors, and foundry quality architects.

- Desk Research: Semiconductor equipment consortium roadmaps, cleanroom qualification registries, and packaging patent filings.

- Market-Sizing and Forecasting: Cleanroom footprint expansion data and specific TSV pitch reduction timelines.

- Data Validation and Update Cycle: Wafer start logs and pure-play foundry capital expenditure disclosures.

Segmental Analysis

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis by Inspection Mode

Volumetric reconstruction geometry explains why 3D CT captures 54.0% share. Conventional planar imaging projects overlapping features onto a single plane, obscuring critical defects located between stacked active silicon layers. Quality control directors at Tier-1 foundries mandate computed tomography because it separates these z-axis layers mathematically, revealing micro-voids that 2D transmission inherently masks. Procurement teams rarely factor massive data storage overhead into capital expenditure models; submicron 3D x-ray inspection generates terabytes of voxel data per wafer, quietly shifting operational constraints from imaging hardware to IT network bandwidth. Cleanroom managers who install platforms without upgrading factory data pipelines face immediate throughput collapse, eventually forcing expensive network retrofits while multi-million-dollar scanners sit idle.

- Defect resolution constraint: Foundries cannot resolve hidden TSV misalignments using planar views. Quality engineers gain distinct z-axis visibility utilizing semiconductor package failure analysis x-ray CT.

- Voxel storage penalty: Cleanroom IT architecture struggles with massive reconstruction files. Network administrators must upgrade bandwidth or face production halts.

- Throughput normalization: Software optimizations compress reconstruction timelines significantly. Operations directors eventually achieve inline speeds matching factory takt times.

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis by Package Type

Thermal realities dictate why HBM stacks represent 24.0% share. Stacking twelve memory dies requires thousands of micro-bumps per layer, generating unprecedented stress during reflow processes. Memory product engineers rely on advanced semiconductor packaging CT protocols to verify bump continuity because electrical opens often disguise themselves as thermal-induced intermittent failures later. FMI analysts observe that while interposers draw industry attention, HBM micro-bump inspection quietly consumes majority high-end inspection capacity due to unforgiving known-good-die economics. Foundries assembling these stacks treat chiplet package defect analysis as an absolute requirement rather than a statistical sampling exercise, creating vendor lock-in scenarios for equipment suppliers passing initial qualification. Memory manufacturers attempting to skip 100% volumetric inspection frequently scrap entire multi-die assemblies.

- Reflow verification: Micro-bumps warp during thermal cycling. Packaging engineers detect non-wets before committing subsequent memory dies.

- Economic penalty: Scrapping completed memory stacks destroys margin. Procurement officers mandate inline inspection to intercept flaws early.

- Sampling limitation: Statistical quality control fails for dense architectures requiring precise hybrid bonding inspection x-ray CT. Yield managers must inspect every unit to guarantee performance.

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis by Automation Level

Factory integration physics drive Inline automation to 47.0% share. Transporting delicate 300mm wafers to an offline lab breaks cleanroom vacuum environments and introduces fatal handling risks. Factory automation managers require inline x-ray CT semiconductor scanners that accept standardised FOUPs directly from overhead hoists, performing scans without human intervention. Based on FMI's assessment, true technical differentiators for inline systems involve vibration isolation engineering allowing submicron imaging alongside thumping factory equipment, not just hardware precision. Traditional offline package failure analysis offers superior baseline resolution, yet production directors willingly sacrifice marginal clarity for logistical safety. Facilities attempting to rely entirely on nearline sampling consistently experience delayed defect feedback loops.

- Vibration isolation: Factory floors transfer micro-seismic noise. Equipment engineers implement active damping to preserve imaging clarity.

- Handling risk: Manual transport introduces particulate contamination. Automation managers eliminate touchpoints to protect exposed wafer surfaces.

- Feedback latency: Offline analysis delays process correction. Production directors require immediate data to halt drifting deposition tools.

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis by Resolution Class

Pitch scaling necessitates why Submicron resolution captures 41.0% share. Modern chiplet designs utilize interconnect pitches approaching 10 micrometers, rendering standard industrial flat panel detectors entirely blind to bridging or voiding defects. Metrology directors specify submicron focal spots for precise solder bump CT inspection to distinguish individual spheres within densely packed arrays. Hardware specifications obscure severe degradation of tube lifespan when running continuously at nanometer-scale focal spots, quietly inflating operating expenses for OSAT providers. Cleanroom maintenance teams discover replacing specialized TSV inspection x-ray sources constitutes massive hidden recurring costs not reflected in initial procurement negotiations. Organizations selecting lower resolution tools inevitably fail basic qualification audits.

- Pitch verification: Dense arrays obscure individual solder joints. Metrology directors apply submicron beams to isolate single-bump failures.

- Consumable expense: Micro-focus tubes degrade rapidly under continuous load. Maintenance teams face frequent, costly hardware replacement cycles.

- Qualification barrier: Inferior resolution fails fabless design audits. Sales directors lose advanced contracts if cleanrooms lack capability.

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis by Buyer Type

Contractual liability explains why OSATs hold 38.0% share. Fabless designers ship extremely expensive bare dies to assembly partners, transferring all financial risk for packaging defects to contract manufacturers. OSAT operations directors purchase top-tier OSAT inspection tools primarily as defensive liability mechanisms, proving defects originated in silicon rather than during attachment processes involving flip chip interconnects. FMI's analysis indicates this defensive dynamic forces contract assemblers to over-index on inspection hardware relative to actual capital budgets. While foundry packaging inspection expands for yield learning, OSATs deploy systems strictly for margin protection and warranty validation. Assembly houses trying to minimize inspection capital absorb massive scrap costs when they cannot prove substrate flaws pre-existed their intervention.

- Liability protection: Fabless designers blame assemblers for failures. OSAT directors use volumetric scans to document incoming silicon defects.

- Capital allocation: Defensive imaging consumes hardware budgets. Procurement managers sacrifice other capacity expansions to fund mandatory inspection tools.

- Yield learning: Foundries trace packaging flaws back to fabrication. Process engineers adjust upstream parameters based on volumetric feedback.

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Drivers, Restraints, and Opportunities

Yield economics in extreme-density architectures compel OSAT engineering directors to intercept interconnect failures immediately using advanced packaging defect inspection systems. Escaping a single void in a high-bandwidth memory stack destroys thousands of dollars in known-good dies. Delaying volumetric implementation forces assembly houses to absorb massive scrap costs when thermal stress later reveals hidden non-wets. Production managers cannot rely on post-process electrical testing because it offers zero root-cause geometry data. Implementing submicron CT scanning provides immediate process feedback, allowing technicians to halt drifting bonders before ruining subsequent expensive silicon batches.

Image reconstruction latency severely slows adoption even when cleanroom directors desperately want inline volumetric data. Mathematical 3d ic packaging reconstruction of terabyte-scale voxel maps takes minutes per die using standard processing architectures. Factory takt times demand seconds. This fundamental computational bottleneck prevents true 100% inline inspection, forcing yield managers to settle for statistical sampling that inevitably misses isolated micro-voids. AI-accelerated sparse-data reconstruction algorithms show promise, yet current validation standards resist non-deterministic imaging outputs.

Opportunities in the Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market

- Sparse-data AI reconstruction: Software engineers bypass hardware limits incorporating AI defect recognition x-ray. Cleanroom managers achieve inline throughput using predictive algorithms.

- Automated FOUP integration: Handlers eliminate human transport risks. Automation directors deploy inspection directly within active wafer transport tracks.

- Multi-modal sensor fusion: Equipment combines X-ray with acoustic data. Yield architects gain comprehensive package testing sockets insight from a single platform.

Regional Analysis

As per the regional assessment, the Heterogeneous Integration and Advanced Packaging X‑Ray CT Inspection Systems market is categorised into North America, Latin America, Western Europe, Eastern Europe, Asia Pacific, and the Middle East & Africa, covering over 40 countries.

.webp)

| Country | CAGR (2026 to 2036) |

|---|---|

| Taiwan | 13.1% |

| South Korea | 12.4% |

| China | 11.9% |

| Malaysia | 11.4% |

| United States | 10.8% |

| Japan | 10.6% |

| Germany | 9.2% |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Asia Pacific Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis

Capacity dominance dictates adoption curves across Asia Pacific. Pure-play foundries and dedicated assembly houses cluster their most advanced capabilities precisely where global fabless designers route highest-volume orders. Facility directors deploy submicron CT systems not as R&D novelties, but as mandatory inline gatekeepers for high-bandwidth memory and complex interposer volumes. FMI analysts note this geographic concentration creates hyper-competitive equipment procurement environments; tool vendors failing qualification at a single mega-fab essentially lose access to majority global advanced packaging volume. Local equipment ecosystems rise rapidly to support this density, pushing inspection throughput speeds faster than anywhere else.

- Taiwan: TSMC capacity expansion forces aggressive inline adoption, driving a 13.1% compound growth trajectory for Taiwan heterogeneous integration and advanced packaging x-ray CT inspection systems industry. Foundry directors integrate submicron inspection directly into Chiayi and Tainan wafer processing equipment lines to validate complex silicon interposers. Regional buyers successfully qualifying new AI defect recognition x-ray reconstruction software secure massive multi-year deployment contracts, capturing absolute market dominance before competing foundries can establish similar volumetric throughput.

- South Korea: In South Korea, memory manufacturers standardizing strict qualification protocols for vertical stacks push the heterogeneous integration and advanced packaging x-ray CT inspection systems segment growth to 12.4%. Yield engineers mandate 100% volumetric verification for every multi-die assembly, utilizing HBM micro-bump inspection platforms to identify hidden non-wets. Operations teams executing this strategy protect vital profit margins from catastrophic scrap events, permanently altering the operational baseline for high-bandwidth memory production across the entire peninsula's advanced manufacturing sector.

- China: Process architects utilize industrial radiography CT platforms to stitch together diverse domestic silicon sources independently. Domestic chiplet ecosystem development bypasses traditional monolithic scaling constraints, accelerating the China’s heterogeneous integration and advanced packaging x-ray CT inspection systems segment demand at 11.9%. The self-reliance push permanently elevates local inspection demand beyond standard consumer electronics baselines, granting regional chiplet packaging inspection systems suppliers unprecedented leverage to refine proprietary defect recognition algorithms without relying on Western baseline technologies.

- Malaysia: Concentrated assembly footprints undergoing rapid, capital-intensive modernization help register 11.4% growth in Malaysia’s heterogeneous integration and advanced packaging x-ray CT inspection systems industry. OSAT facility managers upgrade legacy wire-bond testing infrastructure to support complex flip-chip demands, prioritising inline x-ray CT semiconductor tools. Facilities achieving submicron volumetric verification capability immediately capture higher-margin contracts from global fabless designers, shifting the entire national packaging sector away from low-cost volume processing toward highly specialised, extreme-yield advanced semiconductor assembly operations.

- Japan: Substrate manufacturers pushing the absolute physical limits characterizing organic packaging layers scale Japan’s heterogeneous integration and advanced packaging x-ray CT inspection systems demand at 10.6%. Quality assurance directors deploy high-resolution TSV inspection x-ray systems specifically to verify microscopic via integrity before final bonding. Deep integration between local advanced material suppliers and legacy equipment vendors creates highly specialized, closed-loop qualification cycles that effectively insulate Japanese substrate producers from lower-cost regional competitors seeking to enter the interposer supply chain.

FMI's report includes India, Singapore, and Australia. Evolving semiconductor corridors in Southeast Asia require foundational inspection capability to attract initial Tier-1 assembly investments.

North America Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis

Strategic reshoring mandates redefine inspection deployment across North America. Federal incentives push manufacturers to establish high-value, low-volume assembly lines focused on aerospace, defense, and specialized artificial intelligence hardware. Quality assurance directors working under strict military or automotive standards require absolute traceability, utilizing CT systems to generate permanent volumetric records for every shipped component. In FMI's view, this environment prioritizes absolute resolution and data fidelity over raw throughput speed. Facilities handling specialized quantum computing packages treat inspection hardware as a primary selling point securing government contracts.

- United States: When it comes to the heterogeneous integration and advanced packaging x-ray CT inspection industry of the US, strict federal reshoring initiatives demanding zero-defect verification drive a 10.8% expansion. Quality directors implement comprehensive advanced packaging defect inspection systems specifically for aerospace, defense, and specialized AI logic architectures. Cleanrooms establishing these absolute traceability records win exclusive long-term government procurement agreements, fundamentally transforming regional facility economics by prioritizing ultra-reliable, low-volume manufacturing workflows over pure throughput-driven consumer electronics assembly models dominating overseas markets.

FMI's report includes Canada and Mexico. Cross-border supply chains push baseline automated inspection requirements into emerging North American assembly hubs.

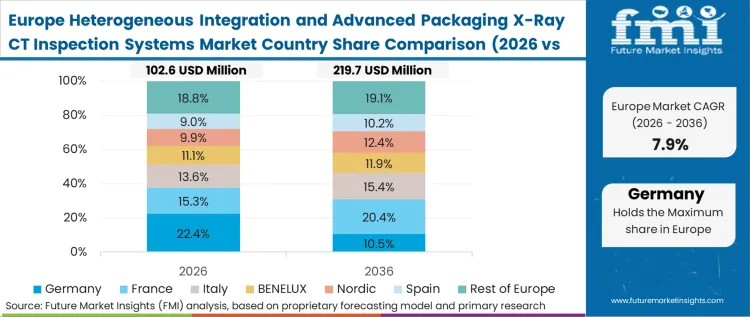

Europe Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis

Automotive power electronics drive specific inspection architectures across Western Europe. Industrial manufacturers focus heavily on silicon carbide integration and robust power modules rather than consumer logic chiplets. Reliability engineers deploy volumetric scanning to detect subtle thermal voids in heavy solder interfaces that would eventually cause catastrophic failure in electric vehicle drivetrains. FMI observes European procurement teams prioritize equipment longevity and specialized dense-metal penetration capabilities over submicron resolution required for memory stacks.

- Germany: Industrial power module reliability dictating strict hardware inspection parameters secures a 9.2% trajectory for the German heterogeneous integration and advanced packaging x-ray CT inspection industry. Automotive engineers mandate deep volumetric scanning specifically targeting dense silicon carbide bonding layers within EV drivetrains. Manufacturers utilizing specialized hybrid bonding inspection x-ray CT capabilities secure vital qualification status with major European automakers, establishing a structural advantage in the high-power electronics sector that pure logic assemblers cannot replicate without extensive validation.

FMI's report includes United Kingdom, France, and Italy. Regional automotive supply chains dictate standardized inspection protocols for emerging power electronics facilities.

Competitive Aligners for Market Players

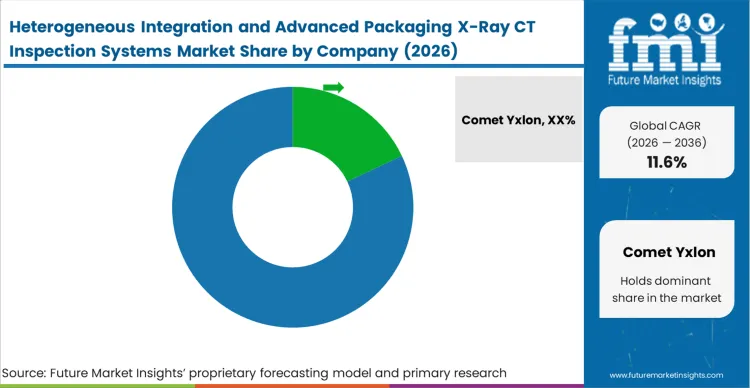

Technological separation in this segment hinges completely on image reconstruction speed. Comet Yxlon and Carl Zeiss Microscopy recognize generating a submicron voxel map means nothing if processing capital equipment data stops production lines. Engineering teams focus massive R&D budgets on sparse-data algorithms and AI-accelerated noise reduction. Competitors offering brilliant resolution but slow analysis find themselves permanently relegated to offline failure analysis labs rather than lucrative high-volume inline deployments.

Incumbents possess deep, proprietary integration libraries with factory automation software. Establishing seamless FOUP handling and SECS/GEM communication protocols inside assembly and testing cleanrooms requires years of hard-won field qualification. Emerging challengers struggle replicating this factory-level trust, often building superior imaging hardware that foundries reject simply because factory interface software lacks proven stability under continuous 24/7 operating loads.

Mega-foundries exercise immense leverage by standardizing inspection protocols across all global sites simultaneously. Procurement directors consolidate purchases to two prime vendors, forcing suppliers into brutal price and capability wars. Manufacturers failing to secure positions within primary TSMC or Intel qualification cycles must pivot entirely, targeting specialized automotive or power-packaging niches where throughput demands yield to unique penetration requirements.

Key Players in Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market

- Comet Yxlon

- Nordson Test & Inspection

- Nikon Corporation

- Carl Zeiss Microscopy

- Waygate Technologies

- ViTrox Corporation Berhad

- Hitachi High-Tech Corporation

Scope of the Report

| Metric | Value |

|---|---|

| Quantitative Units | USD 0.44 billion to USD 1.32 billion, at a CAGR of 11.60% |

| Market Definition | Nondestructive volumetric imaging equipment designed specifically for resolving internal structural defects inside stacked semiconductor packages. Equipment maps solder micro-bumps, through-silicon vias, and wire bonds across multiple z-axis layers without physical cross-sectioning. |

| Segmentation | Inspection Mode, Package Type, Automation Level, Resolution Class, Buyer Type, and Region |

| Regions Covered | North America, Latin America, Western Europe, Eastern Europe, Asia Pacific, Middle East and Africa |

| Countries Covered | Taiwan, South Korea, China, Malaysia, United States, Japan, Germany |

| Key Companies Profiled | Comet Yxlon, Nordson Test & Inspection, Nikon Corporation, Carl Zeiss Microscopy, Waygate Technologies, ViTrox Corporation Berhad, Hitachi High-Tech Corporation |

| Forecast Period | 2026 to 2036 |

| Approach | Cleanroom footprint expansion data and specific TSV pitch reduction timelines. |

Source: Future Market Insights (FMI) analysis, based on proprietary forecasting model and primary research

Heterogeneous Integration and Advanced Packaging X-Ray CT Inspection Systems Market Analysis by Segments

Inspection Mode:

- 3D CT

- 2D X-ray

- Laminography

Package Type:

- HBM stacks

- 2.5D interposers

- 3D ICs

- Fan-out

- Chiplets

Automation Level:

- Inline

- Nearline

- Offline lab

Resolution Class:

- Submicron

- 1 to 3 µm

- Above 3 µm

Buyer Type:

- OSATs

- Foundries

- IDMs

- R&D labs

Region:

- North America

- United States

- Canada

- Europe

- Germany

- United Kingdom

- France

- Italy

- Spain

- Asia Pacific

- China

- Japan

- South Korea

- Taiwan

- Singapore

- Latin America

- Brazil

- Mexico

- Argentina

- Middle East & Africa

- GCC Countries

- South Africa

Bibliography

- SEMI. (2025, July 22). SEMI reports global total semiconductor equipment sales forecast to reach 125.5 billion dollars in 2025.

- Taiwan Semiconductor Manufacturing Company. (2025, March). TSMC annual report 2024.

- ViTrox Corporation Berhad. (2025). Annual report 2024.

- International Roadmap for Devices and Systems. (2024). 2024 IRDS executive packaging tutorial-part 1.

- Villarraga-Gómez, H., Wu, T., De Carlo, F., & Foster, I. (2024). Assessing electronics with advanced 3D X-ray imaging workflows enabled by deep learning. Journal of Materials Engineering and Performance.

- International Microelectronics Assembly and Packaging Society. (2025). Design guidelines for in-line X-ray inspection in advanced packaging technology: A CoWoS case study.

This bibliography is provided for reader reference. The full FMI report contains the complete reference list with primary source documentation.

Frequently Asked Questions

What is the market size of heterogeneous integration and advanced packaging X-ray CT inspection systems?

Demand valuation reached USD 0.39 billion in 2025. Revenue expands to USD 0.44 billion in 2026, advancing to USD 1.32 billion by 2036. Consistent 11.60% compound annual growth reflects strict quality control mandates enforced across mega-foundries building advanced chiplet architectures.

Why is CT inspection becoming more important in advanced semiconductor packaging?

Stacking multiple active silicon layers vertically completely obscures critical interconnects in standard planar views. Computed tomography separates these planes mathematically. Yield architects utilize this z-axis visibility to isolate micro-bumps and hidden non-wets that traditional transmission imaging inherently masks.

Which package types need X-ray CT inspection most?

High-bandwidth memory stacks command maximum inspection priority due to severe thermal stress vulnerabilities. Stacking twelve memory dies introduces unprecedented physical warping during reflow, frequently causing intermittent interconnect failures. Memory engineers treat complete volumetric inspection as mandatory to intercept hidden defects early.

How do HBM and chiplet designs affect inspection equipment demand?

Extreme interconnect density multiplies financial risk per unit. Escaping a single void destroys thousands of dollars in known-good dies. Yield logic dictates that testing small batches mathematically misses isolated errors, forcing quality directors to pivot toward 100% inline volumetric inspection to guarantee multi-die functionality.

Who are the leading suppliers of advanced packaging X-ray CT systems?

Comet Yxlon, Carl Zeiss Microscopy, Waygate Technologies, and Nordson Test & Inspection operate as primary competitors. Mega-foundries exercise immense leverage by standardizing inspection protocols across global sites, forcing suppliers into brutal capability wars focused specifically on AI-accelerated reconstruction speed and factory interface stability.

What is the difference between 2D X-ray, laminography, and CT in packaging inspection?

Standard 2D imaging projects overlapping features onto single planes, missing stacked defects entirely. Laminography achieves partial depth resolution through angled cross-sections but lacks full volumetric accuracy. True CT reconstructs complete 3D voxel models, granting engineers absolute submicron z-axis visibility necessary for dense silicon verification.

Why are OSATs and foundries increasing spending on package inspection?

Fabless designers transfer financial liability for packaging failures directly to assembly partners. Operations directors utilize volumetric scans defensively, proving defects existed within incoming silicon rather than resulting from assembly processes. This dynamic forces assemblers to over-invest in high-end hardware for warranty protection.

Which regions are growing fastest for advanced packaging inspection tools?

Taiwan leads deployment driven by massive TSMC capacity expansions requiring mandatory inline gatekeepers. South Korea tracks closely as memory manufacturers standardize qualification protocols for vertical stacks. China accelerates domestic chiplet ecosystems, utilizing CT platforms to stitch together diverse silicon sources independently.

How does AI improve defect recognition in X-ray CT workflows?

Software engineers deploy AI to predict complete volumetric structures from intentionally sparse scan data. This approach dramatically reduces physical exposure time and data processing latency. Factory managers utilize predictive algorithms to push CT closer to true inline factory takt speeds.

What are the main limitations of inline CT adoption in semiconductor packaging?

Mathematical reconstruction of submicron voxel data creates massive computational bottlenecks. Processing terabytes of imaging data currently takes minutes, whereas factory takt times demand seconds. Cleanroom administrators struggle aligning massive data processing pipelines with physical wafer transport capabilities.

Which defects can CT detect in semiconductor packaging?

Volumetric scanning precisely identifies micro-voids, solder bridging, head-in-pillow non-wets, TSV misalignment, and microscopic via cracking. Engineers trace these topographical variations back to specific front-end deposition anomalies, preventing upstream fabrication errors from destroying subsequent packaged assemblies.

Why is CT inspection needed for HBM packages?

Stacking twelve memory dies requires thousands of micro-bumps per layer, generating unprecedented stress during reflow processes. Electrical opens often disguise themselves as thermal-induced intermittent failures later. CT scanning provides root-cause geometry data immediately, preventing catastrophic scrap events.

Can x-ray CT inspect hybrid bonding defects?

Yes, submicron platforms resolve critical alignment deviations inside hybrid bonded copper-to-copper interfaces. Quality engineers utilize precise z-axis data to detect microscopic particulate inclusions and bonding voids that compromise structural integrity and electrical conductivity in dense 3D IC architectures.

What is heterogeneous integration inspection?

It involves verifying structural integrity inside packages containing multiple diverse silicon components (logic, memory, sensors) stitched together. Equipment must map complex solder micro-bumps, through-silicon vias, and wire bonds across multiple layers without physically cross-sectioning the expensive final product.

What is the fastest-growing region for advanced packaging x-ray CT systems?

Taiwan exhibits the fastest structural growth trajectory at 13.1% CAGR. Unmatched concentration of advanced capacity dictates extreme inline metrology requirements. Facility directors deploy scanners strictly as mandatory gatekeepers for complex interposer volumes entering the global supply chain.

Explain the market for x-ray CT inspection in heterogeneous integration?

Yield economics govern tool adoption. Delaying volumetric implementation forces assembly houses to absorb massive scrap costs. Implementing submicron CT scanning provides immediate process feedback, allowing technicians to halt drifting bonders before ruining subsequent expensive silicon batches destined for AI accelerators.

Which companies lead advanced packaging CT inspection systems?

Market leadership hinges on image reconstruction speed. Comet Yxlon, Nikon Corporation, and ViTrox Corporation Berhad focus massive R&D budgets on sparse-data algorithms. Competitors offering brilliant resolution but slow analysis find themselves permanently relegated to offline failure analysis labs.

Why are HBM and chiplets increasing CT inspection demand?

Flip-chip geometries conceal connections entirely beneath silicon dies, nullifying standard optical capabilities. Assembly managers upgrade specifically to secure lucrative contracts for advanced architectures. Facilities failing to modernize remain permanently locked into low-margin legacy wire-bond business.

Compare inline and offline CT inspection for semiconductor packaging?

Offline configurations bypass active factory floor vibration, allowing maximum theoretical imaging resolution but introducing manual handling risks. Inline systems sacrifice marginal clarity for logistical safety, utilizing automated FOUP handlers to scan wafers seamlessly without breaking cleanroom vacuum environments.

When should OSATs adopt inline CT inspection?

Adoption becomes mandatory when scrap costs exceed equipment depreciation. Assembly houses trying to minimize inspection capital absorb massive losses when they cannot prove substrate flaws pre-existed their intervention. Inline deployment transforms post-mortem failure analysis into active yield rescue.

How does x-ray CT differ from 2D x-ray in package inspection?

Planar 2D transmission inherently masks hidden non-wets located between stacked active layers. Computed tomography separates z-axis layers mathematically, revealing critical solder bump defects and TSV misalignments that quality control directors at Tier-1 foundries must intercept before final overmolding.

What are the inspection bottlenecks in HBM package production?

A single complete 300mm wafer scan generates immense voxel file sizes. Cleanroom IT networks buckle under continuous data transfer loads. Administrators must architect dedicated high-speed storage pipelines before factory directors can utilize scanners at maximum capability without halting production.

How do foundries trace failures back to fabrication?

Packaging defects often originate from subtle topographical variations on incoming silicon itself. Process engineers map volumetric packaging data back to specific front-end deposition anomalies. This feed-forward loop prevents upstream fabrication errors from propagating into expensive assembly workflows.

Why is statistical sampling failing for advanced node packages?

Dense integration concentrates immense value into single units where solitary micro-voids cause total device failure. Testing a small batch mathematically guarantees missing isolated errors. Quality directors implement 100% inline volumetric scanning to assure fabless clients of multi-die functionality.

Table of Content

- Executive Summary

- Global Market Outlook

- Demand to side Trends

- Supply to side Trends

- Technology Roadmap Analysis

- Analysis and Recommendations

- Market Overview

- Market Coverage / Taxonomy

- Market Definition / Scope / Limitations

- Research Methodology

- Chapter Orientation

- Analytical Lens and Working Hypotheses

- Market Structure, Signals, and Trend Drivers

- Benchmarking and Cross-market Comparability

- Market Sizing, Forecasting, and Opportunity Mapping

- Research Design and Evidence Framework

- Desk Research Programme (Secondary Evidence)

- Company Annual and Sustainability Reports

- Peer-reviewed Journals and Academic Literature

- Corporate Websites, Product Literature, and Technical Notes

- Earnings Decks and Investor Briefings

- Statutory Filings and Regulatory Disclosures

- Technical White Papers and Standards Notes

- Trade Journals, Industry Magazines, and Analyst Briefs

- Conference Proceedings, Webinars, and Seminar Materials

- Government Statistics Portals and Public Data Releases

- Press Releases and Reputable Media Coverage

- Specialist Newsletters and Curated Briefings

- Sector Databases and Reference Repositories

- FMI Internal Proprietary Databases and Historical Market Datasets

- Subscription Datasets and Paid Sources

- Social Channels, Communities, and Digital Listening Inputs

- Additional Desk Sources

- Expert Input and Fieldwork (Primary Evidence)

- Primary Modes

- Qualitative Interviews and Expert Elicitation

- Quantitative Surveys and Structured Data Capture

- Blended Approach

- Why Primary Evidence is Used

- Field Techniques

- Interviews

- Surveys

- Focus Groups

- Observational and In-context Research

- Social and Community Interactions

- Stakeholder Universe Engaged

- C-suite Leaders

- Board Members

- Presidents and Vice Presidents

- R&D and Innovation Heads

- Technical Specialists

- Domain Subject-matter Experts

- Scientists

- Physicians and Other Healthcare Professionals

- Governance, Ethics, and Data Stewardship

- Research Ethics

- Data Integrity and Handling

- Primary Modes

- Tooling, Models, and Reference Databases

- Desk Research Programme (Secondary Evidence)

- Data Engineering and Model Build

- Data Acquisition and Ingestion

- Cleaning, Normalisation, and Verification

- Synthesis, Triangulation, and Analysis

- Quality Assurance and Audit Trail

- Market Background

- Market Dynamics

- Drivers

- Restraints

- Opportunity

- Trends

- Scenario Forecast

- Demand in Optimistic Scenario

- Demand in Likely Scenario

- Demand in Conservative Scenario

- Opportunity Map Analysis

- Product Life Cycle Analysis

- Supply Chain Analysis

- Investment Feasibility Matrix

- Value Chain Analysis

- PESTLE and Porter’s Analysis

- Regulatory Landscape

- Regional Parent Market Outlook

- Production and Consumption Statistics

- Import and Export Statistics

- Market Dynamics

- Global Market Analysis 2021 to 2025 and Forecast, 2026 to 2036

- Historical Market Size Value (USD Million) Analysis, 2021 to 2025

- Current and Future Market Size Value (USD Million) Projections, 2026 to 2036

- Y to o to Y Growth Trend Analysis

- Absolute $ Opportunity Analysis

- Global Market Pricing Analysis 2021 to 2025 and Forecast 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Inspection Mode

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Inspection Mode , 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Inspection Mode , 2026 to 2036

- 3D CT

- 2D X-ray

- Laminography

- 3D CT

- Y to o to Y Growth Trend Analysis By Inspection Mode , 2021 to 2025

- Absolute $ Opportunity Analysis By Inspection Mode , 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Package Type

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Package Type, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Package Type, 2026 to 2036

- HBM stacks

- 2.5D interposers

- 3D ICs

- Fan-out

- Chiplets

- HBM stacks

- Y to o to Y Growth Trend Analysis By Package Type, 2021 to 2025

- Absolute $ Opportunity Analysis By Package Type, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Automation Level

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Automation Level, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Automation Level, 2026 to 2036

- Inline

- Nearline

- Offline lab

- Inline

- Y to o to Y Growth Trend Analysis By Automation Level, 2021 to 2025

- Absolute $ Opportunity Analysis By Automation Level, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Resolution Class

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Resolution Class, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Resolution Class, 2026 to 2036

- Submicron

- 1 to 3 µm

- Above 3 µm

- Submicron

- Y to o to Y Growth Trend Analysis By Resolution Class, 2021 to 2025

- Absolute $ Opportunity Analysis By Resolution Class, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Buyer Type

- Introduction / Key Findings

- Historical Market Size Value (USD Million) Analysis By Buyer Type, 2021 to 2025

- Current and Future Market Size Value (USD Million) Analysis and Forecast By Buyer Type, 2026 to 2036

- OSATs

- Foundries

- IDMs

- R&D labs

- OSATs

- Y to o to Y Growth Trend Analysis By Buyer Type, 2021 to 2025

- Absolute $ Opportunity Analysis By Buyer Type, 2026 to 2036

- Global Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Region

- Introduction

- Historical Market Size Value (USD Million) Analysis By Region, 2021 to 2025

- Current Market Size Value (USD Million) Analysis and Forecast By Region, 2026 to 2036

- North America

- Latin America

- Western Europe

- Eastern Europe

- East Asia

- South Asia and Pacific

- Middle East & Africa

- Market Attractiveness Analysis By Region

- North America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- USA

- Canada

- Mexico

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Key Takeaways

- Latin America Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Brazil

- Chile

- Rest of Latin America

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Key Takeaways

- Western Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Germany

- UK

- Italy

- Spain

- France

- Nordic

- BENELUX

- Rest of Western Europe

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Key Takeaways

- Eastern Europe Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Russia

- Poland

- Hungary

- Balkan & Baltic

- Rest of Eastern Europe

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Key Takeaways

- East Asia Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- China

- Japan

- South Korea

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Key Takeaways

- South Asia and Pacific Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- India

- ASEAN

- Australia & New Zealand

- Rest of South Asia and Pacific

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Key Takeaways

- Middle East & Africa Market Analysis 2021 to 2025 and Forecast 2026 to 2036, By Country

- Historical Market Size Value (USD Million) Trend Analysis By Market Taxonomy, 2021 to 2025

- Market Size Value (USD Million) Forecast By Market Taxonomy, 2026 to 2036

- By Country

- Kingdom of Saudi Arabia

- Other GCC Countries

- Turkiye

- South Africa

- Other African Union

- Rest of Middle East & Africa

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- By Country

- Market Attractiveness Analysis

- By Country

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Key Takeaways

- Key Countries Market Analysis

- USA

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Canada

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Mexico

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Brazil

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Chile

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Germany

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- UK

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Italy

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Spain

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- France

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- India

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- ASEAN

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Australia & New Zealand

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- China

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Japan

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- South Korea

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Russia

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Poland

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Hungary

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Kingdom of Saudi Arabia

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Turkiye

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- South Africa

- Pricing Analysis

- Market Share Analysis, 2025

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- USA

- Market Structure Analysis

- Competition Dashboard

- Competition Benchmarking

- Market Share Analysis of Top Players

- By Regional

- By Inspection Mode

- By Package Type

- By Automation Level

- By Resolution Class

- By Buyer Type

- Competition Analysis

- Competition Deep Dive

- Comet Yxlon

- Overview

- Product Portfolio

- Profitability by Market Segments (Product/Age /Sales Channel/Region)

- Sales Footprint

- Strategy Overview

- Marketing Strategy

- Product Strategy

- Channel Strategy

- Nordson Test & Inspection

- Nikon Corporation

- Carl Zeiss Microscopy

- Waygate Technologies

- ViTrox Corporation Berhad

- Hitachi High-Tech Corporation

- Comet Yxlon

- Competition Deep Dive

- Assumptions & Acronyms Used

List of Tables

- Table 1: Global Market Value (USD Million) Forecast by Region, 2021 to 2036

- Table 2: Global Market Value (USD Million) Forecast by Inspection Mode , 2021 to 2036

- Table 3: Global Market Value (USD Million) Forecast by Package Type, 2021 to 2036

- Table 4: Global Market Value (USD Million) Forecast by Automation Level, 2021 to 2036

- Table 5: Global Market Value (USD Million) Forecast by Resolution Class, 2021 to 2036

- Table 6: Global Market Value (USD Million) Forecast by Buyer Type, 2021 to 2036

- Table 7: North America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 8: North America Market Value (USD Million) Forecast by Inspection Mode , 2021 to 2036

- Table 9: North America Market Value (USD Million) Forecast by Package Type, 2021 to 2036

- Table 10: North America Market Value (USD Million) Forecast by Automation Level, 2021 to 2036

- Table 11: North America Market Value (USD Million) Forecast by Resolution Class, 2021 to 2036

- Table 12: North America Market Value (USD Million) Forecast by Buyer Type, 2021 to 2036

- Table 13: Latin America Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 14: Latin America Market Value (USD Million) Forecast by Inspection Mode , 2021 to 2036

- Table 15: Latin America Market Value (USD Million) Forecast by Package Type, 2021 to 2036

- Table 16: Latin America Market Value (USD Million) Forecast by Automation Level, 2021 to 2036

- Table 17: Latin America Market Value (USD Million) Forecast by Resolution Class, 2021 to 2036

- Table 18: Latin America Market Value (USD Million) Forecast by Buyer Type, 2021 to 2036

- Table 19: Western Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 20: Western Europe Market Value (USD Million) Forecast by Inspection Mode , 2021 to 2036

- Table 21: Western Europe Market Value (USD Million) Forecast by Package Type, 2021 to 2036

- Table 22: Western Europe Market Value (USD Million) Forecast by Automation Level, 2021 to 2036

- Table 23: Western Europe Market Value (USD Million) Forecast by Resolution Class, 2021 to 2036

- Table 24: Western Europe Market Value (USD Million) Forecast by Buyer Type, 2021 to 2036

- Table 25: Eastern Europe Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 26: Eastern Europe Market Value (USD Million) Forecast by Inspection Mode , 2021 to 2036

- Table 27: Eastern Europe Market Value (USD Million) Forecast by Package Type, 2021 to 2036

- Table 28: Eastern Europe Market Value (USD Million) Forecast by Automation Level, 2021 to 2036

- Table 29: Eastern Europe Market Value (USD Million) Forecast by Resolution Class, 2021 to 2036

- Table 30: Eastern Europe Market Value (USD Million) Forecast by Buyer Type, 2021 to 2036

- Table 31: East Asia Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 32: East Asia Market Value (USD Million) Forecast by Inspection Mode , 2021 to 2036

- Table 33: East Asia Market Value (USD Million) Forecast by Package Type, 2021 to 2036

- Table 34: East Asia Market Value (USD Million) Forecast by Automation Level, 2021 to 2036

- Table 35: East Asia Market Value (USD Million) Forecast by Resolution Class, 2021 to 2036

- Table 36: East Asia Market Value (USD Million) Forecast by Buyer Type, 2021 to 2036

- Table 37: South Asia and Pacific Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 38: South Asia and Pacific Market Value (USD Million) Forecast by Inspection Mode , 2021 to 2036

- Table 39: South Asia and Pacific Market Value (USD Million) Forecast by Package Type, 2021 to 2036

- Table 40: South Asia and Pacific Market Value (USD Million) Forecast by Automation Level, 2021 to 2036

- Table 41: South Asia and Pacific Market Value (USD Million) Forecast by Resolution Class, 2021 to 2036

- Table 42: South Asia and Pacific Market Value (USD Million) Forecast by Buyer Type, 2021 to 2036

- Table 43: Middle East & Africa Market Value (USD Million) Forecast by Country, 2021 to 2036

- Table 44: Middle East & Africa Market Value (USD Million) Forecast by Inspection Mode , 2021 to 2036

- Table 45: Middle East & Africa Market Value (USD Million) Forecast by Package Type, 2021 to 2036

- Table 46: Middle East & Africa Market Value (USD Million) Forecast by Automation Level, 2021 to 2036

- Table 47: Middle East & Africa Market Value (USD Million) Forecast by Resolution Class, 2021 to 2036

- Table 48: Middle East & Africa Market Value (USD Million) Forecast by Buyer Type, 2021 to 2036

List of Figures

- Figure 1: Global Market Pricing Analysis

- Figure 2: Global Market Value (USD Million) Forecast 2021-2036

- Figure 3: Global Market Value Share and BPS Analysis by Inspection Mode , 2026 and 2036

- Figure 4: Global Market Y-o-Y Growth Comparison by Inspection Mode , 2026-2036

- Figure 5: Global Market Attractiveness Analysis by Inspection Mode

- Figure 6: Global Market Value Share and BPS Analysis by Package Type, 2026 and 2036

- Figure 7: Global Market Y-o-Y Growth Comparison by Package Type, 2026-2036

- Figure 8: Global Market Attractiveness Analysis by Package Type

- Figure 9: Global Market Value Share and BPS Analysis by Automation Level, 2026 and 2036

- Figure 10: Global Market Y-o-Y Growth Comparison by Automation Level, 2026-2036

- Figure 11: Global Market Attractiveness Analysis by Automation Level

- Figure 12: Global Market Value Share and BPS Analysis by Resolution Class, 2026 and 2036

- Figure 13: Global Market Y-o-Y Growth Comparison by Resolution Class, 2026-2036

- Figure 14: Global Market Attractiveness Analysis by Resolution Class

- Figure 15: Global Market Value Share and BPS Analysis by Buyer Type, 2026 and 2036

- Figure 16: Global Market Y-o-Y Growth Comparison by Buyer Type, 2026-2036

- Figure 17: Global Market Attractiveness Analysis by Buyer Type

- Figure 18: Global Market Value (USD Million) Share and BPS Analysis by Region, 2026 and 2036

- Figure 19: Global Market Y-o-Y Growth Comparison by Region, 2026-2036

- Figure 20: Global Market Attractiveness Analysis by Region

- Figure 21: North America Market Incremental Dollar Opportunity, 2026-2036

- Figure 22: Latin America Market Incremental Dollar Opportunity, 2026-2036

- Figure 23: Western Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 24: Eastern Europe Market Incremental Dollar Opportunity, 2026-2036

- Figure 25: East Asia Market Incremental Dollar Opportunity, 2026-2036

- Figure 26: South Asia and Pacific Market Incremental Dollar Opportunity, 2026-2036

- Figure 27: Middle East & Africa Market Incremental Dollar Opportunity, 2026-2036

- Figure 28: North America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 29: North America Market Value Share and BPS Analysis by Inspection Mode , 2026 and 2036

- Figure 30: North America Market Y-o-Y Growth Comparison by Inspection Mode , 2026-2036

- Figure 31: North America Market Attractiveness Analysis by Inspection Mode

- Figure 32: North America Market Value Share and BPS Analysis by Package Type, 2026 and 2036

- Figure 33: North America Market Y-o-Y Growth Comparison by Package Type, 2026-2036

- Figure 34: North America Market Attractiveness Analysis by Package Type

- Figure 35: North America Market Value Share and BPS Analysis by Automation Level, 2026 and 2036

- Figure 36: North America Market Y-o-Y Growth Comparison by Automation Level, 2026-2036

- Figure 37: North America Market Attractiveness Analysis by Automation Level

- Figure 38: North America Market Value Share and BPS Analysis by Resolution Class, 2026 and 2036

- Figure 39: North America Market Y-o-Y Growth Comparison by Resolution Class, 2026-2036

- Figure 40: North America Market Attractiveness Analysis by Resolution Class

- Figure 41: North America Market Value Share and BPS Analysis by Buyer Type, 2026 and 2036

- Figure 42: North America Market Y-o-Y Growth Comparison by Buyer Type, 2026-2036

- Figure 43: North America Market Attractiveness Analysis by Buyer Type

- Figure 44: Latin America Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 45: Latin America Market Value Share and BPS Analysis by Inspection Mode , 2026 and 2036

- Figure 46: Latin America Market Y-o-Y Growth Comparison by Inspection Mode , 2026-2036

- Figure 47: Latin America Market Attractiveness Analysis by Inspection Mode

- Figure 48: Latin America Market Value Share and BPS Analysis by Package Type, 2026 and 2036

- Figure 49: Latin America Market Y-o-Y Growth Comparison by Package Type, 2026-2036

- Figure 50: Latin America Market Attractiveness Analysis by Package Type

- Figure 51: Latin America Market Value Share and BPS Analysis by Automation Level, 2026 and 2036

- Figure 52: Latin America Market Y-o-Y Growth Comparison by Automation Level, 2026-2036

- Figure 53: Latin America Market Attractiveness Analysis by Automation Level

- Figure 54: Latin America Market Value Share and BPS Analysis by Resolution Class, 2026 and 2036

- Figure 55: Latin America Market Y-o-Y Growth Comparison by Resolution Class, 2026-2036

- Figure 56: Latin America Market Attractiveness Analysis by Resolution Class

- Figure 57: Latin America Market Value Share and BPS Analysis by Buyer Type, 2026 and 2036

- Figure 58: Latin America Market Y-o-Y Growth Comparison by Buyer Type, 2026-2036

- Figure 59: Latin America Market Attractiveness Analysis by Buyer Type

- Figure 60: Western Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 61: Western Europe Market Value Share and BPS Analysis by Inspection Mode , 2026 and 2036

- Figure 62: Western Europe Market Y-o-Y Growth Comparison by Inspection Mode , 2026-2036

- Figure 63: Western Europe Market Attractiveness Analysis by Inspection Mode

- Figure 64: Western Europe Market Value Share and BPS Analysis by Package Type, 2026 and 2036

- Figure 65: Western Europe Market Y-o-Y Growth Comparison by Package Type, 2026-2036

- Figure 66: Western Europe Market Attractiveness Analysis by Package Type

- Figure 67: Western Europe Market Value Share and BPS Analysis by Automation Level, 2026 and 2036

- Figure 68: Western Europe Market Y-o-Y Growth Comparison by Automation Level, 2026-2036

- Figure 69: Western Europe Market Attractiveness Analysis by Automation Level

- Figure 70: Western Europe Market Value Share and BPS Analysis by Resolution Class, 2026 and 2036

- Figure 71: Western Europe Market Y-o-Y Growth Comparison by Resolution Class, 2026-2036

- Figure 72: Western Europe Market Attractiveness Analysis by Resolution Class

- Figure 73: Western Europe Market Value Share and BPS Analysis by Buyer Type, 2026 and 2036

- Figure 74: Western Europe Market Y-o-Y Growth Comparison by Buyer Type, 2026-2036

- Figure 75: Western Europe Market Attractiveness Analysis by Buyer Type

- Figure 76: Eastern Europe Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 77: Eastern Europe Market Value Share and BPS Analysis by Inspection Mode , 2026 and 2036

- Figure 78: Eastern Europe Market Y-o-Y Growth Comparison by Inspection Mode , 2026-2036

- Figure 79: Eastern Europe Market Attractiveness Analysis by Inspection Mode

- Figure 80: Eastern Europe Market Value Share and BPS Analysis by Package Type, 2026 and 2036

- Figure 81: Eastern Europe Market Y-o-Y Growth Comparison by Package Type, 2026-2036

- Figure 82: Eastern Europe Market Attractiveness Analysis by Package Type

- Figure 83: Eastern Europe Market Value Share and BPS Analysis by Automation Level, 2026 and 2036

- Figure 84: Eastern Europe Market Y-o-Y Growth Comparison by Automation Level, 2026-2036

- Figure 85: Eastern Europe Market Attractiveness Analysis by Automation Level

- Figure 86: Eastern Europe Market Value Share and BPS Analysis by Resolution Class, 2026 and 2036

- Figure 87: Eastern Europe Market Y-o-Y Growth Comparison by Resolution Class, 2026-2036

- Figure 88: Eastern Europe Market Attractiveness Analysis by Resolution Class

- Figure 89: Eastern Europe Market Value Share and BPS Analysis by Buyer Type, 2026 and 2036

- Figure 90: Eastern Europe Market Y-o-Y Growth Comparison by Buyer Type, 2026-2036

- Figure 91: Eastern Europe Market Attractiveness Analysis by Buyer Type

- Figure 92: East Asia Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 93: East Asia Market Value Share and BPS Analysis by Inspection Mode , 2026 and 2036

- Figure 94: East Asia Market Y-o-Y Growth Comparison by Inspection Mode , 2026-2036

- Figure 95: East Asia Market Attractiveness Analysis by Inspection Mode

- Figure 96: East Asia Market Value Share and BPS Analysis by Package Type, 2026 and 2036

- Figure 97: East Asia Market Y-o-Y Growth Comparison by Package Type, 2026-2036

- Figure 98: East Asia Market Attractiveness Analysis by Package Type

- Figure 99: East Asia Market Value Share and BPS Analysis by Automation Level, 2026 and 2036

- Figure 100: East Asia Market Y-o-Y Growth Comparison by Automation Level, 2026-2036

- Figure 101: East Asia Market Attractiveness Analysis by Automation Level

- Figure 102: East Asia Market Value Share and BPS Analysis by Resolution Class, 2026 and 2036

- Figure 103: East Asia Market Y-o-Y Growth Comparison by Resolution Class, 2026-2036

- Figure 104: East Asia Market Attractiveness Analysis by Resolution Class

- Figure 105: East Asia Market Value Share and BPS Analysis by Buyer Type, 2026 and 2036

- Figure 106: East Asia Market Y-o-Y Growth Comparison by Buyer Type, 2026-2036

- Figure 107: East Asia Market Attractiveness Analysis by Buyer Type

- Figure 108: South Asia and Pacific Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 109: South Asia and Pacific Market Value Share and BPS Analysis by Inspection Mode , 2026 and 2036

- Figure 110: South Asia and Pacific Market Y-o-Y Growth Comparison by Inspection Mode , 2026-2036

- Figure 111: South Asia and Pacific Market Attractiveness Analysis by Inspection Mode

- Figure 112: South Asia and Pacific Market Value Share and BPS Analysis by Package Type, 2026 and 2036

- Figure 113: South Asia and Pacific Market Y-o-Y Growth Comparison by Package Type, 2026-2036

- Figure 114: South Asia and Pacific Market Attractiveness Analysis by Package Type

- Figure 115: South Asia and Pacific Market Value Share and BPS Analysis by Automation Level, 2026 and 2036

- Figure 116: South Asia and Pacific Market Y-o-Y Growth Comparison by Automation Level, 2026-2036

- Figure 117: South Asia and Pacific Market Attractiveness Analysis by Automation Level

- Figure 118: South Asia and Pacific Market Value Share and BPS Analysis by Resolution Class, 2026 and 2036

- Figure 119: South Asia and Pacific Market Y-o-Y Growth Comparison by Resolution Class, 2026-2036

- Figure 120: South Asia and Pacific Market Attractiveness Analysis by Resolution Class

- Figure 121: South Asia and Pacific Market Value Share and BPS Analysis by Buyer Type, 2026 and 2036

- Figure 122: South Asia and Pacific Market Y-o-Y Growth Comparison by Buyer Type, 2026-2036

- Figure 123: South Asia and Pacific Market Attractiveness Analysis by Buyer Type

- Figure 124: Middle East & Africa Market Value Share and BPS Analysis by Country, 2026 and 2036

- Figure 125: Middle East & Africa Market Value Share and BPS Analysis by Inspection Mode , 2026 and 2036

- Figure 126: Middle East & Africa Market Y-o-Y Growth Comparison by Inspection Mode , 2026-2036

- Figure 127: Middle East & Africa Market Attractiveness Analysis by Inspection Mode

- Figure 128: Middle East & Africa Market Value Share and BPS Analysis by Package Type, 2026 and 2036

- Figure 129: Middle East & Africa Market Y-o-Y Growth Comparison by Package Type, 2026-2036

- Figure 130: Middle East & Africa Market Attractiveness Analysis by Package Type

- Figure 131: Middle East & Africa Market Value Share and BPS Analysis by Automation Level, 2026 and 2036

- Figure 132: Middle East & Africa Market Y-o-Y Growth Comparison by Automation Level, 2026-2036

- Figure 133: Middle East & Africa Market Attractiveness Analysis by Automation Level

- Figure 134: Middle East & Africa Market Value Share and BPS Analysis by Resolution Class, 2026 and 2036

- Figure 135: Middle East & Africa Market Y-o-Y Growth Comparison by Resolution Class, 2026-2036

- Figure 136: Middle East & Africa Market Attractiveness Analysis by Resolution Class

- Figure 137: Middle East & Africa Market Value Share and BPS Analysis by Buyer Type, 2026 and 2036

- Figure 138: Middle East & Africa Market Y-o-Y Growth Comparison by Buyer Type, 2026-2036

- Figure 139: Middle East & Africa Market Attractiveness Analysis by Buyer Type

- Figure 140: Global Market - Tier Structure Analysis

- Figure 141: Global Market - Company Share Analysis

Full Research Suite comprises of:

Market outlook & trends analysis

Interviews & case studies

Strategic recommendations

Vendor profiles & capabilities analysis

5-year forecasts

8 regions and 60+ country-level data splits

Market segment data splits

12 months of continuous data updates

DELIVERED AS:

PDF EXCEL ONLINE